# 16Mb (512K x 36 & 1M x 18) SRAM

#### **Features**

- 512K x 36 or 1M x 18 organization

- · CMOS technology

- Double-data-rate and single-data-rate synchronous modes of operation

- · Pipeline mode of operation

- · Burst mode of operation

- · Self-timed late write with full data coherency

- Single differential high-speed transceiver logic (HSTL) clock with HSTL input and output levels

- 2.5V power supply, 1.5 V<sub>DDQ</sub>

- Registered addresses, controls, and data-ins

- Common I/O

- · Asynchronous output enable

- Boundary scan using a limited set of JTAG 1149.1 functions

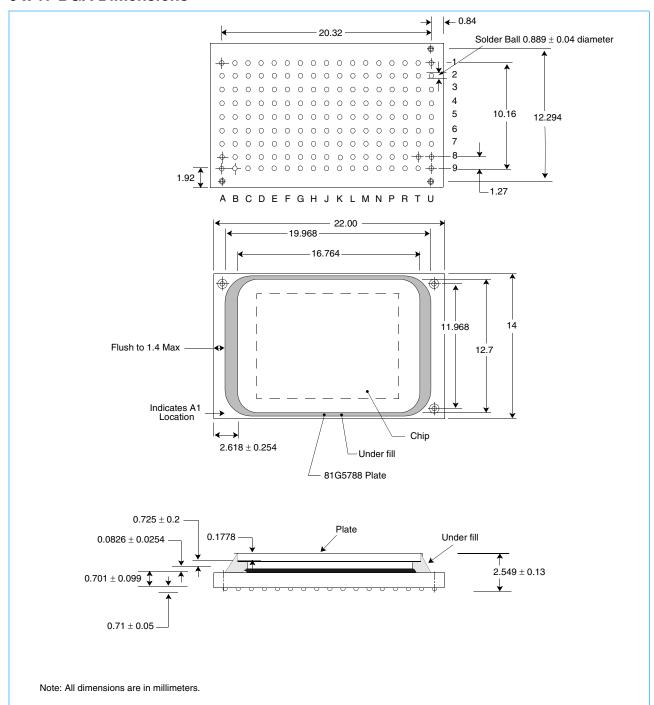

- 9 x 17 bump ball grid array package with SRAM JEDEC standard pinout and boundary SCAN order

- · Programmable impedance output driver

### **Description**

The IBM043616CXLBC and IBM041816CXLBC 16Mb SRAMs are double-data-rate (DDR) pipeline mode, high-performance CMOS static random-access memories that have wide I/O and offer cycle times as low as 2.5ns. Single differential CK clocks are used to initialize the read/write operation, and all internal operations are self-timed. In DDR mode, every rising edge of the CK clock addresses and controls are registered internally. Data-ins are regis-

tered on rising and falling edges of the CK clock. Data-outs are updated from output registers on the next rising and falling edges of the CK clock, hence the double data rate. Internal write buffers allow write data to follow one cycle after addresses and controls. The SRAM is operated with a single 2.5V power supply and is compatible with HSTL I/O interfaces.

## x36 BGA Bump Layout (Top View)

|   | 1        | 2         | 3        | 4        | 5         | 6                 | 7               | 8                  | 9        |

|---|----------|-----------|----------|----------|-----------|-------------------|-----------------|--------------------|----------|

| Α | $V_{SS}$ | $V_{DDQ}$ | SA13     | SA11     | ZQ        | SA10              | SA8             | $V_{DDQ}$          | $V_{SS}$ |

| В | DQ23     | DQ20      | SA14     | $V_{SS}$ | B1        | $V_{SS}$          | SA7             | DQ15               | DQ12     |

| С | $V_{SS}$ | $V_{DDQ}$ | SA15     | SA12     | G         | SA9               | SA6             | $V_{\mathrm{DDQ}}$ | $V_{SS}$ |

| D | DQ24     | DQ21      | SA18     | $V_{SS}$ | $V_{DD}$  | $V_{SS}$          | SA5             | DQ14               | DQ11     |

| E | $V_{SS}$ | $V_{DDQ}$ | $V_{SS}$ | $V_{DD}$ | $V_{REF}$ | $V_{DD}$          | $V_{SS}$        | $V_{\mathrm{DDQ}}$ | $V_{SS}$ |

| F | DQ25     | CQ        | DQ18     | $V_{DD}$ | $V_{DD}$  | $V_{DD}$          | DQ17            | CQ                 | DQ10     |

| G | $V_{SS}$ | $V_{DDQ}$ | $V_{SS}$ | $V_{SS}$ | CK        | $V_{SS}$          | $V_{SS}$        | $V_{DDQ}$          | $V_{SS}$ |

| Н | DQ26     | DQ22      | DQ19     | $V_{DD}$ | CK        | $V_{DD}$          | DQ16            | DQ13               | DQ9      |

| J | $V_{SS}$ | $V_{DDQ}$ | $V_{SS}$ | $V_{DD}$ | $V_{DD}$  | $V_{DD}$          | $V_{SS}$        | $V_{\mathrm{DDQ}}$ | $V_{SS}$ |

| K | DQ27     | DQ31      | DQ34     | $V_{SS}$ | B2        | $V_{SS}$          | DQ1             | DQ4                | DQ8      |

| L | $V_{SS}$ | $V_{DDQ}$ | $V_{SS}$ | LBO      | ВЗ        | MODE <sup>1</sup> | $V_{SS}$        | $V_{DDQ}$          | $V_{SS}$ |

| M | DQ28     | CQ        | DQ35     | $V_{DD}$ | $V_{DD}$  | $V_{DD}$          | DQ0             | CQ                 | DQ7      |

| N | $V_{SS}$ | $V_{DDQ}$ | $V_{SS}$ | $V_{DD}$ | $V_{REF}$ | $V_{DD}$          | $V_{SS}$        | $V_{\mathrm{DDQ}}$ | $V_{SS}$ |

| Р | DQ29     | DQ32      | NC       | $V_{SS}$ | $V_{DD}$  | $V_{SS}$          | SA4             | DQ3                | DQ6      |

| R | $V_{SS}$ | $V_{DDQ}$ | $V_{DD}$ | SA17     | SA1       | SA2               | $V_{DD}$        | $V_{DDQ}$          | $V_{SS}$ |

| Т | DQ30     | DQ33      | SA16     | $V_{SS}$ | SA0       | $V_{SS}$          | SA3             | DQ2                | DQ5      |

| U | $V_{SS}$ | $V_{DDQ}$ | TMS      | TDI      | TCK       | TDO               | NC <sup>2</sup> | $V_{DDQ}$          | $V_{SS}$ |

<sup>1.</sup> The Mode pin must be connected to  $V_{SS}$  or floated. The Mode pin has a very small pull down, less than  $5\mu\text{A}$  current at

## x18 BGA Bump Layout (Top View)

|   | 1               | 2                  | 3        | 4        | 5         | 6                 | 7               | 8                  | 9               |

|---|-----------------|--------------------|----------|----------|-----------|-------------------|-----------------|--------------------|-----------------|

| Α | $V_{SS}$        | $V_{DDQ}$          | SA13     | SA11     | ZQ        | SA10              | SA8             | $V_{DDQ}$          | $V_{SS}$        |

| В | NC              | DQ10               | SA14     | $V_{SS}$ | B1        | $V_{SS}$          | SA7             | NC                 | DQ5             |

| С | $V_{SS}$        | $V_{DDQ}$          | SA15     | SA12     | G         | SA9               | SA6             | $V_{DDQ}$          | $V_{SS}$        |

| D | DQ11            | NC                 | SA18     | $V_{SS}$ | $V_{DD}$  | $V_{SS}$          | SA5             | DQ7                | NC              |

| E | $V_{SS}$        | $V_{DDQ}$          | $V_{SS}$ | $V_{DD}$ | $V_{REF}$ | $V_{DD}$          | $V_{SS}$        | $V_{DDQ}$          | $V_{SS}$        |

| F | NC              | CQ                 | NC       | $V_{DD}$ | $V_{DD}$  | $V_{DD}$          | DQ8             | NC                 | DQ4             |

| G | $V_{SS}$        | $V_{\mathrm{DDQ}}$ | $V_{SS}$ | $V_{SS}$ | CK        | $V_{SS}$          | $V_{SS}$        | $V_{\mathrm{DDQ}}$ | $V_{SS}$        |

| Н | DQ12            | NC                 | DQ9      | $V_{DD}$ | CK        | $V_{DD}$          | NC              | DQ6                | NC              |

| J | $V_{SS}$        | VDDQ               | $V_{SS}$ | $V_{DD}$ | $V_{DD}$  | $V_{DD}$          | $V_{SS}$        | $V_{DDQ}$          | $V_{SS}$        |

| Κ | NC              | DQ15               | NC       | $V_{SS}$ | B2        | $V_{SS}$          | DQ0             | NC                 | DQ3             |

| L | $V_{SS}$        | $V_{DDQ}$          | $V_{SS}$ | LBO      | В3        | MODE <sup>1</sup> | $V_{SS}$        | $V_{DDQ}$          | $V_{SS}$        |

| M | DQ13            | NC                 | DQ17     | $V_{DD}$ | $V_{DD}$  | $V_{DD}$          | NC              | CQ                 | NC              |

| N | $V_{SS}$        | $V_{DDQ}$          | $V_{SS}$ | $V_{DD}$ | $V_{REF}$ | $V_{DD}$          | $V_{SS}$        | $V_{DDQ}$          | $V_{SS}$        |

| Р | NC              | DQ16               | SA19     | $V_{SS}$ | $V_{DD}$  | $V_{SS}$          | SA4             | NC                 | DQ2             |

| R | $V_{SS}$        | $V_{DDQ}$          | $V_{DD}$ | SA17     | SA1       | SA2               | $V_{DD}$        | $V_{DDQ}$          | $V_{SS}$        |

| Т | DQ14            | NC                 | SA16     | $V_{SS}$ | SA0       | $V_{SS}$          | SA3             | DQ1                | NC              |

| U | V <sub>SS</sub> | $V_{DDQ}$          | TMS      | TDI      | TCK       | TDO               | NC <sup>2</sup> | $V_{\mathrm{DDQ}}$ | V <sub>SS</sub> |

<sup>1.</sup> The Mode pin must be connected to  $V_{SS}$ . The Mode pin has a very small pull down, less than  $5\mu A$  current at  $V_{DD}$  input. 2. ESD protection diodes reside on this NC bump

# **Pin Description**

| SA0-SA19            | Address Input (SA0–SA1 burst control starting addresses)                                       | TDO              | IEEE® 1149.1 Test Output (LVTTL level)           |

|---------------------|------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------|

| DQ0-DQ35            | Data I/O                                                                                       | G                | Asynchronous Output Enable                       |

| $CQ, \overline{CQ}$ | Differential Echo Clocks                                                                       | MODE             | Mode Pin. Must be connected to V <sub>SS</sub> . |

| CK, CK              | Differential Input Register Clocks                                                             | V <sub>REF</sub> | HSTL Input Reference Voltage                     |

| B1                  | Controls. See Function Control on page 7.                                                      | $V_{DD}$         | Power Supply (+ 2.5V)                            |

| B2                  | Controls. See Function Control on page 7.                                                      | $V_{SS}$         | Ground                                           |

| В3                  | Controls. See Function Control on page 7.                                                      | $V_{DDQ}$        | Output Power Supply                              |

| <del>LBO</del>      | Linear Burst Order ( $\overline{LBO}$ = 1, interleave mode; $\overline{LBO}$ = 0, linear mode) | ZQ               | Output Driver Impedance Control                  |

| TMS, TDI, TCK       | IEEE 1149.1 Test Inputs (LVTTL levels)                                                         | NC               | No Connect                                       |

# **Ordering Information**

| Part Number       | Organization | Cycle Time (ns) | Package    |

|-------------------|--------------|-----------------|------------|

| IBM043616CXLBC-20 | 512K x 36    | 2.0             | 9 x 17 BGA |

| IBM043616CXLBC-25 | 512K x 36    | 2.5             | 9 x 17 BGA |

| IBM043616CXLBC-27 | 512K x 36    | 2.7             | 9 x 17 BGA |

| IBM043616CXLBC-28 | 512K x 36    | 2.8             | 9 x 17 BGA |

| IBM043616CXLBC-30 | 512K x 36    | 3.0             | 9 x 17 BGA |

| IBM041816CXLBC-20 | 1M x 18      | 2.0             | 9 x 17 BGA |

| IBM041816CXLBC-25 | 1M x 18      | 2.5             | 9 x 17 BGA |

| IBM041816CXLBC-27 | 1M x 18      | 2.7             | 9 x 17 BGA |

| IBM041816CXLBC-28 | 1M x 18      | 2.8             | 9 x 17 BGA |

| IBM041816CXLBC-30 | 1M x 18      | 3.0             | 9 x 17 BGA |

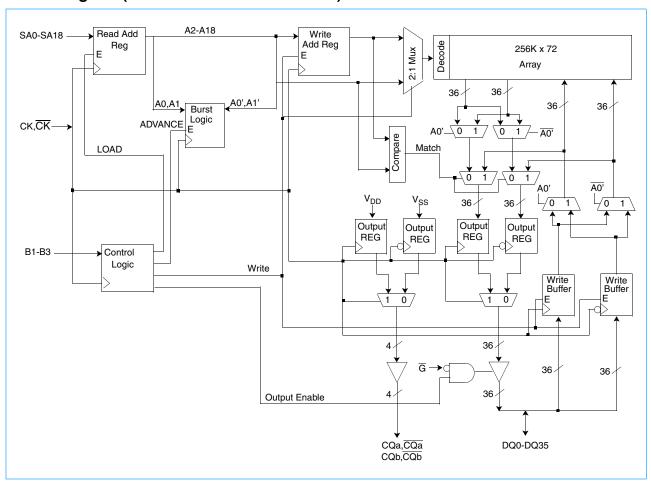

### **Block Diagram (x36 Double Data Rate Mode)**

#### **SRAM Features**

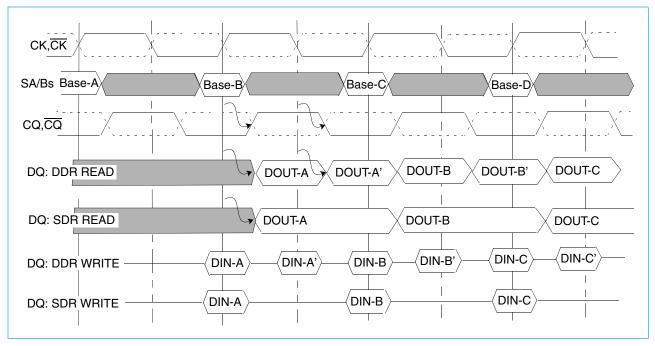

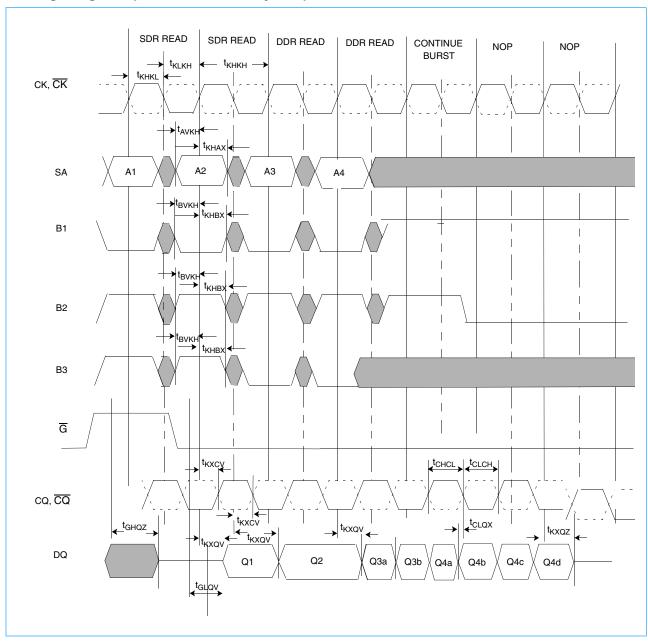

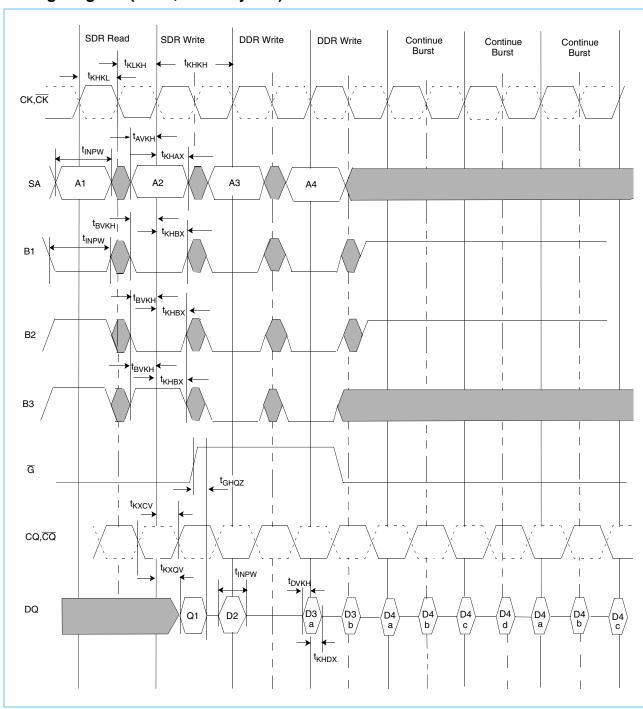

#### Double Data Rate (DDR) and Single Data Rate (SDR) Modes

The timing diagram on page 6 shows input and output data placements for both DDR and SDR modes. In DDR read mode, two sets of data-outs are generated from the second rising and falling edges of the CK clock, assuming the first rising edge of the CK clock samples the base address. The first of the two data-out sets (DOUT-A) is generated from the sampled base address (Base-A). The second data-out set (DOUT-A') is generated from the next burst-order address, according to the burst-order definition. Similarly, a DDR write requires data-in placement on the second rising and falling CK edges. In SDR read mode, only one set of data-outs is generated from the second rising CK edge. In SDR write mode, one set of data-ins is sampled on the second rising CK edge. The user may switch from DDR to SDR mode (or vice-versa) during any LOAD (B1 = 0) operation.

#### **Late Write**

The late-write function allows write data to be registered one cycle after addresses and controls. This feature eliminates one of two bus-turnaround cycles normally required when going from a read to a write operation. Late write is accomplished by buffering write addresses and data. The SRAM array update occurs during the third write cycle. Read-cycle addresses are monitored to determine if read data is to be supplied from the SRAM array or the write buffer. Full data coherency is maintained for both DDR and SDR operations. As a result, NOP (write buffer flush) operations are not required going from write cycles to read cycles.

#### **Echo Clocks**

Echo clocks CQ and  $\overline{CQ}$  are generated from rising and falling edges of the CK clock, with access times representative of the data-outs. Echo clocks keep running during write and NOP operations. Echo-clock operation is identical for both double-data-rate and single-data-rate operations. The close tracking of echo clocks and data-outs timings allows the echo clocks to be used as capture clocks for the data-outs by the receiving device.

### **Timing Diagram: Double Data Rate and Single Data Rate Modes**

#### **Programmable Impedance and Power Up Requirements**

An external resistor, RQ, must be connected between the ZQ pin on the SRAM and  $V_{SS}$  to allow the SRAM to adjust its output driver impedance. The value of RQ must be five times the value of the intended line impedance driven by the SRAM. The allowable range of RQ to guarantee impedance matching with a tolerance of 15% is between  $175\Omega$  and  $350\Omega$ . Periodic readjustment of the output driver impedance is necessary because the impedance is affected by drifts in supply voltage and temperature. One evaluation occurs every 64 clock cycles, and each evaluation may move the output driver impedance level one step at a time towards the optimum level. The output driver has 64 discrete binary weighted steps. Impedance updates for zeros occur whenever the SRAM is driving ones for the same DQs; impedance updates for ones occur whenever SRAM is driving zeros for the same DQs. Updates of both zeros and ones occur when the SRAM is High-Z.. The SRAM requires 4  $\mu$ s of power-up time after  $V_{DD}$  reaches its operating range. Furthermore, to guarantee the output driver impedance, the SRAM requires 2048 clock cycles and a Read "0" and Read "1" or a Read "1" and a Read "0" across all outputs. The RC time constant of the loaded RQ trace must be less than 3ns.

#### **Power-Up and Power-Down Sequences**

The power supplies must be powered up in the following sequence:  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{REF}$ , followed by inputs. The power-down sequence must be the reverse.  $V_{DDQ}$  must not exceed  $V_{DD}$ .

#### **Initial Writes**

DQ and CQ timings will not be guaranteed until at least two write cycles are performed. These cycles can be part of the programmable impedance initial cycles.

#### **Function Control**

The function control is dependent on the state of the three function control pins (B1, B2, and B3), captured when CK transitions from low to high as described in the following table ("n" refers to the current cycle and "n-1" refers to the previous SRAM cycle):

| B1 (n-1) | B2 (n-1) | B3 (n-1) | B1 (n) | B2 (n) | B3 (n) | Function (n)                                   |

|----------|----------|----------|--------|--------|--------|------------------------------------------------|

| Х        | Х        | Х        | 0      | 0      | 0      | Load New Address, Double Data Rate (DDR) Write |

| х        | Х        | Х        | 0      | 0      | 1      | Load New Address, Single Data Rate (SDR) Write |

| х        | Х        | Х        | 0      | 1      | 0      | Load New Address, DDR Read                     |

| Х        | Х        | Х        | 0      | 1      | 1      | Load New Address, SDR Read                     |

| 0        | 0        | 0        | 1      | 1      | Х      | Continue Burst, DDR Write                      |

| 0        | 0        | 1        | 1      | 1      | Х      | Continue Burst, SDR Write                      |

| 0        | 1        | 0        | 1      | 1      | Х      | Continue Burst, DDR Read                       |

| 0        | 1        | 1        | 1      | 1      | Х      | Continue Burst, SDR Read                       |

| Х        | Х        | Х        | 1      | 0      | Х      | NOP (High-Z cycle n+1)                         |

| 1        | 0        | Х        | 1      | Х      | Х      | NOP (High-Z cycle n+2)                         |

#### **Burst Order Definition**

The DC state of the  $\overline{\text{LBO}}$  pin determines the burst order of the addresses given the starting address in a Load operation (B1 = 0). The following table defines the order of addresses for the two different states of  $\overline{\text{LBO}}$ .

# Address Sequence when $\overline{LBO} = V_{DD}$ (Interleave Burst)

|                  | SA1 | SA0 | SA1 | SA0 | SA1 | SA0 | SA1 | SA0 |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Starting address | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 1   |

| Second address   | 0   | 1   | 0   | 0   | 1   | 1   | 1   | 0   |

| Third address    | 1   | 0   | 1   | 1   | 0   | 0   | 0   | 1   |

| Fourth address   | 1   | 1   | 1   | 0   | 0   | 1   | 0   | 0   |

# Address Sequence when $\overline{LBO} = V_{SS}$ (Linear Burst)

|                  | SA1 | SA0 | SA1 | SA0 | SA1 | SA0 | SA1 | SA0 |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Starting address | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 1   |

| Second address   | 0   | 1   | 1   | 0   | 1   | 1   | 0   | 0   |

| Third address    | 1   | 0   | 1   | 1   | 0   | 0   | 0   | 1   |

| Fourth address   | 1   | 1   | 0   | 0   | 0   | 1   | 1   | 0   |

### **Clock Truth Table**

| СК  | B1 (n) | B2 (n) | B3 (n) | DQ (n) | DQ (n+1)               | DQ (n+1.5)             | MODE                     |

|-----|--------|--------|--------|--------|------------------------|------------------------|--------------------------|

| L→H | L      | Н      | Н      | Х      | D <sub>out</sub> 0-35  | Previous Data<br>Held  | Read Cycle SDR           |

| L→H | L      | Н      | L      | Х      | D <sub>out</sub> 0-35a | D <sub>out</sub> 0-35b | Read Cycle DDR           |

| L→H | L      | L      | Н      | Х      | D <sub>IN</sub> 0-35   | Х                      | Write cycle SDR          |

| L→H | L      | L      | L      | Х      | D <sub>IN</sub> 0-35a  | D <sub>IN</sub> 0-35b  | Write Cycle DDR          |

| L→H | Н      | L      | Х      | Х      | High-Z                 | High-Z                 | NOP (Deselect) Cycle     |

| L→H | Н      | Н      | Х      |        |                        |                        | Continue Burst Operation |

# **Output Enable Truth Table**

| Operation (n, n + 1) | <u>G</u> (n) | <u>ਰ</u> (n + 1) | DQ (n) | DQ (n + 1)            |

|----------------------|--------------|------------------|--------|-----------------------|

| Read                 | L            | L                | Х      | D <sub>OUT</sub> 0-35 |

| Read                 | Н            | Н                | High-Z | High-Z                |

| Write                | L            | L                | X      | High-Z                |

| NOP                  | L            | L                | Х      | High-Z                |

### **Absolute Maximum Ratings**

| Symbol           | Parameter                    | Rating        | Units | Notes |

|------------------|------------------------------|---------------|-------|-------|

| V <sub>DD</sub>  | Power Supply Voltage         | -0.5 to 2.825 | V     | 1     |

| V <sub>IN</sub>  | Input Voltage                | -0.5 to 2.4   | V     | 1     |

| V <sub>OUT</sub> | Output Voltage               | -0.5 to 2.825 | V     | 1     |

| TJ               | Operating Temperature        | 0 to +110     | °C    | 1     |

| T <sub>STG</sub> | Storage Temperature          | -55 to +125   | °C    | 1     |

| I <sub>OUT</sub> | Short Circuit Output Current | 25            | mA    | 1     |

<sup>1.</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Recommended DC Operating Conditions** $(T_A = 0 \text{ to } 85^{\circ}\text{C})$

| Symbol                 | Parameter                                                 | Min.                  | Тур.      | Max.                   | Units | Notes |

|------------------------|-----------------------------------------------------------|-----------------------|-----------|------------------------|-------|-------|

| $V_{DD}$               | Supply Voltage                                            | 2.5V - 5%             | 2.5       | 2.5V + 5%              | V     | 1     |

| $V_{DDQ}$              | Output Driver Supply Voltage                              | 1.4                   | 1.5       | 1.6                    | V     | 1     |

| V <sub>IH</sub>        | Input High Voltage                                        | V <sub>REF</sub> +0.1 |           | V <sub>DDQ</sub> + 0.3 | V     | 1, 2  |

| V <sub>IL</sub>        | Input Low Voltage                                         | -0.3                  |           | V <sub>REF</sub> - 0.1 | V     | 1, 3  |

| V <sub>REF</sub>       | Input Reference Voltage                                   | 0.68                  | 0.68 0.75 |                        | V     | 1     |

| V <sub>IN - CLK</sub>  | Clocks Signal Voltage                                     | -0.3                  |           | V <sub>DDQ</sub> + 0.3 | V     | 1, 4  |

| V <sub>DIF - CLK</sub> | V <sub>DIF - CLK</sub> Differential Clocks Signal Voltage |                       |           | V <sub>DDQ</sub> + 0.6 | V     | 1, 5  |

| V <sub>CM - CLK</sub>  | Clocks Common Mode Voltage                                | 0.7                   |           | 0.8                    | V     | 1     |

- 1. All voltages referenced to V<sub>SS</sub>. All V<sub>DD</sub>, V<sub>DDQ</sub>, and V<sub>SS</sub> pins must be connected.

2.  $V_{IH}(Max)DC = V_{DDQ} + 0.3V$ ,  $V_{IH}(Max)AC = 2.6V$  (2.1 V for DQs) (pulse width  $\leq$  20% of cycle time).

- 3.  $V_{IL}(Min)DC$  = 0.3 V,  $V_{IL}(Min)AC$  = -1.0 V (-0.5V for DQs) (pulse width  $\leq$  20% of cycle time).

- 4.  $V_{IN\text{-}CLK}$  specifies the maximum allowable DC excursions of each differential clock (CK,  $\overline{CK}$ ).

- 5.  $V_{\text{DIF-CLK}}$  specifies the minimum clock differential voltage required for switching.

## **DC Electrical Characteristics** $(T_A = 0 \text{ to } +85^{\circ}\text{C}, V_{DD} = 2.5 \text{ V } \pm 5\%)$

| Symbol              | Parameter                                                                                     |     |     | Min.                  | Max.                  | Units | Notes |

|---------------------|-----------------------------------------------------------------------------------------------|-----|-----|-----------------------|-----------------------|-------|-------|

|                     |                                                                                               |     | -20 |                       | 910                   |       |       |

|                     |                                                                                               | x36 | -25 |                       | 750                   | mA    | 1     |

| l                   | Average Power Supply Operating Current                                                        |     | -30 |                       | 640                   |       |       |

| I <sub>DD</sub>     | $(I_{OUT} = 0, V_{IN} = V_{IH} \text{ or } V_{IL})$                                           |     | -20 |                       | 660                   |       |       |

|                     |                                                                                               | x18 | -25 |                       | 540                   | mA    | 1     |

|                     |                                                                                               |     | -30 |                       | 470                   |       |       |

| I <sub>NOOP</sub>   | Power Supply NOOP Current                                                                     |     |     |                       | 150                   | mA    | 1     |

| ILI                 | Input Leakage Current, any input $(V_{IN} = V_{SS} \text{ or } V_{DDQ})$                      |     |     | -2                    | +2                    | μΑ    |       |

| I <sub>LO</sub>     | Output Leakage Current (V <sub>OUT</sub> = V <sub>SS</sub> or V <sub>DDQ</sub> , DQ in High-Z |     |     | -5                    | +5                    | μΑ    |       |

| V <sub>OH</sub>     | Output High Level Voltage (I <sub>OH</sub> = -6mA)                                            |     |     | V <sub>DDQ</sub> -0.4 | $V_{DDQ}$             | V     | 2     |

| V <sub>OL</sub>     | Output Low Level Voltage (I <sub>OL</sub> = +6mA)                                             |     |     | $V_{SS}$              | V <sub>SS</sub> + 0.4 | V     | 2     |

| I <sub>LIJTAG</sub> | JTAG Leakage Current (V <sub>IN</sub> = V <sub>SS</sub> or V <sub>DD</sub> )                  |     |     | -70                   | +10                   | μΑ    | 3     |

- I<sub>OUT</sub> = Chip Output Current

Minimum Impedance Output Driver

- 3. For JTAG Inputs only

### **Programmable Impedance Output Driver DC Electrical Characteristics**

$(T_A = 0 \text{ to } +85^{\circ}\text{C}, \ V_{DD} = 2.5 \ \text{V} \pm 5\%)$

| Symbol          | Parameter           | Min.                | Max.                | Units | Notes   |

|-----------------|---------------------|---------------------|---------------------|-------|---------|

| V <sub>OH</sub> | Output High Voltage | V <sub>DDQ</sub> /2 | $V_{DDQ}$           | V     | 1, 2, 4 |

| V <sub>OL</sub> | Output Low Voltage  | $V_{SS}$            | V <sub>DDQ</sub> /2 | V     | 3, 4    |

- $1. \quad I_{OH} = \left(V_{DDQ} \, / \, 2\right) \, / \, \left(RQ \, / \, 5\right) \, \pm \, 15\% \, \, @ \, \, V_{OH} = V_{DDQ} \, / \, 2 \, \, (for: \, 175\Omega \leq RQ \leq 250\Omega).$

- $2. \quad I_{OH} = \left( V_{DDQ} \, / \, 2 \right) \, / \, \left( RQ \, / \, 5 \right) \, \pm \, 15\%, \, + \, 20\% \, \, @ \, \, V_{OH} = \, V_{DDQ} \, / \, 2 \, \, (for: 250\Omega \leq RQ \leq 350\Omega).$

- 3.  $I_{OL} = (V_{DDQ} \, / \, 2) \, / \, (RQ \, / \, 5) \pm 15\%$  @  $V_{OL} = V_{DDQ} \, / \, 2$  (for:  $175\Omega \leq RQ \leq 350\Omega$ ).

- 4. Parameter tested with RQ =  $250\Omega$  and  $V_{DDQ} = 1.5 \text{ V}$ .

#### **PBGA Thermal Characteristics**

| Symbol | Parameter                           | Rating | Units |

|--------|-------------------------------------|--------|-------|

| R⊚JC   | Thermal Resistance Junction to Case | 1      | °C/W  |

### **Capacitance** $(T_A = 0 \text{ to } +85^{\circ}\text{C}, V_{DD} = 2.5 \text{ V} \pm 5\%, f = 1 \text{MHz})$

| Symbol           | Parameter                       | Test Condition | Max. | Units |

|------------------|---------------------------------|----------------|------|-------|

| C <sub>IN</sub>  | Input Capacitance               | $V_{IN} = 0V$  | 4    | pF    |

| C <sub>OUT</sub> | Data I/O Capacitance (DQ0-DQ35) | $V_{OUT} = 0V$ | 5    | pF    |

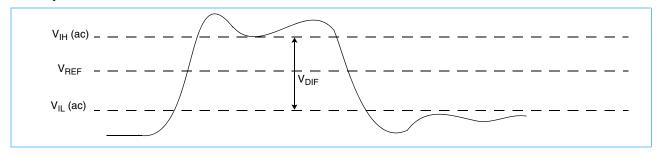

## **AC Input Characteristics** $(T_A = 0 \text{ to } +85^{\circ}\text{C}, V_{DD} = 2.5 \text{ V} \pm 5\%)$

| Symbol                | Parameter                                | Min.                   | Max.                     | Units | Notes |

|-----------------------|------------------------------------------|------------------------|--------------------------|-------|-------|

| V <sub>IH</sub> (ac)  | AC Input Logic High                      | V <sub>REF</sub> + 400 |                          | mV    | 3, 4  |

| V <sub>IL</sub> (ac)  | AC Input Logic Low                       |                        | V <sub>REF</sub> - 400   | mV    | 3, 4  |

| V <sub>DIF</sub> (ac) | Clock Input Differential Voltage         | 800                    |                          | mV    | 2, 3  |

| V <sub>REF</sub> (ac) | V <sub>REF</sub> Peak-to-Peak AC Voltage |                        | 5% V <sub>REF</sub> (dc) | mV    | 1     |

- 1. The peak-to-peak AC component superimposed on  $V_{REF}$  may not exceed 5% of the DC component of  $V_{REF}$ .

- 2. SRAM performance is a function of clock input differential voltage ( $V_{DIF}$ ).

- 3. To guarantee AC characteristics;  $V_{IH}$ ,  $V_{IL}$ ,  $T_{rise}$  and  $T_{fall}$  of inputs and clocks must be within 20% of each other. If these conditions are not met then:

- Setup time is measured from clock crossing to inputs at their switched  $V_{IHAC}$ ,  $V_{ILAC}$  levels.

- $\bullet \quad \text{Hold time is measured from clock crossing to inputs switching out of their valid $V_{IHAC}$, $V_{ILAC}$ levels.}$

- 4. See AC Input Definition on page 11.

## **AC Input Definition**

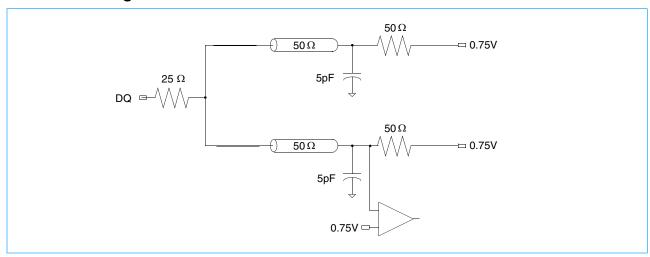

# **AC Test Loading**

# **AC Test Conditions** $(T_A = 0 \text{ to } +85^{\circ}\text{C}, V_{DD} = 2.5 \text{ V} \pm 5\%, V_{DDQ} = 1.5 \text{ V})$

| Symbol               | Parameter                                      | Conditions               | Units | Notes |

|----------------------|------------------------------------------------|--------------------------|-------|-------|

| $V_{IH}$             | Input High Level                               | 1.25                     | V     |       |

| $V_{IL}$             | Input Low Level                                | 0.25                     | V     |       |

| $V_{REF}$            | Input Reference Voltage                        | 0.75                     | V     |       |

| V <sub>DIF-CLK</sub> | Differential Clocks Voltage                    | 1.0                      | V     |       |

| V <sub>CM-CLK</sub>  | Clocks Common Mode Voltage                     | 0.75                     | V     |       |

| $T_{R}$              | Input Rise Time                                | 0.5                      | ns    |       |

| $T_F$                | Input Fall Time                                | 0.5                      | ns    |       |

|                      | I/O Signals Reference Level (except CK clocks) | 0.75                     | V     |       |

|                      | Clocks Reference Level                         | Differential Cross Point | V     |       |

|                      | Output Load Conditions                         |                          |       | 1     |

### **AC Characteristics** $(T_A = 0 \text{ to } +85^{\circ}\text{C}, V_{DD} = 2.5 \text{ V} \pm 5\%)$

| Cumbal                    | Dorometer                                                                                    | -2                        | 20                        | -2                        | 25                        | -2                        | 27                        | -2                        | 28                        | -3                        | 30                        | Lleite | Notes            |

|---------------------------|----------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------|------------------|

| Symbol                    | Parameter                                                                                    | Min.                      | Max.                      | Units  | Notes            |

| t <sub>KHKH</sub>         | Cycle Time                                                                                   | 2.0                       |                           | 2.5                       |                           | 2.7                       |                           | 2.8                       |                           | 3.0                       |                           | ns     |                  |

| t <sub>KHKL</sub>         | Clock High Pulse Width                                                                       | 0.9                       |                           | 1.2                       |                           | 1.2                       |                           | 1.2                       |                           | 1.4                       |                           | ns     |                  |

| t <sub>KLKH</sub>         | Clock Low Pulse Width                                                                        | 0.9                       |                           | 1.2                       |                           | 1.2                       |                           | 1.2                       |                           | 1.4                       |                           | ns     |                  |

| t <sub>AVKH</sub>         | Address Setup Time                                                                           | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | ns     | 1, 6, 8          |

| t <sub>KHAX</sub>         | Address Hold Time                                                                            | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | ns     | 1, 8             |

| t <sub>BVKH</sub>         | Function Control (B1, B2, B3) Setup<br>Time                                                  | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | ns     | 1, 8             |

| t <sub>KHBX</sub>         | Function Control (B1, B2, B3) Hold<br>Time                                                   | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | 0.4                       |                           | ns     | 1, 8             |

| t <sub>DVKH</sub>         | Data-In Setup Time                                                                           | 0.17                      |                           | 0.21                      |                           | 0.30                      |                           | 0.30                      |                           | 0.30                      |                           | ns     | 1, 9, 6, 8       |

| t <sub>KHDX</sub>         | Data-In Hold Time                                                                            | 0.17                      |                           | 0.21                      |                           | 0.30                      |                           | 0.30                      |                           | 0.30                      |                           | ns     | 1, 9, 6, 8       |

| t <sub>INPW</sub>         | Input Pulse Width                                                                            | 0.8                       |                           | 1.0                       |                           | 1.0                       |                           | 1.0                       |                           | 1.2                       |                           |        |                  |

| t <sub>CHCL</sub>         | Echo Clock (CQ) High Pulse Width                                                             | t <sub>KHKL</sub><br>-0.1 | t <sub>KHKL</sub><br>+0.1 | ns     | 1, 3, 6          |

| t <sub>CLCH</sub>         | Echo Clock (CQ) Low Pulse Width                                                              | t <sub>KLKH</sub><br>-0.1 | t <sub>KLKH</sub><br>+0.1 | ns     | 1, 3, 6          |

| t <sub>KXCV</sub>         | Clock (CK) crossing to Echo clock (CQ) Valid                                                 | 0.8                       | 2.3                       | 0.8                       | 1.8                       | 0.8                       | 1.8                       | 0.8                       | 1.8                       | 0.8                       | 1.7                       | ns     | 1, 2, 4, 6,<br>7 |

| t <sub>KXQV</sub>         | Clock (CK) crossing to Output Valid                                                          | 0.8                       | 2.3                       | 0.8                       | 1.8                       | 0.8                       | 1.8                       | 0.8                       | 1.8                       | 0.8                       | 1.7                       | ns     | 1, 2, 6, 7       |

| t <sub>KXQZ</sub>         | Clock (CK) crossing to Output High-Z                                                         | 0.8                       | 2.3                       | 0.8                       | 1.8                       | 0.8                       | 1.8                       | 0.8                       | 1.8                       | 0.8                       | 1.7                       | ns     | 1, 2, 7          |

| t <sub>KXQLZ</sub>        | Clock (CK) crossing to Output Active                                                         | 0.8                       | 2.3                       | 0.8                       | 1.8                       | 0.8                       | 1.8                       | 0.8                       | 1.8                       | 0.8                       | 1.7                       | ns     | 1, 2, 6, 7       |

| t <sub>QVTRK</sub>        | Echo Clock (CQ) Valid to Output Valid Tracking $(t_{KXCV} - t_{KXQV})$                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | ns     | 1, 3, 5, 6       |

| t <sub>QZTRK</sub>        | Echo Clock (CQ) Valid to Output<br>High-Z Tracking (t <sub>KXCV</sub> - t <sub>KXQZ</sub> )  | -0.2                      | 0.2                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | ns     | 1, 3, 5, 6       |

| t <sub>QLZ</sub> -<br>TRK | Echo Clock (CQ) Valid to Output<br>Active Tracking (t <sub>KXCV</sub> - t <sub>KXQLZ</sub> ) | -0.2                      | 0.2                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | -0.2                      | 0.2                       | ns     | 1, 3, 5, 6       |

| t <sub>GHQZ</sub>         | Output Enable ( $\overline{G}$ ) High to High-Z                                              | _                         | 1.4                       | _                         | 1.7                       | _                         | 1.7                       | _                         | 1.7                       | _                         | 2.0                       | ns     | 3                |

| t <sub>GLQV</sub>         | Output Enable $(\overline{G})$ Low to Output Valid                                           | 0.5                       | 1.4                       | 0.5                       | 1.7                       | 0.5                       | 1.7                       | 0.5                       | 1.7                       | 0.5                       | 2.0                       | ns     | 2, 3             |

- 1. See AC Test Loading on page 11. To guarantee AC timing specifications, AC test conditions must be met.

- 2. Maximum is tested at 2.38V and 85°C. Minimum is tested at 2.75V and 0°C.

- 3. These parameters may not be tested at the values shown in this table, and may only be guaranteed by design.

- 4. Echo clock (CQ) Valid refers to CQ and  $\overline{\text{CQ}}$  rising and falling edges.

- 5. The tracking between echo-clock access times and DQ access times is across all cycle boundaries for any given SRAM address and function pattern.

- 6. CK and CK clocks must be used differentially in order to meet specification.

- 7. Access pushes out as cycle time decreases.

- 8. To guarantee AC characteristics; V<sub>IH</sub>, V<sub>IL</sub>, T<sub>rise</sub>, and T<sub>fall</sub> of inputs and clocks must be within 20% of each other. If these conditions are not met then:

- Setup time is measured from clock crossing to inputs at their switched V<sub>IHAC</sub>, V<sub>ILAC</sub> levels.

- Hold time is measured from clock crossing to inputs switching out of their valid V<sub>IHAC</sub>, V<sub>ILAC</sub> levels.

- 9. Guaranteed by design and tested without guardband.

## **Timing Diagram (Read and NOP Cycles)**

# **Timing Diagram (Read, Write Cycles)**

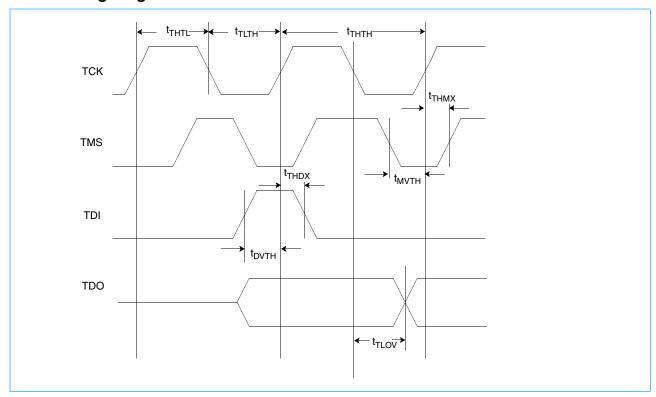

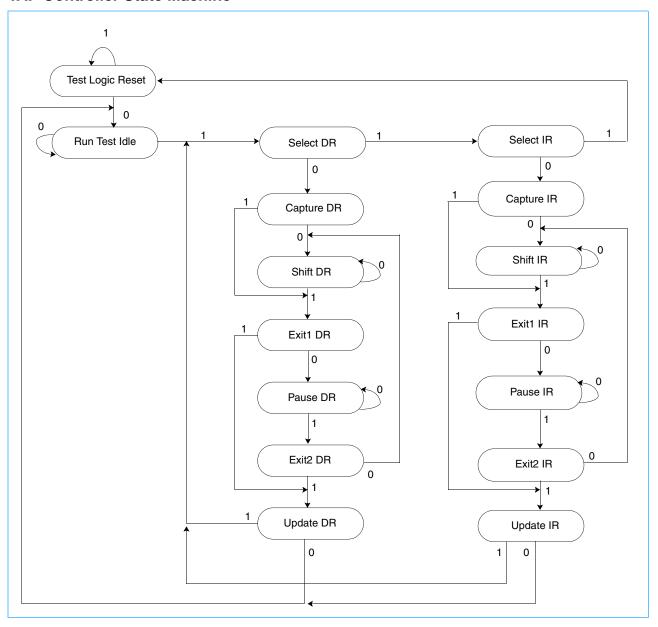

### **IEEE 1149.1 TAP and Boundary SCAN**

The SRAM provides a limited set of JTAG functions intended to test the interconnection between SRAM I/Os and printed circuit-board traces or other components. There is no multiplexer in the path from the I/O pins to the RAM core.

In conformance with IEEE standard 1149.1, the SRAM contains a TAP controller, instruction register, boundary-scan register, bypass register, and ID register.

The TAP controller has a standard 16-state machine that resets internally upon power-up; therefore, a TRST signal is not required.

#### Signal List:

· TCK: Test Clock

TMS: Test Mode Select

TDI: Test Data InTDO: Test Data Out

### **JTAG Recommended DC Operating Conditions** $(T_A = 0 \text{ to } 85^{\circ}\text{C})$

| Symbol           | Parameter               | Min. | Тур. | Max. | Units | Notes |

|------------------|-------------------------|------|------|------|-------|-------|

| V <sub>IH1</sub> | JTAG Input High Voltage | 1.7  | _    | 2.8  | V     |       |

| V <sub>IL1</sub> | JTAG Input Low Voltage  | -0.3 | _    | 0.8  | V     |       |

| V <sub>OH1</sub> | JTAG Output High Level  | 2.1  | _    | _    | V     | 2     |

| V <sub>OL1</sub> | JTAG Output Low Level   | _    | _    | 0.2  | V     | 1     |

<sup>1.</sup> OH1 = -2mA at 2.1V.

## **JTAG AC Test Conditions** $(T_A = 0 \text{ to } +85^{\circ}\text{C}, V_{DD} = 2.5 \text{ V} \pm 5\%)$

| Symbol           | Parameter                               | Conditions | Units | Notes |

|------------------|-----------------------------------------|------------|-------|-------|

| V <sub>IH1</sub> | Input Pulse High Level                  | 2.0        | V     |       |

| $V_{IL1}$        | Input Pulse Low Level                   | 0.0        | V     |       |

| T <sub>R1</sub>  | Input Rise Time                         | 2.0        | ns    |       |

| T <sub>F1</sub>  | Input Fall Time                         | 2.0        | ns    |       |

|                  | Input and Output Timing Reference Level | 1.0        | V     | 1     |

<sup>1.</sup> See AC Test Loading on page 11.

<sup>2.</sup> OL1 = +2mA at 0.2V.

# **JTAG AC Characteristics** $(T_A = 0 \text{ to } +85^{\circ}\text{C}, \ V_{DD} = 2.5 \ \text{V} \pm 5\%)$

|                       |                                                               |                                                                                                                                   | Units                                                                                                                             | Notes                                                                                                                                                                                                      |

|-----------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK Cycle Time        | 20                                                            |                                                                                                                                   | ns                                                                                                                                |                                                                                                                                                                                                            |

| TCK High Pulse Width  | 7                                                             |                                                                                                                                   | ns                                                                                                                                |                                                                                                                                                                                                            |

| TCK Low Pulse Width   | 7                                                             |                                                                                                                                   | ns                                                                                                                                |                                                                                                                                                                                                            |

| TMS Setup             | 4                                                             |                                                                                                                                   | ns                                                                                                                                |                                                                                                                                                                                                            |

| TMS Hold              | 4                                                             |                                                                                                                                   | ns                                                                                                                                |                                                                                                                                                                                                            |

| TDI Setup             | 4                                                             |                                                                                                                                   | ns                                                                                                                                |                                                                                                                                                                                                            |

| TDI Hold              | 4                                                             |                                                                                                                                   | ns                                                                                                                                |                                                                                                                                                                                                            |

| TCK Low to Valid Data |                                                               | 7                                                                                                                                 | ns                                                                                                                                | 1                                                                                                                                                                                                          |

|                       | TCK Low Pulse Width  TMS Setup  TMS Hold  TDI Setup  TDI Hold | TCK Low Pulse Width       7         TMS Setup       4         TMS Hold       4         TDI Setup       4         TDI Hold       4 | TCK Low Pulse Width       7         TMS Setup       4         TMS Hold       4         TDI Setup       4         TDI Hold       4 | TCK Low Pulse Width         7         ns           TMS Setup         4         ns           TMS Hold         4         ns           TDI Setup         4         ns           TDI Hold         4         ns |

## **JTAG Timing Diagram**

### **Scan Register Definition**

| Register Name                 | Bit Size x18 | Bit Size x36 |

|-------------------------------|--------------|--------------|

| Instruction                   | 3            | 3            |

| Bypass                        | 1            | 1            |

| ID                            | 32           | 32           |

| Boundary Scan <sup>1, 2</sup> | 49           | 68           |

- 1. The boundary-scan chain consists of the following bits:

- 36 or 18 bits for data inputs depending on x36 or x18 configuration

- 19 bits for SA0-SA18 for x36; 20 bits for SA0-SA19 for x18

- 4 or 2 bits for CQ and  $\overline{\text{CQ}}$  clocks depending on x36 or x18 configuration

- 9 bits for CK,  $\overline{CK}$ , ZQ,  $\overline{LBO}$ , B1, B2, B3, MODE, and  $\overline{G}$

- 2. CK and CK clocks connect to a differential receiver that generates a single-ended clock signal. This signal and its inverted value are used for boundary-scan sampling. CQ and CQ clocks are sampled from the CK and CK boundary-scan register inputs.

### **ID Register Definition**

|           |                                                | Field Bit Number and Description            |                              |                                  |                 |  |  |

|-----------|------------------------------------------------|---------------------------------------------|------------------------------|----------------------------------|-----------------|--|--|

| Part      | Revision Number<br>(31:28)<br>IBM Internal Use | Device Density and<br>Configuration (27:19) | Vendor Definition<br>(18:12) | Manufacture JEDEC<br>Code (11:1) | Start<br>Bit(0) |  |  |

| 1M x 18   | xxxx                                           | 011100001                                   | 0110011                      | 00010100100                      | 1               |  |  |

| 512K x 36 | XXXX                                           | 011011110                                   | 0110011                      | 00010100100                      | 1               |  |  |

### **Instruction Set**

| Code | Instruction | Notes |

|------|-------------|-------|

| 000  | SAMPLE-Z    | 1     |

| 001  | IDCODE      | 1     |

| 010  | SAMPLE-Z    | 1     |

| 011  | PRIVATE     | 4     |

| 100  | SAMPLE      | 3     |

| 101  | PRIVATE     | 4     |

| 110  | PRIVATE     | 4     |

| 111  | BYPASS      | 2     |

- 1. Instruction places DQs in High-Z in order to sample all input data regardless of other SRAM inputs.

- 2. BYPASS register is initialized to V<sub>SS</sub> when BYPASS instruction is invoked. The BYPASS register also holds the last serially loaded TDI when exiting the Shift DR state.

- 3. SAMPLE instruction does not place DQs in High-Z.

- 4. PRIVATE is reserved for the exclusive use of IBM. Invoking this instruction will cause improper SRAM functionality.

This part has not been designed to comply with the following sections of IEEE 1149.1:

- 7.2.1.b, e

- 7.7.1.a-f

- 10.1.1.b, e

- 10.7.1.a-d

# **Boundary Scan Order (x36)**

| Exit Order | Signal            | Bump # | Exit Order | Signal | Bump # | Exit Order | Signal     | Bump # |

|------------|-------------------|--------|------------|--------|--------|------------|------------|--------|

| 1          | SA1               | 5R     | 24         | CQ     | 8F     | 47         | CQ         | 2F     |

| 2          | SA0               | 5T     | 25         | DQ11   | 9D     | 48         | DQ25       | 1F     |

| 3          | SA2               | 6R     | 26         | DQ17   | 7F     | 49         | DQ19       | 3Н     |

| 4          | SA3               | 7T     | 27         | DQ14   | 8D     | 50         | DQ22       | 2H     |

| 5          | SA4               | 7P     | 28         | DQ12   | 9B     | 51         | DQ26       | 1H     |

| 6          | DQ2               | 8T     | 29         | DQ15   | 8B     | 52         | ZQ         | 5A     |

| 7          | DQ5               | 9T     | 30         | SA5    | 7D     | 53         | B1         | 5B     |

| 8          | DQ3               | 8P     | 31         | SA6    | 7C     | 54         | B2         | 5K     |

| 9          | DQ0               | 7M     | 32         | SA7    | 7B     | 55         | В3         | 5L     |

| 10         | DQ6               | 9P     | 33         | SA8    | 7A     | 56         | <u>LBO</u> | 4L     |

| 11         | CQ                | 8M     | 34         | SA9    | 6C     | 57         | DQ27       | 1K     |

| 12         | DQ7               | 9M     | 35         | SA10   | 6A     | 58         | DQ31       | 2K     |

| 13         | DQ1               | 7K     | 36         | SA11   | 4A     | 59         | DQ34       | зк     |

| 14         | DQ4               | 8K     | 37         | SA12   | 4C     | 60         | DQ28       | 1M     |

| 15         | DQ8               | 9K     | 38         | SA13   | ЗА     | 61         | CQ         | 2M     |

| 16         | MODE <sup>1</sup> | 6L     | 39         | SA14   | 3B     | 62         | DQ29       | 1P     |

| 17         | CK                | 5H     | 40         | SA15   | 3C     | 63         | DQ35       | ЗМ     |

| 18         | СК                | 5G     | 41         | SA18   | 3D     | 64         | DQ32       | 2P     |

| 19         | G                 | 5C     | 42         | DQ20   | 2B     | 65         | DQ30       | 1T     |

| 20         | DQ9               | 9H     | 43         | DQ23   | 1B     | 66         | DQ33       | 2T     |

| 21         | DQ13              | 8H     | 44         | DQ21   | 2D     | 67         | SA16       | 3Т     |

| 22         | DQ16              | 7H     | 45         | DQ18   | 3F     | 68         | SA17       | 4R     |

| 23         | DQ10              | 9F     | 46         | DQ24   | 1D     |            |            |        |

<sup>1.</sup> Mode will scan out the value placed on the Mode pin or, if the Mode pin is floated, Mode will scan  $V_{SS}$ .

# **Boundary Scan Order (x18)**

| Exit Order | Signal            | Bump # | Exit Order | Signal     | Bump # |

|------------|-------------------|--------|------------|------------|--------|

| 1          | SA1               | 5R     | 26         | SA11       | 4A     |

| 2          | SA0               | 5T     | 27         | SA12       | 4C     |

| 3          | SA2               | 6R     | 28         | SA13       | ЗА     |

| 4          | SA3               | 7T     | 29         | SA14       | 3B     |

| 5          | SA4               | 7P     | 30         | SA15       | 3C     |

| 6          | DQ1               | 8T     | 31         | SA18       | 3D     |

| 7          | DQ2               | 9P     | 32         | DQ10       | 2B     |

| 8          | CQ                | 8M     | 33         | DQ11       | 1D     |

| 9          | DQ0               | 7K     | 34         | CQ         | 2F     |

| 10         | DQ3               | 9K     | 35         | DQ9        | 3H     |

| 11         | MODE <sup>1</sup> | 6L     | 36         | DQ12       | 1H     |

| 12         | СК                | 5H     | 37         | ZQ         | 5A     |

| 13         | СК                | 5G     | 38         | B1         | 5B     |

| 14         | G                 | 5C     | 39         | B2         | 5K     |

| 15         | DQ6               | 8H     | 40         | В3         | 5L     |

| 16         | DQ4               | 9F     | 41         | <u>LBO</u> | 4L     |

| 17         | DQ8               | 7F     | 42         | DQ15       | 2K     |

| 18         | DQ7               | 8D     | 43         | DQ13       | 1M     |

| 19         | DQ5               | 9B     | 44         | DQ17       | ЗМ     |

| 20         | SA5               | 7D     | 45         | DQ16       | 2P     |

| 21         | SA6               | 7C     | 46         | DQ14       | 1T     |

| 22         | SA7               | 7B     | 47         | SA19       | 3P     |

| 23         | SA8               | 7A     | 48         | SA16       | ЗТ     |

| 24         | SA9               | 6C     | 49         | SA17       | 4R     |

| 25         | SA10              | 6A     |            |            |        |

<sup>1.</sup> Mode will scan out the value placed on the Mode pin or, if the Mode pin is floated, Mode will scan  $V_{SS}$ .

# **TAP Controller State Machine**

### 9 x 17 BGA Dimensions

# **Revision Log**

| Rev          | Contents of Modification |

|--------------|--------------------------|

| June 3, 2002 | Initial release (00).    |

© Copyright International Business Machines Corporation 2002

All Rights Reserved

Printed in the United States of America June 2002

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM IBM Logo

IEEE and IEEE 802 are registered trademarks in the United States of the Institute of Electrical and Electronics Engineers.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation, life support, space, nuclear, or military applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6351

The IBM home page can be found at <a href="http://www.ibm.com">http://www.ibm.com</a>

The IBM Microelectronics Division home page can be found at http://www.chips.ibm.com

June 3, 2002