W83L784R

Winbond H/W

Monitoring IC

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-1 - Revision 0.54

W83L784R

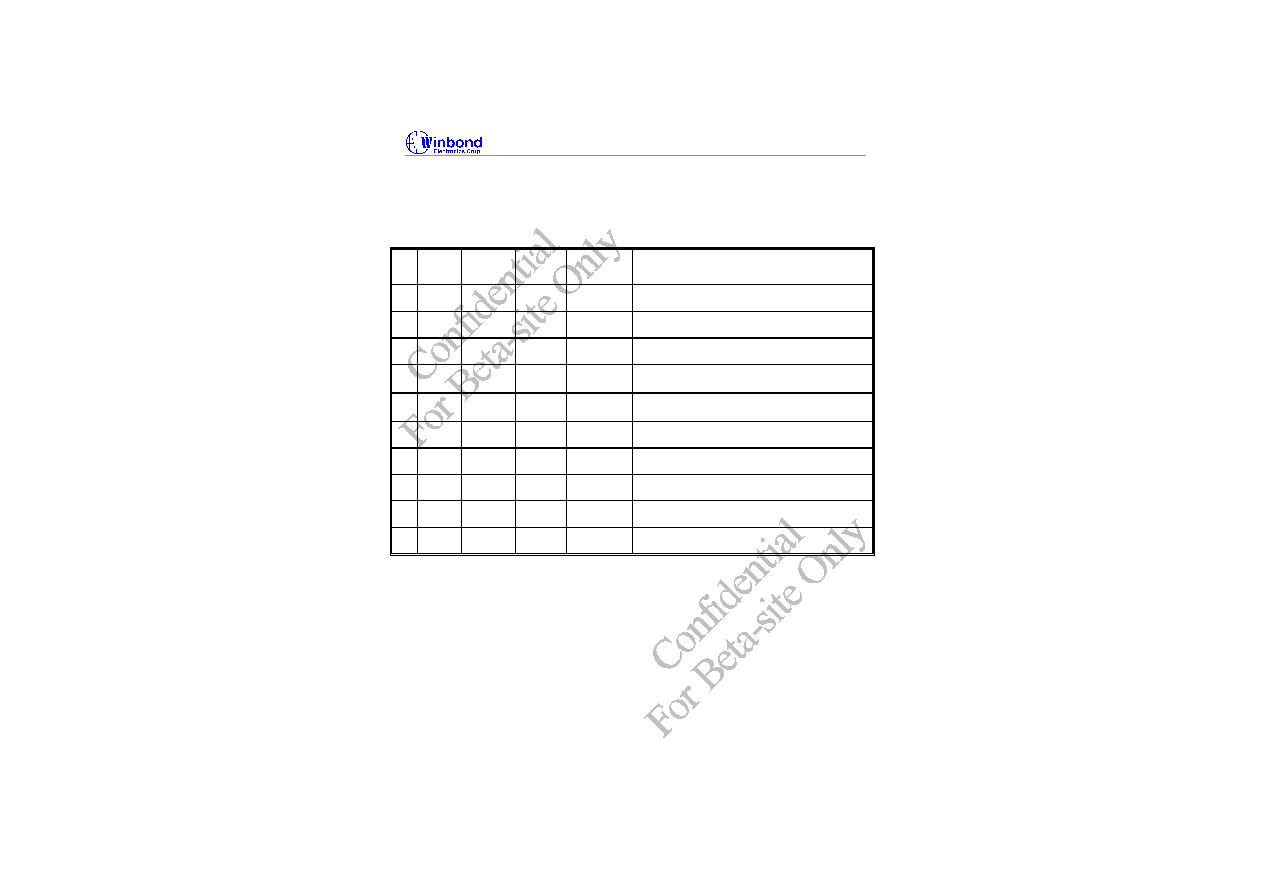

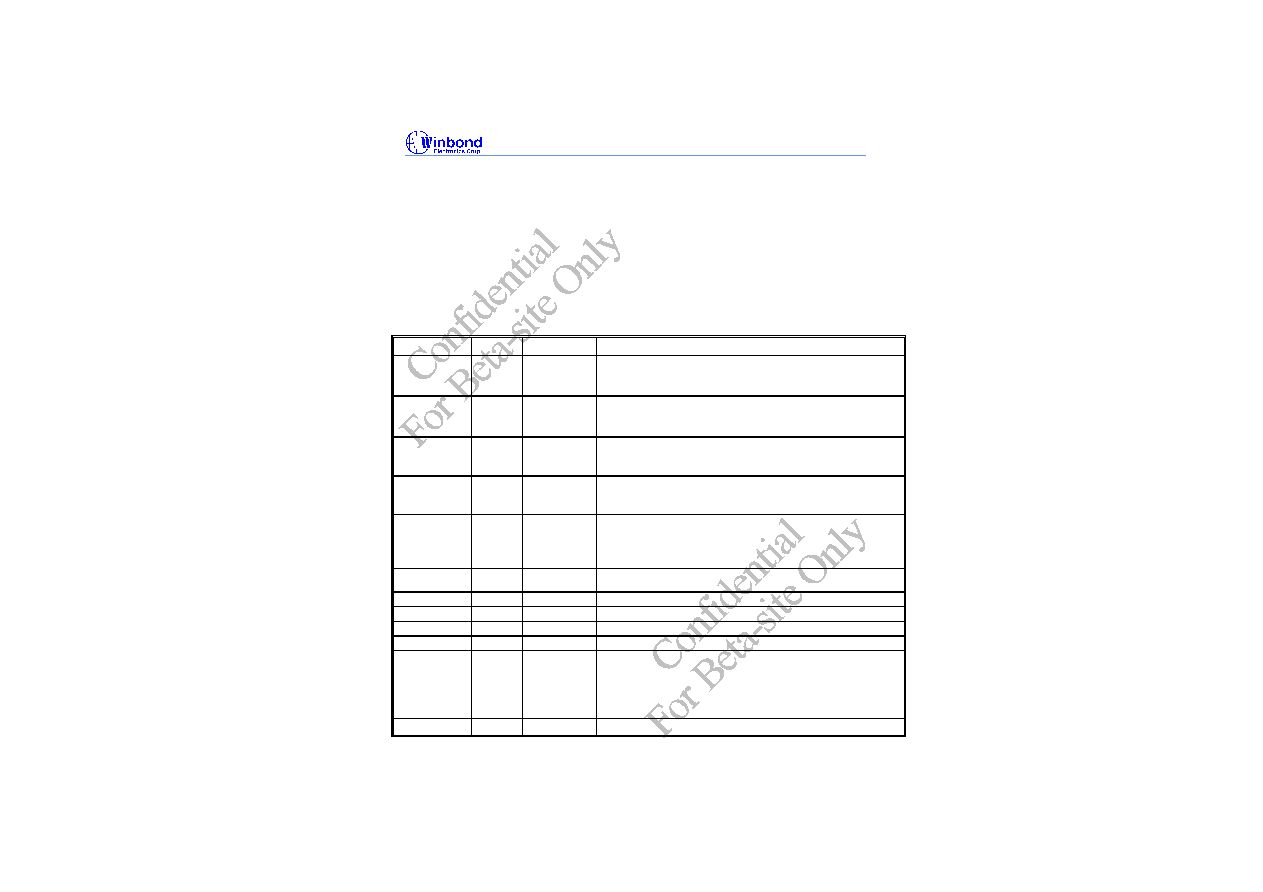

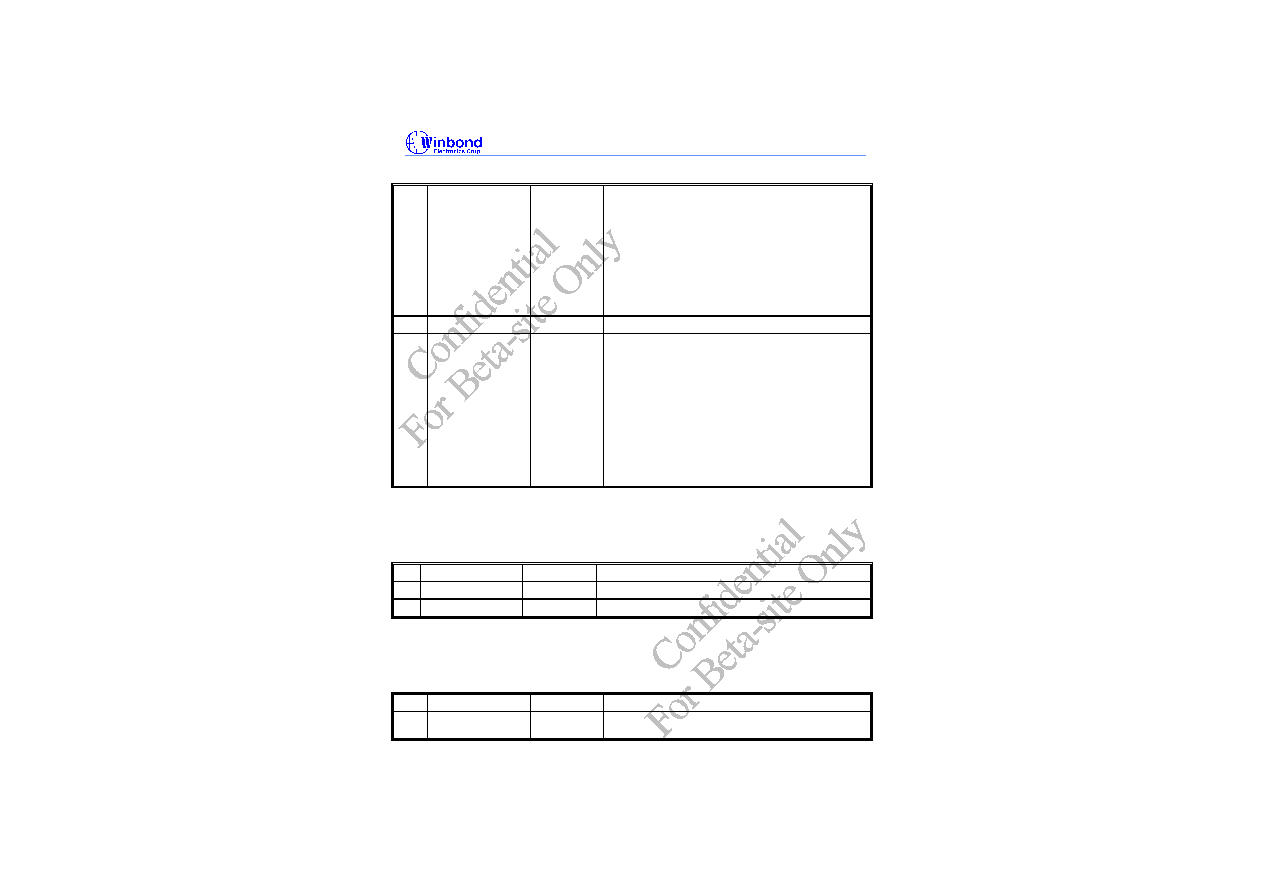

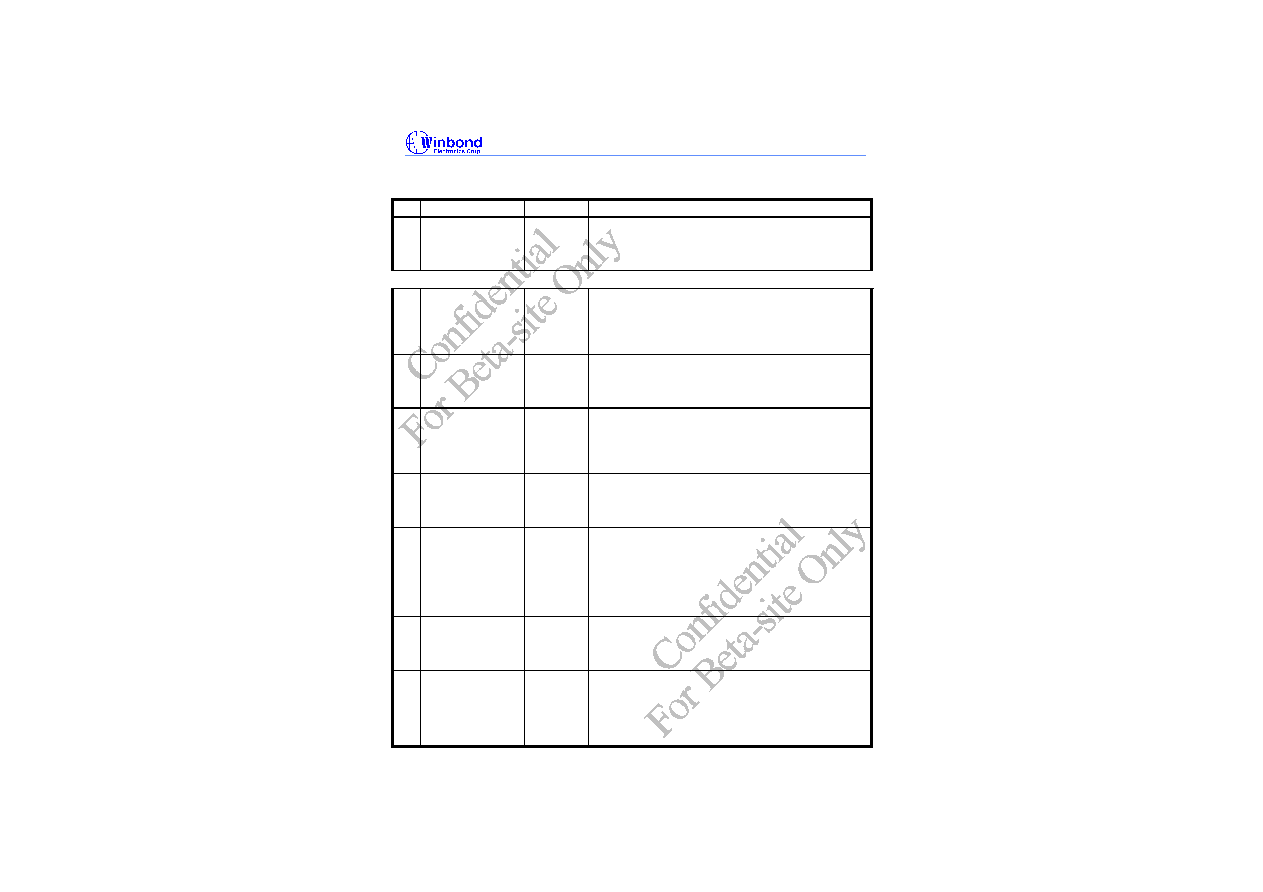

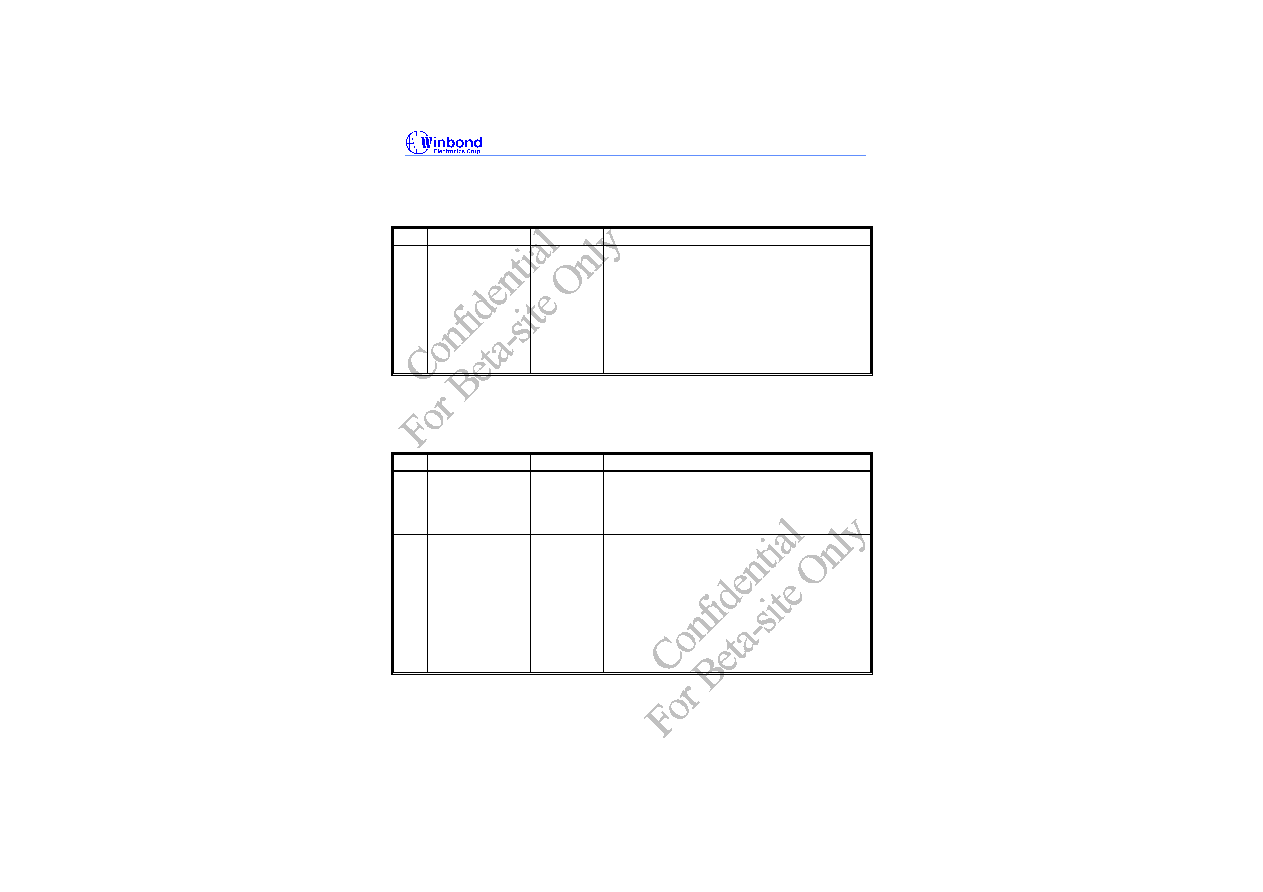

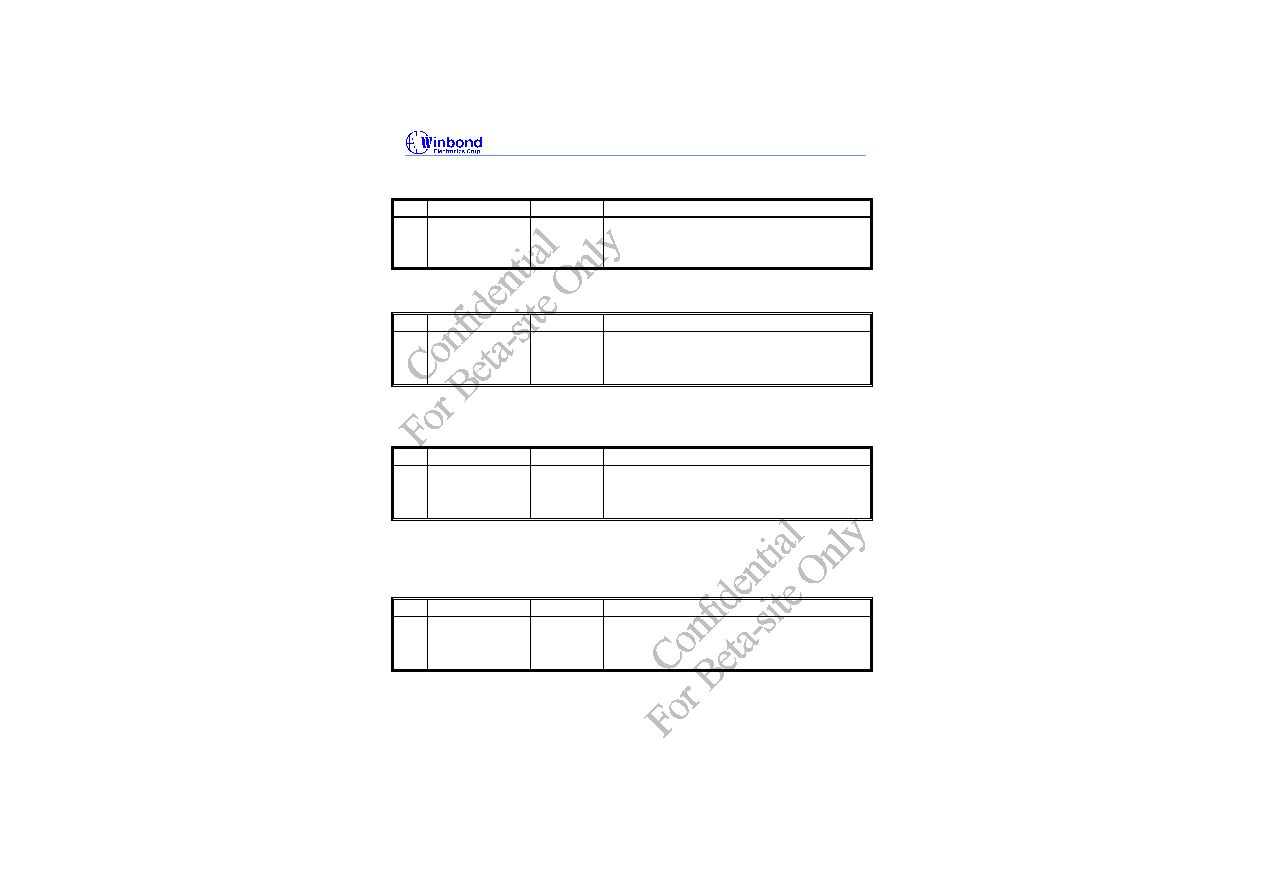

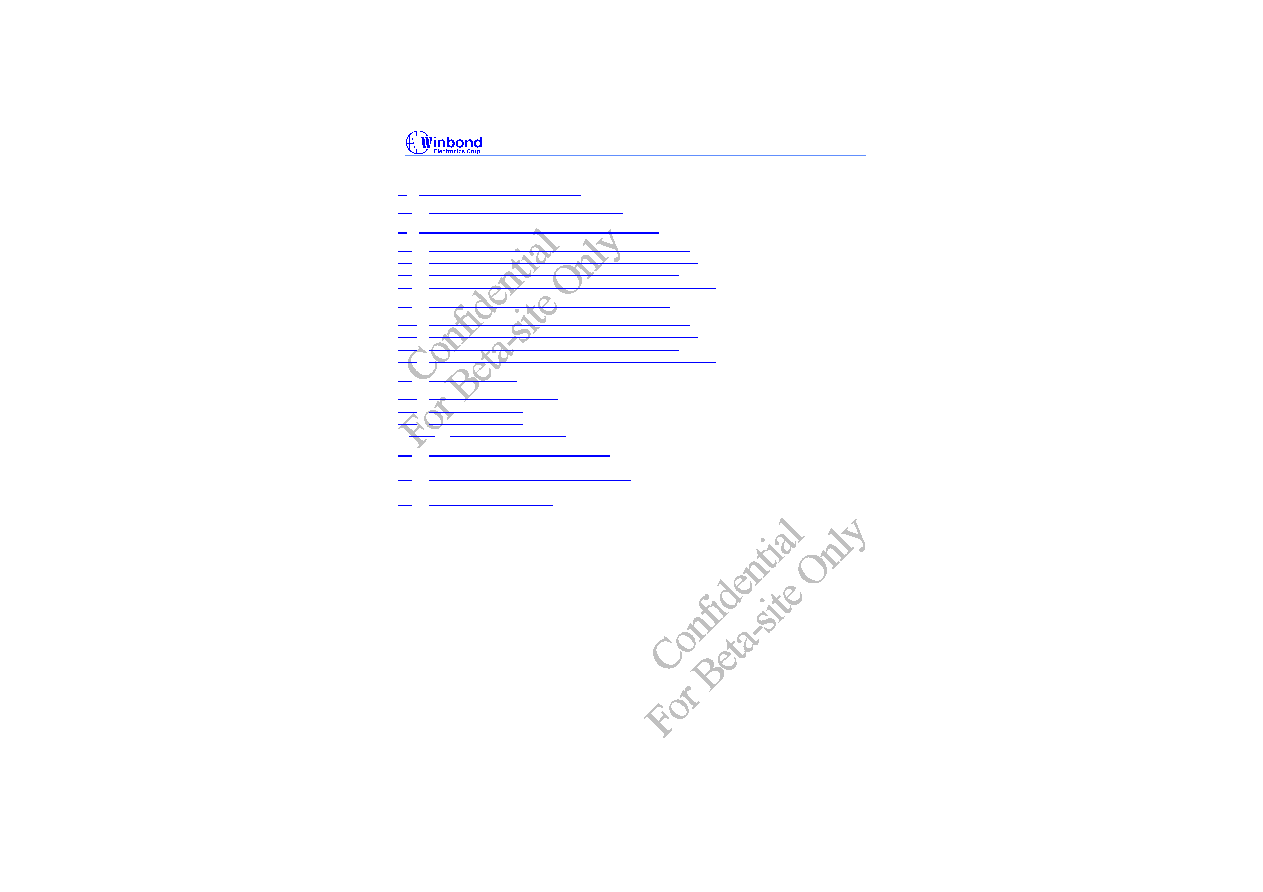

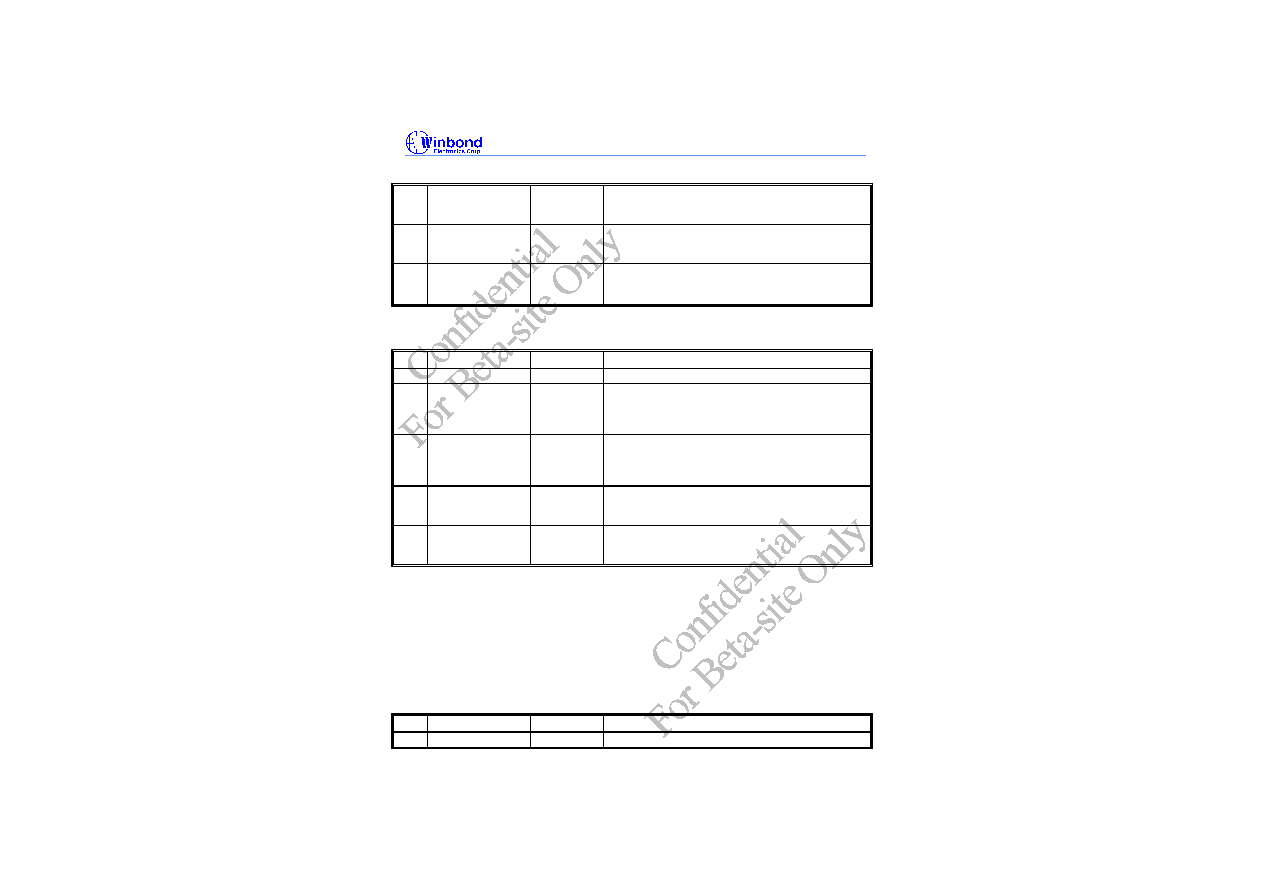

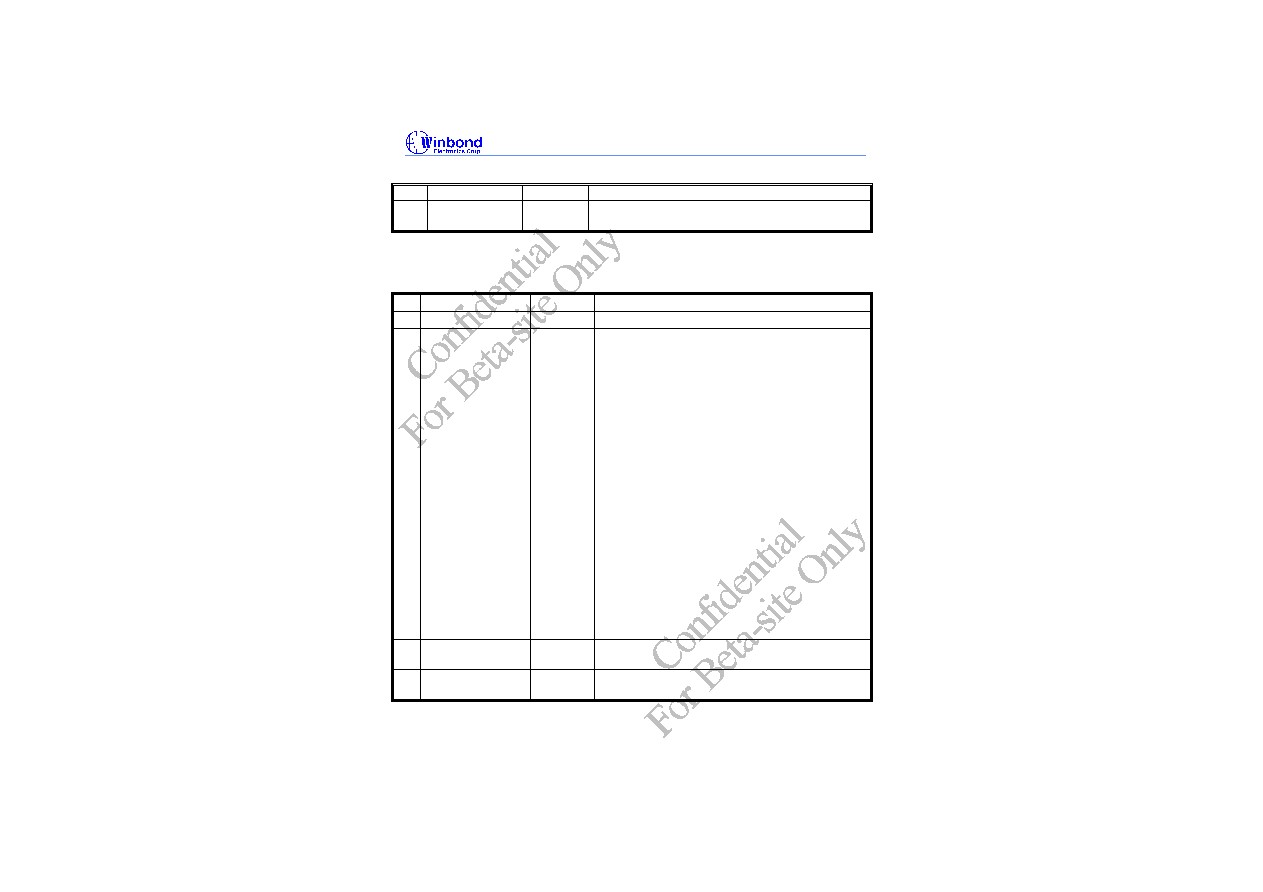

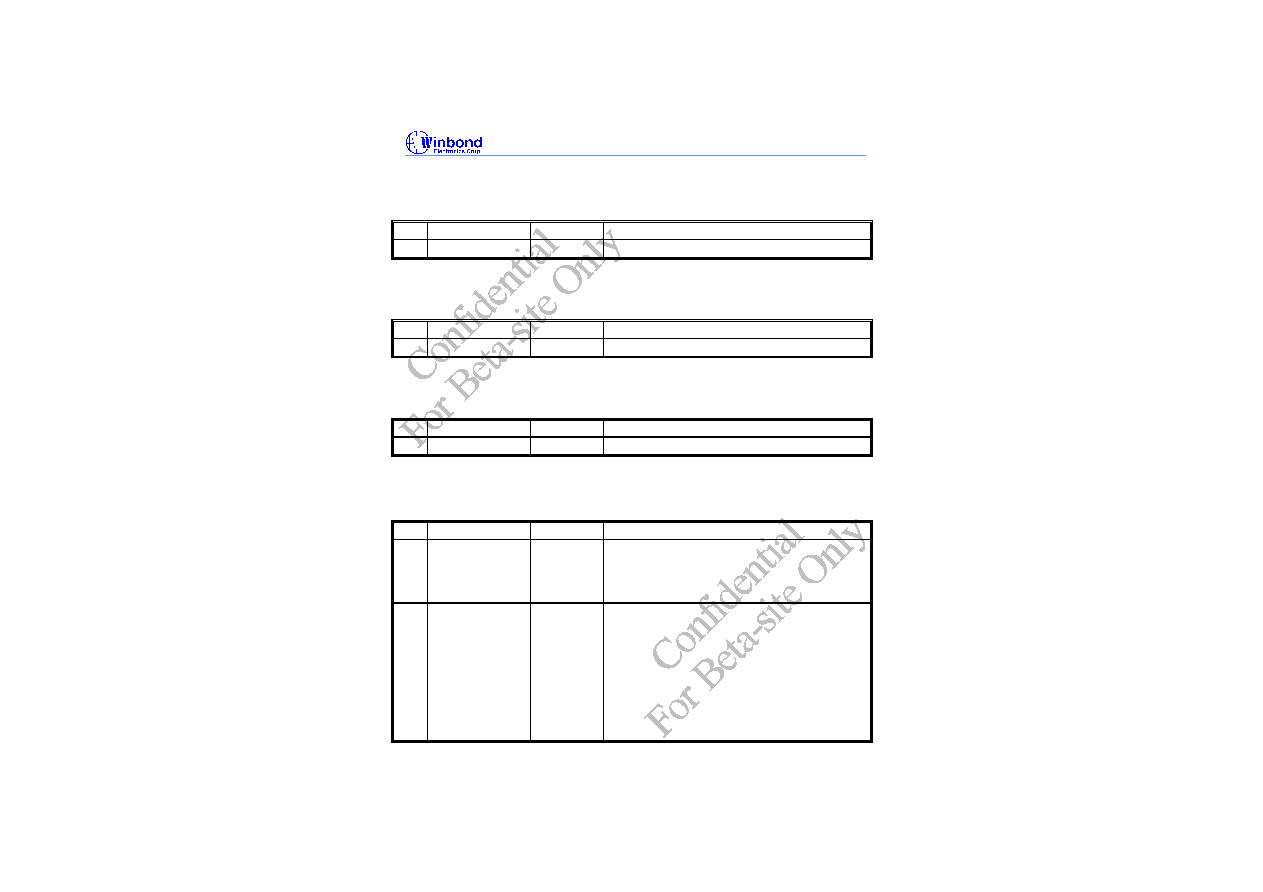

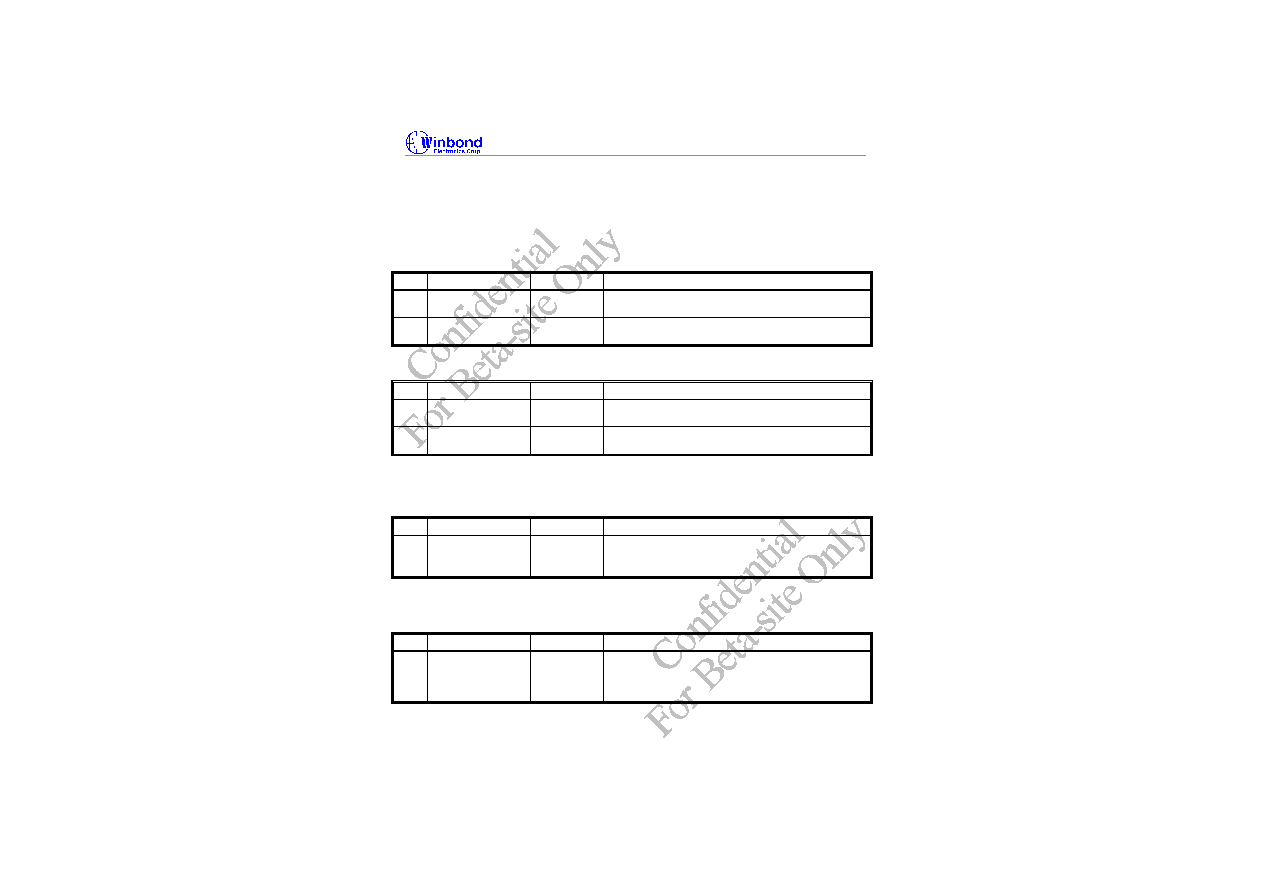

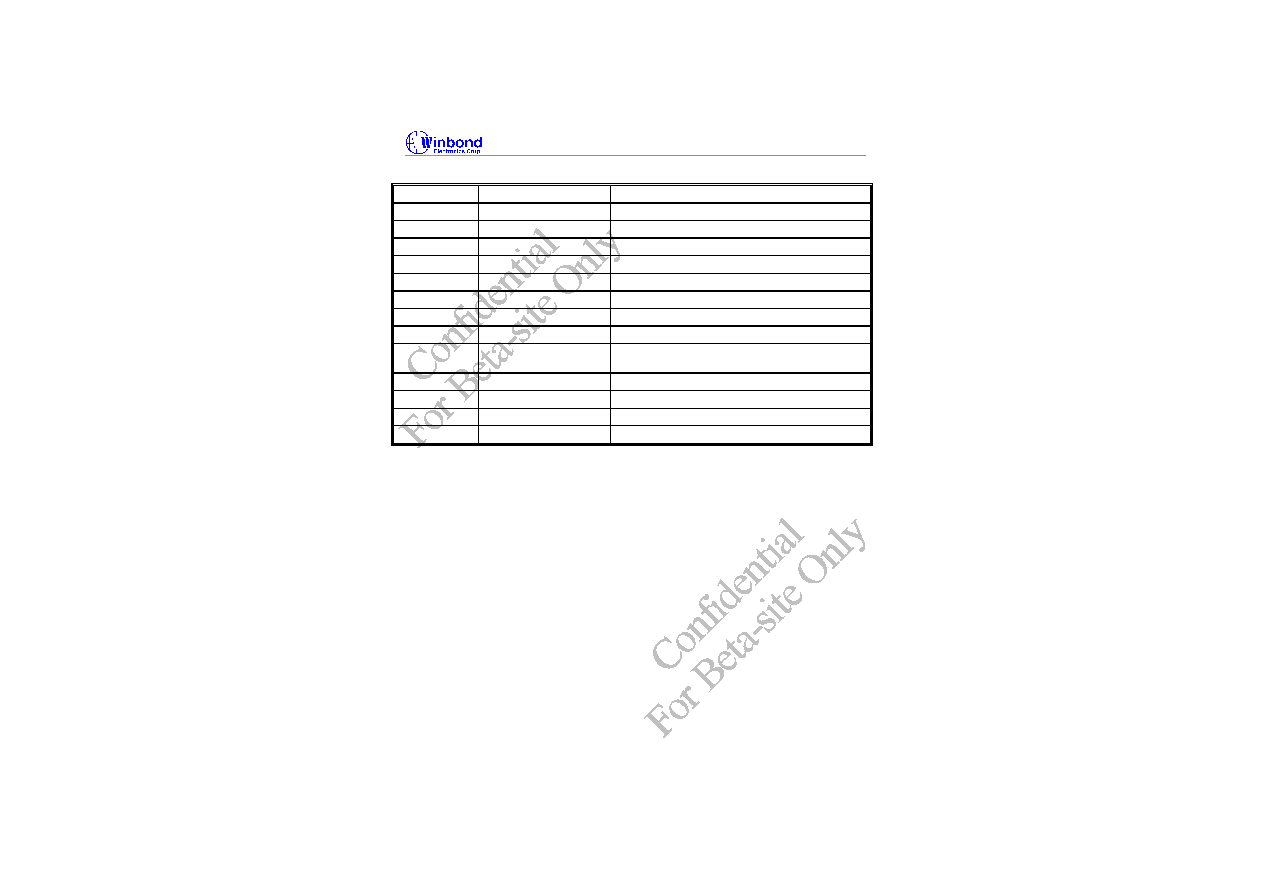

Data Sheet Revision History

Pages

Dates

Version

Version

on Web

Main Contents

1

n.a.

n.a.

All the version before 0.50 are for internal use.

2

n.a.

99/4

0.5

n.a.

First publication.

3

P.55

99/6

0.52

n.a.

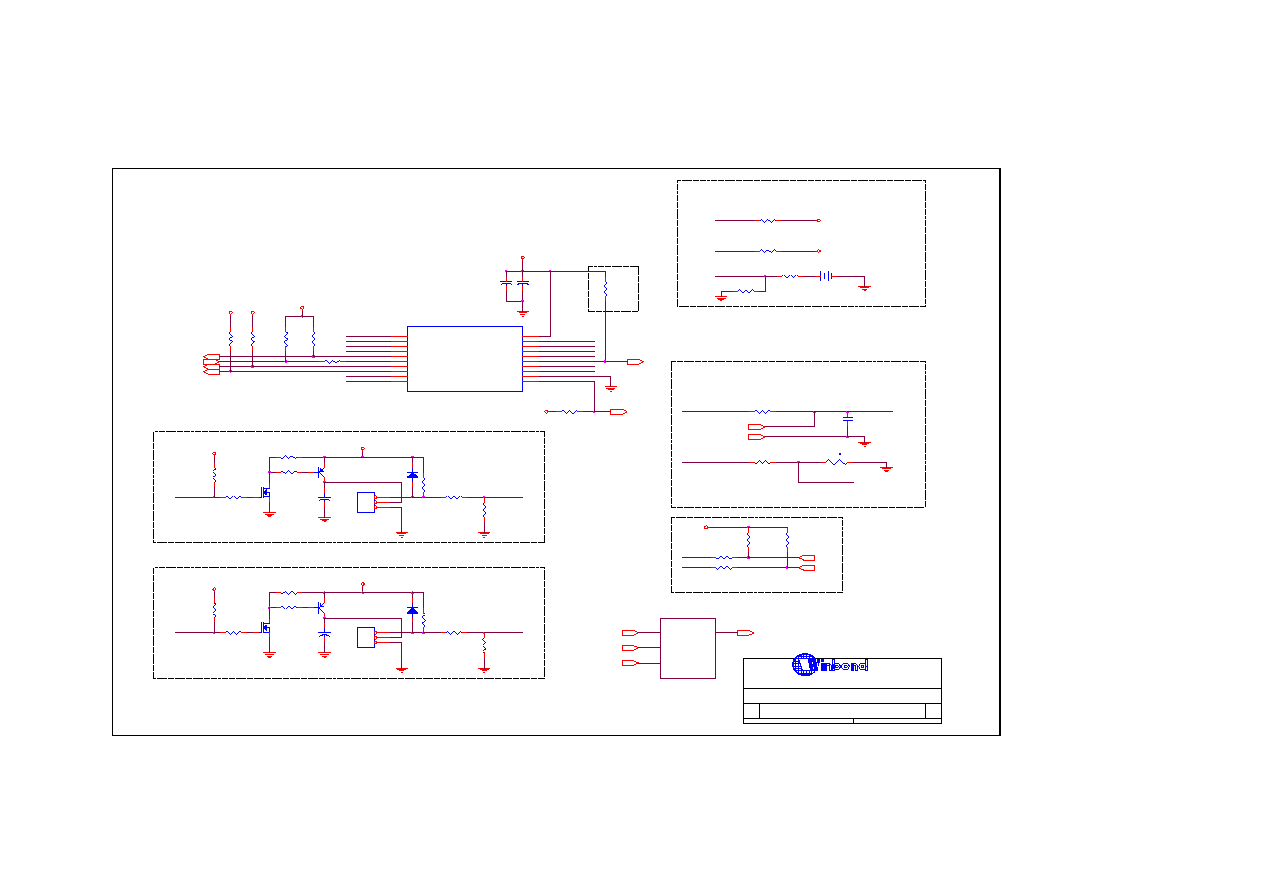

Schematics updated

4

P.54

99/6

0.53

n.a.

Corrected the length (D) from 10.2mm to 7.2mm

in the package outline table.

5

P.56

99/9

0.54

n.a.

Updated V0.5 schematics adding pull-high

resistors for RESET# (pin15)

6

7

8

9

10

Please note that all data and specifications are subject to change without notice. All

the trade marks of products and companies mentioned in this data sheet belong to

their respective owners.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or

systems where malfunction of these products can reasonably be expected to result

in personal injury. Winbond customers using or selling these products for use in

such applications do so at their own risk and agree to fully indemnify Winbond for

any damages resulting from such improper use or sales.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-2 - Revision 0.54

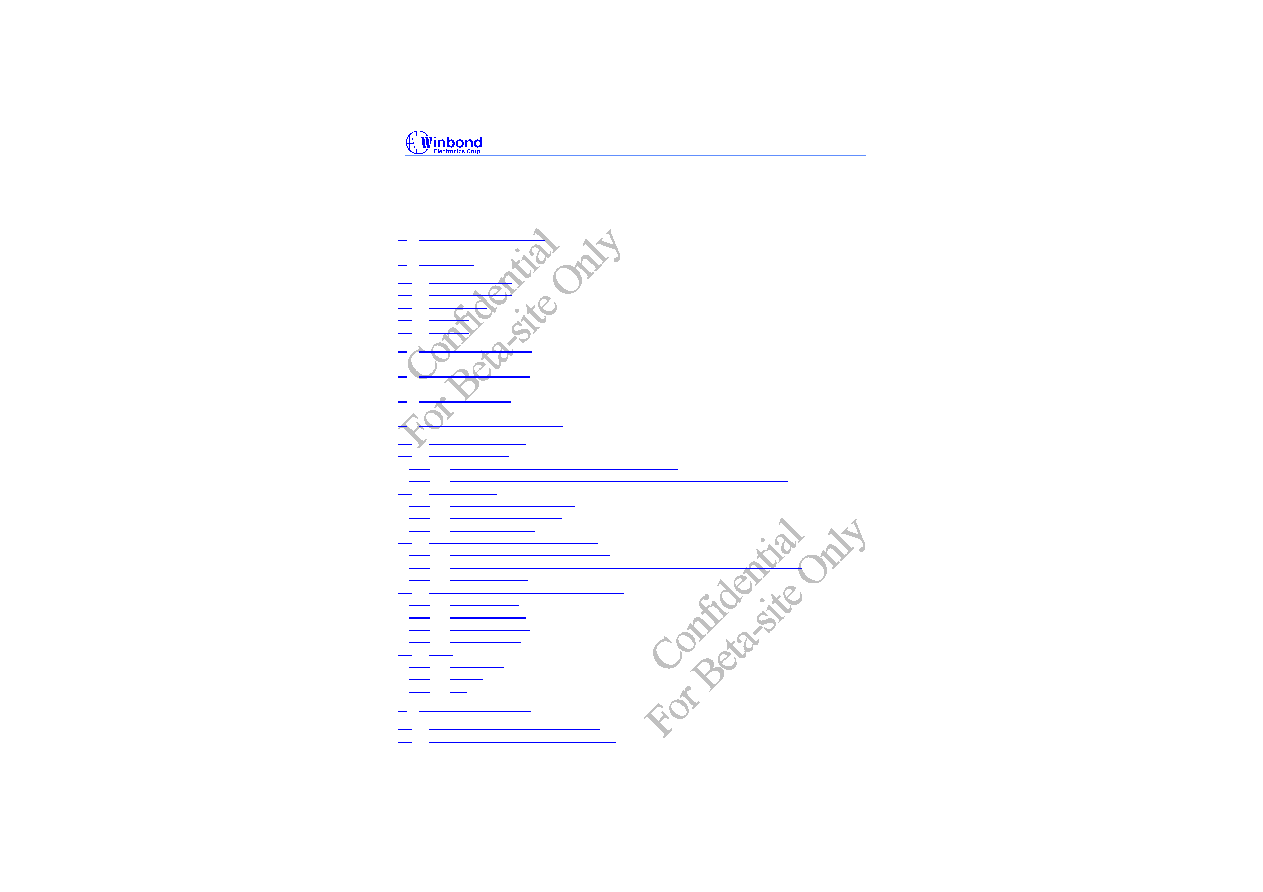

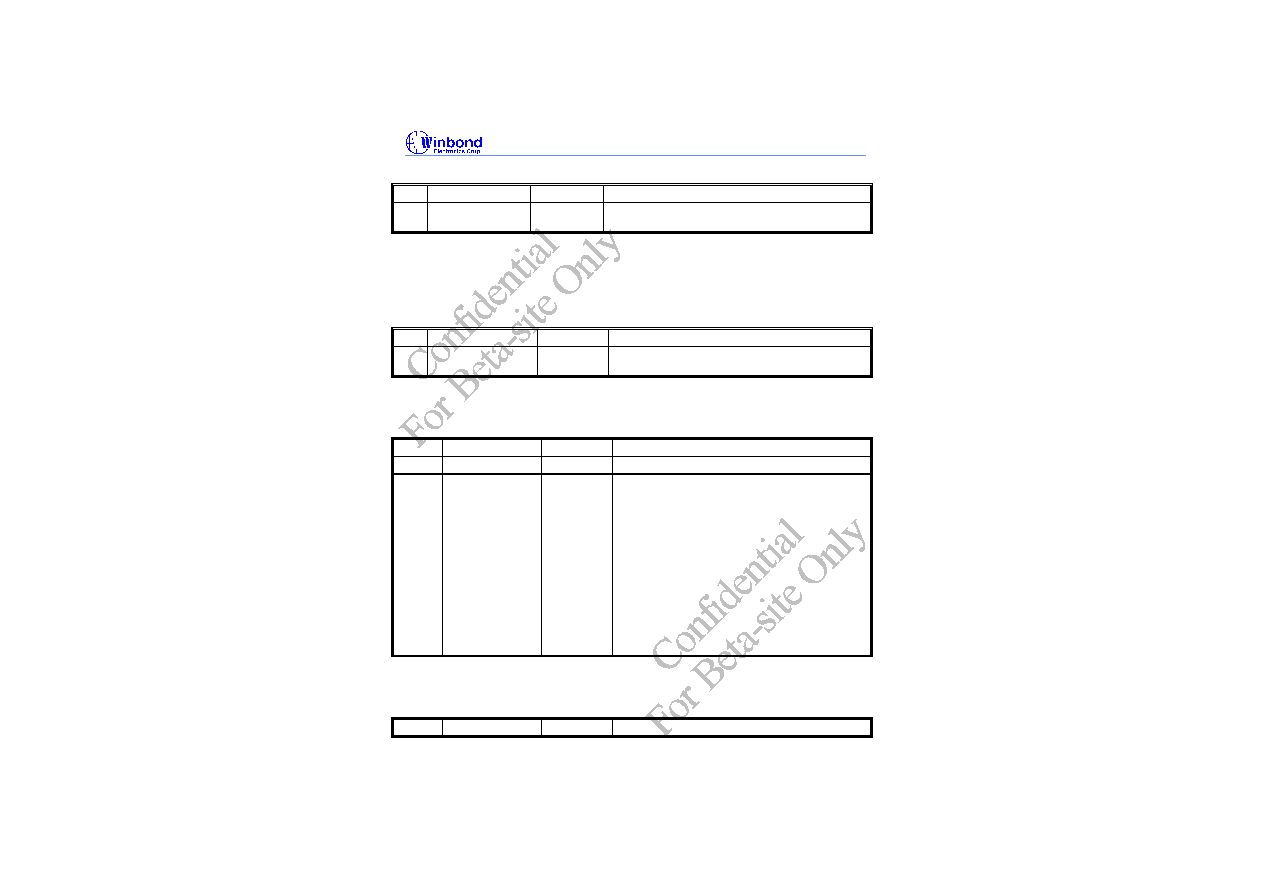

TABLE OF CONTENTS

1.

GENERAL DESCRIPTION

....................................................................................................................5

2.

FEATURES

..............................................................................................................................................6

2.1

M

ONITORING

I

TEMS

................................................................................................................................6

2.2

A

CTIONS

E

NABLING

................................................................................................................................6

2.3

P

OWER

G

OOD

.........................................................................................................................................6

2.4

G

ENERAL

...............................................................................................................................................6

2.5

P

ACKAGE

................................................................................................................................................6

3.

KEY SPECIFICATIONS

........................................................................................................................7

4.

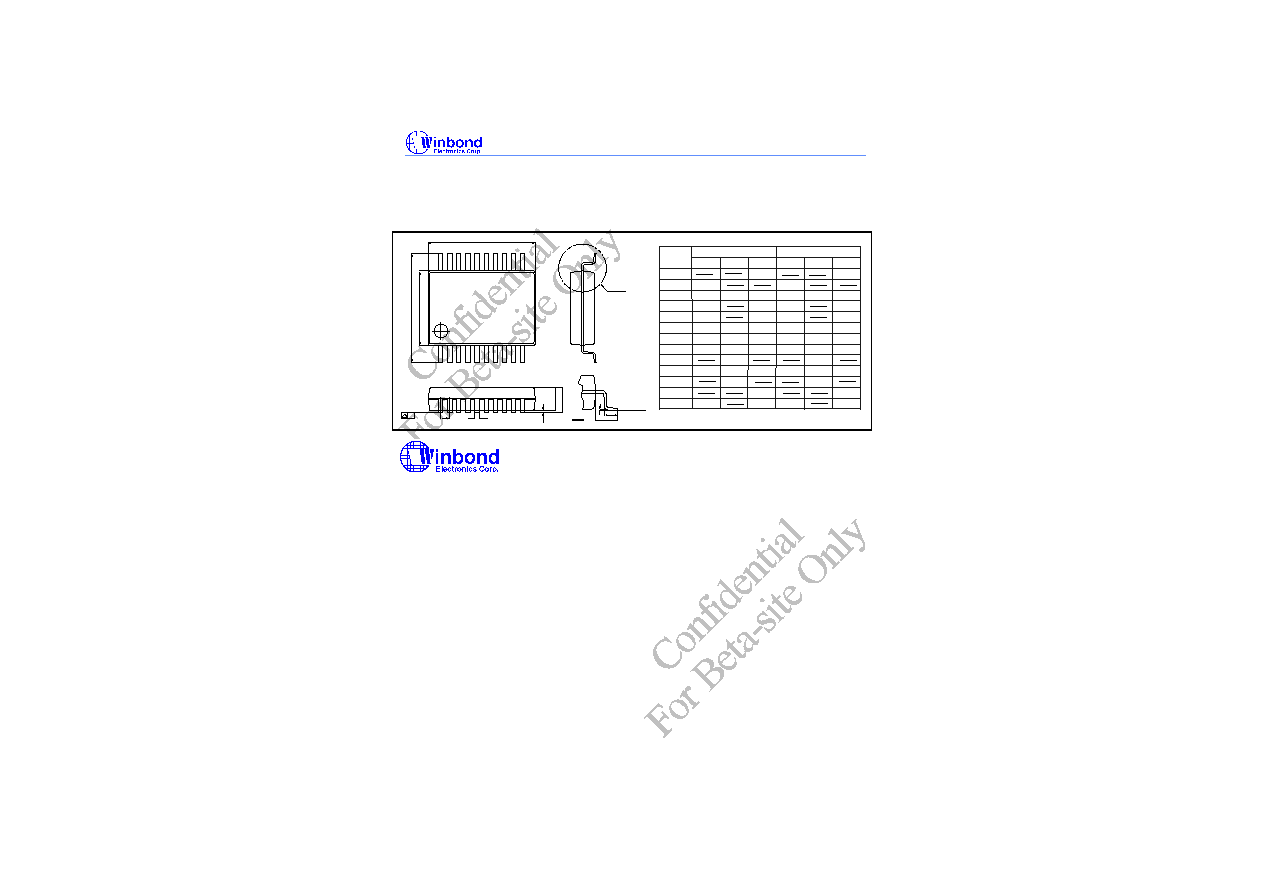

PIN CONFIGURATION

.........................................................................................................................7

5.

PIN DESCRIPTION

................................................................................................................................8

6.

FUNCTIONAL DESCRIPTION

...........................................................................................................10

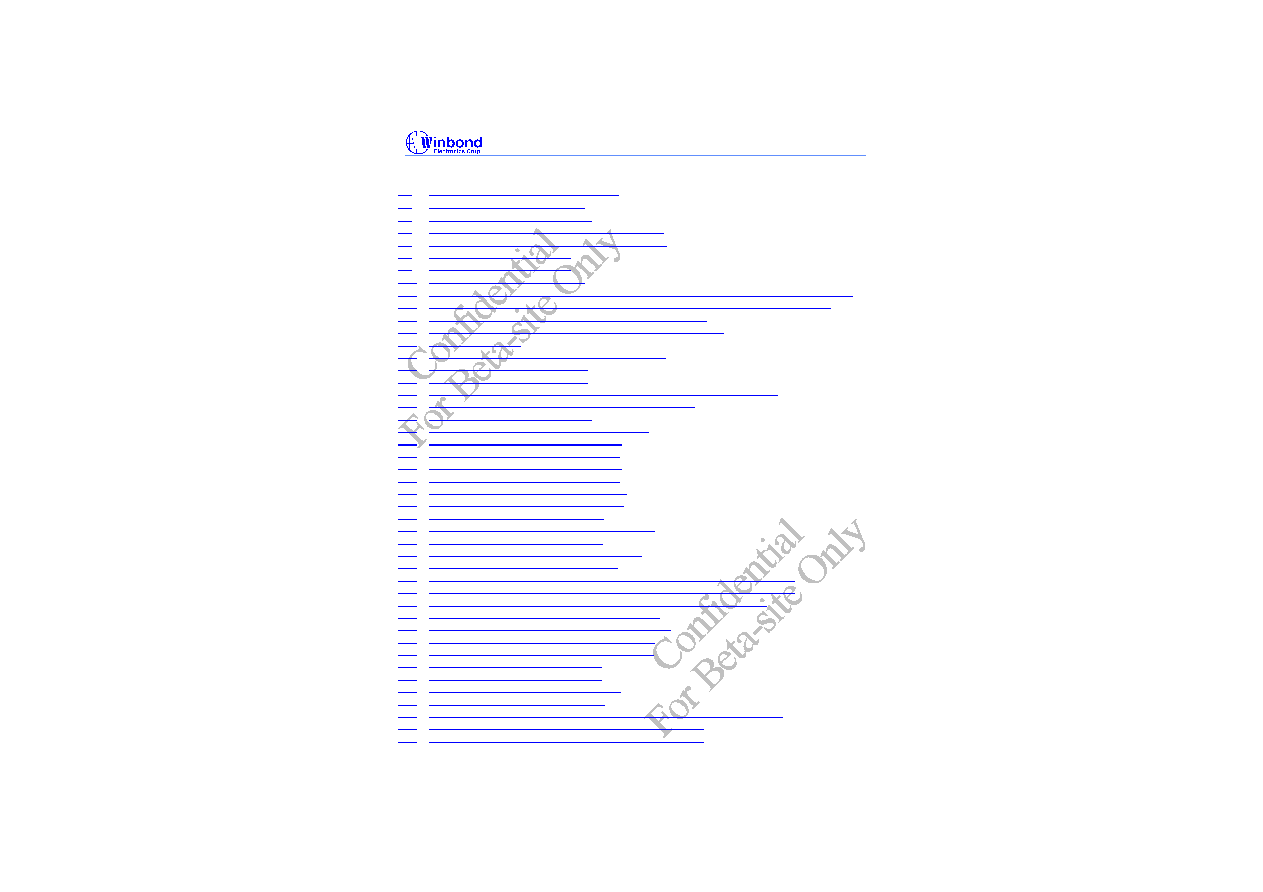

6.1

G

ENERAL

D

ESCRIPTION

.........................................................................................................................10

6.2

A

CCESS

I

NTERFACE

...............................................................................................................................10

6.2.1

The first serial bus access timing are shown as follow:

.................................................................10

6.2.2

The serial bus timing of the temperature CPUT1 and CPUT2 is shown as follow:

........................11

6.3

A

NALOG

I

NPUTS

...................................................................................................................................15

6.3.1

Monitor over 4.096V voltage:

......................................................................................................15

6.3.2

Power good for 3V and 5V

...........................................................................................................16

6.3.3

Battery Fault Alarm

.....................................................................................................................17

6.4

T

EMPERATURE

M

EASUREMENT

M

ACHINE

..............................................................................................17

6.4.1

Monitor temperature from thermistor:

..........................................................................................17

6.4.2

Monitor temperature from Pentium II

TM

thermal diode or bipolar transistor 2N3904

...................18

6.4.3

Over Temperature

........................................................................................................................18

6.5

FAN S

PEED

C

OUNT AND

FAN S

PEED

C

ONTROL

.....................................................................................20

6.5.1

Fan speed count

...........................................................................................................................20

6.5.2

Fan speed control

........................................................................................................................21

6.5.3

Smart Fan Control

.......................................................................................................................22

6.5.4

Fan Fault Alarm

..........................................................................................................................24

6.6

SMI#

...................................................................................................................................................24

6.6.1

Temperature

.................................................................................................................................24

6.6.2

Voltage

........................................................................................................................................26

6.6.3

Fan

..............................................................................................................................................26

7.

REGISTERS AND RAM

.......................................................................................................................27

7.1

C

ONFIGURATION

R

EGISTER

I

NDEX

40

H

..............................................................................................27

7.2

I

NTERRUPT

S

TATUS

R

EGISTER

1

I

NDEX

41

H

........................................................................................27

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-3 - Revision 0.54

7.3

I

NTERRUPT

S

TATUS

R

EGISTER

2

I

NDEX

42

H

.......................................................................................28

7.4

SMI M

ASK

R

EGISTER

1

I

NDEX

43

H

...................................................................................................28

7.5

SMI� M

ASK

R

EGISTER

2

I

NDEX

44

H

................................................................................................29

7.6

R

EAL

T

IME

H

ARDWARE

S

TATUS

R

EGISTER

I -- I

NDEX

45

H

......................................................................29

7.7

R

EAL

T

IME

H

ARDWARE

S

TATUS

R

EGISTER

II -- I

NDEX

46

H

.....................................................................30

7.8

R

ESERVED

R

EGISTER

-- I

NDEX

47

H

........................................................................................................30

7.9

R

ESERVED

R

EGISTER

-- I

NDEX

48

H

........................................................................................................30

7.10

F

AN

D

IVISOR

R

EGISTER

I

NDEX

49

H

...................................................................................................30

7.11

S

ERIAL

B

US

A

DDRESS

(

FOR

V

OLTAGE

,F

AN

,

AND INTERNAL TEMPERATURE

) R

EGISTER

A

DDRESS

4A

H

31

7.12

CPUT1 T

EMPERATURE AND

CPUT2 T

EMPERATURE

S

ERIAL

B

US

A

DDRESS

R

EGISTER

--I

NDEX

4B

H

.........31

7.13

W

INBOND

V

ENDOR

ID (L

OW

B

YTE

) - I

NDEX

4C

H

(A

UTO

I

NCREASE

)

......................................................32

7.14

W

INBOND

V

ENDOR

ID (H

IGH

B

YTE

) - I

NDEX

4D

H

(N

O

A

UTO

I

NCREASE

)

................................................32

7.15

C

HIP

ID -- I

NDEX

4E

H

...........................................................................................................................32

7.16

ACPI T

EMPERATURE

I

NCREMENT

R

EGISTER

-- I

NDEX

4F

H

.....................................................................32

7.17

OVT# P

ROPERTY

S

ELECT

- I

NDEX

50

H

..................................................................................................33

7.18

SMI# P

ROPERTY

S

ELECT

-- I

NDEX

51

H

..................................................................................................34

7.19

FANIN1/GPO1, FANIN2/GPO2

AND

BEEP/GPO3 C

ONTROL

R

EGISTER

- I

NDXE

52

H

............................34

7.20

CPUT1/CPUT2 T

HERMAL

S

ENSOR

T

YPE

R

EGISTER

-- I

NDEX

53

H

..........................................................36

7.21

M

ISC

C

ONTROL

R

EGISTER

-- I

NDEX

54

H

................................................................................................36

7.22

F

AN

/VBAT F

AULT

C

ONTROL

R

EGISTER

-- I

NDEX

55

H

............................................................................37

7.23

F

AN

1 F

AULT

H

IGH

L

IMIT

C

OUNT

-- I

NDEX

56

H

.....................................................................................37

7.24

F

AN

2 F

AULT

L

OW

L

IMIT

C

OUNT

-- I

NDEX

57

H

......................................................................................37

7.25

F

AN

2 F

AULT

H

IGH

L

IMIT

C

OUNT

-- I

NDEX

58

H

.....................................................................................37

7.26

F

AN

1 F

AULT

L

OW

L

IMIT

C

OUNT

-- I

NDEX

59

H

......................................................................................38

7.27

VBAT F

AULT

H

IGH

L

IMIT

V

ALUE

-- I

NDEX

5A

H

....................................................................................38

7.28

VBAT F

AULT

L

OW

L

IMIT

V

ALUE

-- I

NDEX

5B

H

.....................................................................................38

7.29

FAN 1 P

RE

-S

CALE

R

EGISTER

-- I

NDEX

80

H

............................................................................................38

7.30

FAN 1 D

UTY

C

YCLE

S

ELECT

R

EGISTER

-- 81

H

(

B

ANK

0)

.........................................................................39

7.31

FAN 2 P

RE

-S

CALE

R

EGISTER

--

I

NDEX

82

H

............................................................................................39

7.32

FAN2 D

UTY

C

YCLE

S

ELECT

R

EGISTER

-- I

NDEX

83

H

..............................................................................40

7.33

FAN C

ONFIGURATION

R

EGISTER

-- I

NDEX

84

H

.......................................................................................40

7.34

CPUT1 T

ARGET

T

EMPERATURE

R

EGISTER

/ F

AN

1 T

ARGET

S

PEED

R

EGISTER

-- I

NDEX

85

H

......................41

7.35

CPUT2 T

ARGET

T

EMPERATURE

R

EGISTER

/ F

AN

2 T

ARGET

S

PEED

R

EGISTER

-- I

NDEX

86

H

......................41

7.36

T

OLERANCE OF

T

ARGET

T

EMPERATURE OR

T

ARGET

S

PEED

R

EGISTER

-- I

NDEX

87

H

................................42

7.37

F

AN

1 PWM S

TOP

D

UTY

C

YCLE

R

EGISTER

-- I

NDEX

88

H

.......................................................................42

7.38

F

AN

2 PWM S

TOP

D

UTY

C

YCLE

R

EGISTER

-- 89

H

(

B

ANK

0)

....................................................................42

7.39

F

AN

1 S

TART

-

UP

D

UTY

C

YCLE

R

EGISTER

-- I

NDEX

8A

H

.........................................................................42

7.40

F

AN

2 S

TART

-

UP

D

UTY

C

YCLE

R

EGISTER

-- I

NDEX

8B

H

..........................................................................43

7.41

F

AN

1 S

TOP

T

IME

R

EGISTER

-- I

NDXE

8C

H

.............................................................................................43

7.42

F

AN

2 S

TOP

T

IME

R

EGISTER

-- I

NDEX

8D

H

.............................................................................................43

7.43

F

AN

S

TEP

D

OWN

T

IME

R

EGISTER

-- I

NDEX

8E

H

......................................................................................43

7.44

F

AN

S

TEP

U

P

T

IME

R

EGISTER

-- I

NDEX

8F

H

............................................................................................44

7.45

T

EMPERATURE

S

ENSOR

1 (I

NTERNAL

T

HERMAL

D

IODE

) O

FFSET

R

EGISTER

- I

NDEX

90

H

..........................44

7.46

T

EMPERATURE

S

ENSOR

2 (CPU T1) O

FFSET

R

EGISTER

- I

NDEX

91

H

.......................................................44

7.47

T

EMPERATURE

S

ENSOR

3 (CPU T2) O

FFSET

R

EGISTER

- I

NDEX

92

H

.......................................................45

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-4 - Revision 0.54

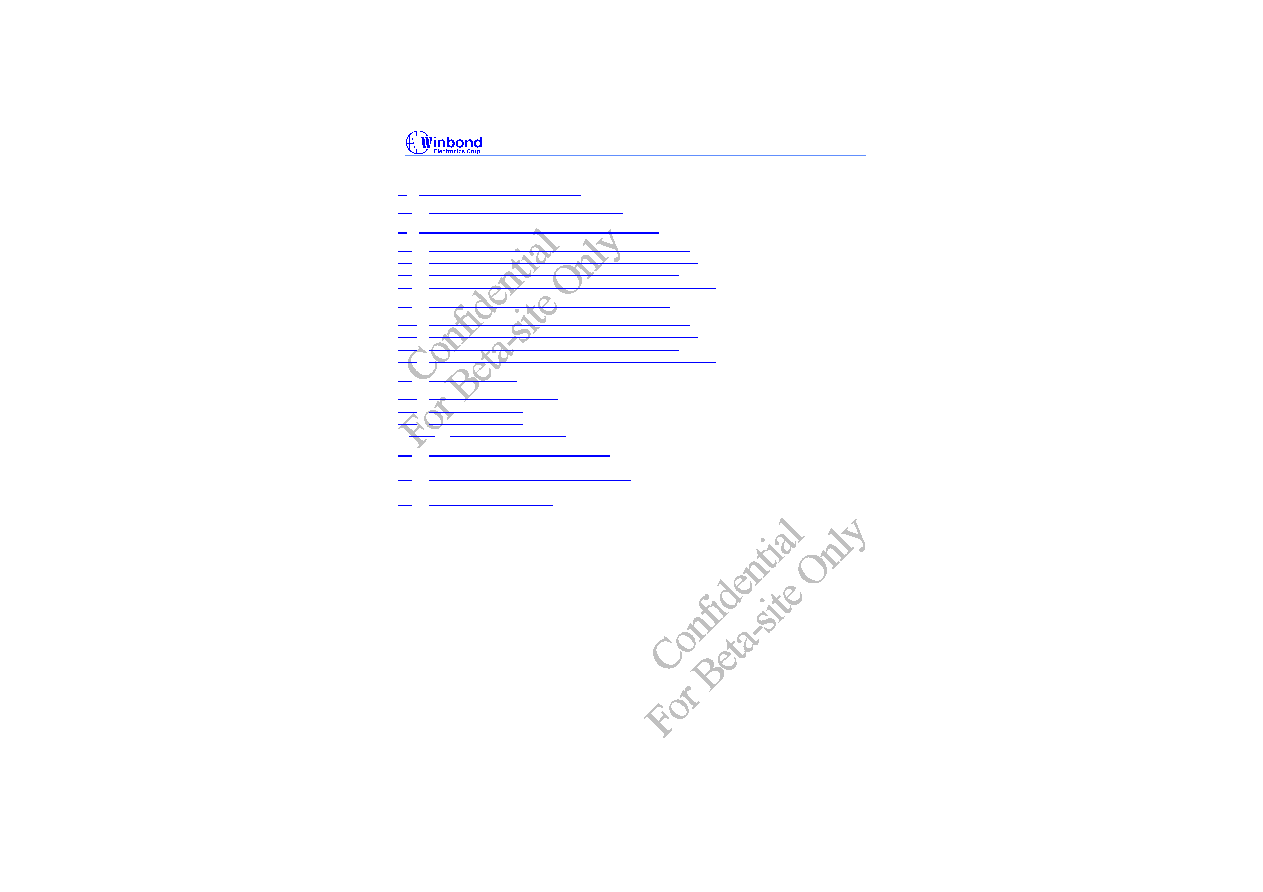

8.

VALUE RAM AND LIMIT VALUE

....................................................................................................46

8.1

V

ALUE

RAM

I

NDEX

20

H

- 3F

H OR

60

H

- 7F

H

.....................................................................................46

9.

TEMPERATURE SENSOR 2 (CPU T1) REGISTERS

........................................................................48

9.1

T

EMPERATURE

S

ENSOR

2 T

EMPERATURE

R

EGISTER

- I

NDEX

00

H

............................................................48

9.2

T

EMPERATURE

S

ENSOR

2 C

ONFIGURATION

R

EGISTER

- I

NDEX

01

H

.........................................................48

9.3

T

EMPERATURE

S

ENSOR

2 H

YSTERESIS

R

EGISTER

- I

NDEX

02

H

................................................................48

9.4

T

EMPERATURE

S

ENSOR

2 O

VER

-

TEMPERATURE

R

EGISTER

- I

NDEX

03

H

...................................................48

10.

TEMPERATURE SENSOR 3 (CPU T2) REGISTERS

....................................................................49

10.1

T

EMPERATURE

S

ENSOR

3 T

EMPERATURE

R

EGISTER

- I

NDEX

00

H

............................................................49

10.2

T

EMPERATURE

S

ENSOR

3 C

ONFIGURATION

R

EGISTER

- I

NDEX

01

H

.........................................................49

10.3

T

EMPERATURE

S

ENSOR

3 H

YSTERESIS

R

EGISTER

- I

NDEX

02

H

................................................................49

10.4

T

EMPERATURE

S

ENSOR

3 O

VER

-

TEMPERATURE

R

EGISTER

- I

NDEX

03

H

...................................................49

11.

SPECIFICATIONS

............................................................................................................................50

11.1

A

BSOLUTE

M

AXIMUM

R

ATINGS

.............................................................................................................50

11.2

DC C

HARACTERISTICS

..........................................................................................................................50

11.3

AC C

HARACTERISTICS

..........................................................................................................................52

11.3.1

Serial Bus Timing Diagram

..........................................................................................................52

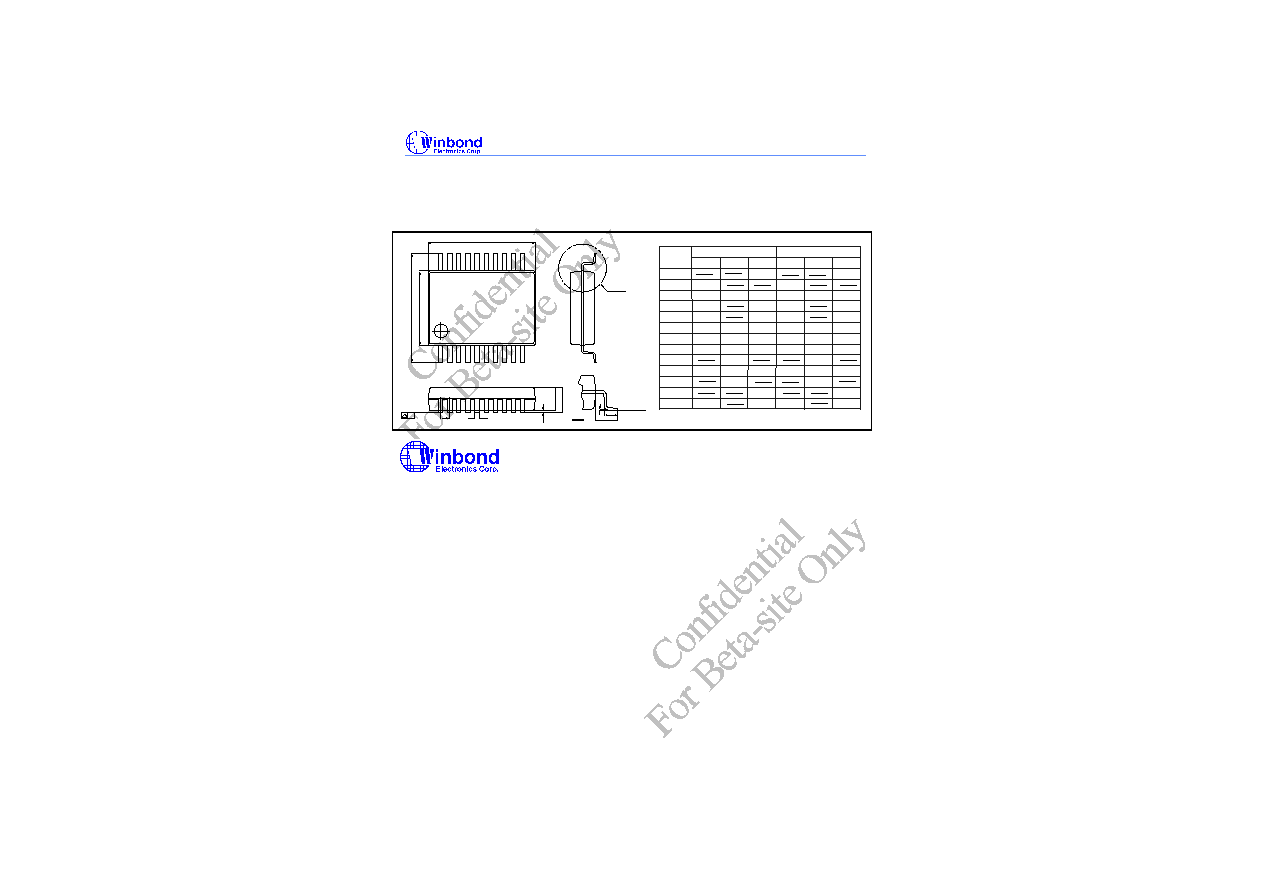

12.

HOW TO READ THE TOP MARKING

..........................................................................................53

13.

PACKAGE DRAWING AND DIMENSIONS

..................................................................................54

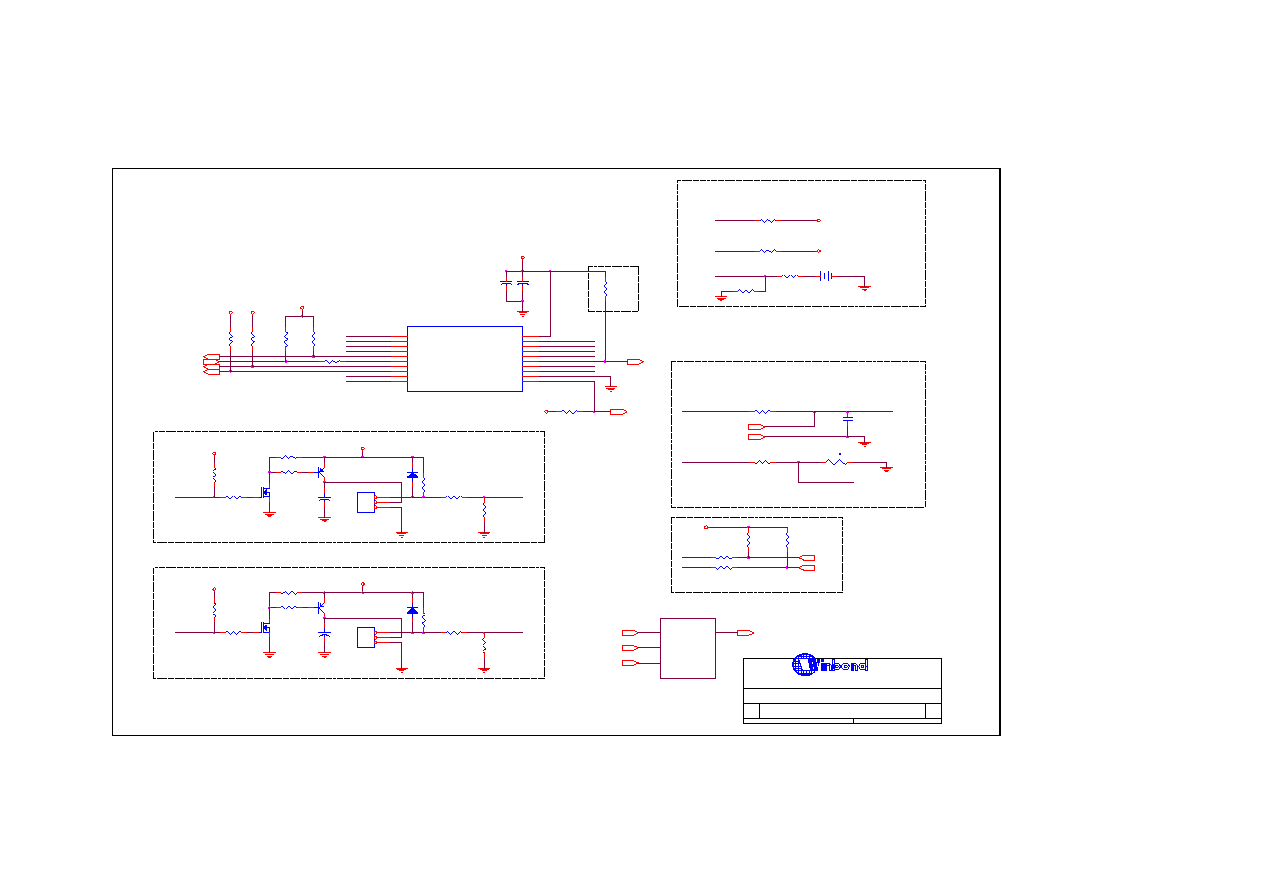

14.

W83L784R SCHEMATICS

...............................................................................................................55

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-5 - Revision 0.54

1. GENERAL DESCRIPTION

W83L784R is an evolving product of W83782D --- Winbond's most popular hardware status

monitoring IC. Specifically designed for the Notebook system, W83L784R can be used to monitor

several critical hardware parameters of the system, including power supply voltages, fan speeds, and

temperatures, which are very important for a high-end Notebook system to work stably and properly.

An 8-bit analog-to-digital converter (ADC) was built inside W83L784R. The W83L784R can

monitor 4 analog voltage inputs, 2 fan tachometer inputs, one on-chip internal temperature sensor

and 2 remote temperature sensors. The remote temperature sensing can be performed by

thermistors, or 2N3904 NPN-type transistors, or directly from Intel

TM

Deschutes CPU thermal diode

output. The W83L784R provides 2 PWM (pulse width modulation) outputs for the fan speed control

to support the

}

Thermal Cruise

TM

~

system, which can maintain the CPU or system in the specific

programmable temperature under the hardware control. Another Fan speed control mode is

}

Speed

Cruise

}

to Keep the fan operating in the specific r.p.m.. On the other hand,

the W83L784R provides

low active outputs such as fan fault and Battery low which could issue the hardware warning signals

when the fan speed or battery voltage drop out of the preset range. Also the W83L784R provides:

power good reset for 3V and 5V; power down mode for power saving; fault pin for necessary H/W

shutdown control; SMI#, OVT#, GPO# signals for system protection events; I

2

C

TM

serial bus interface.

Through the application software or BIOS, the users can read all the monitored parameters of

system from time to time. And a pop-up warning can be also activated when the monitored item was

out of the proper/preset range. The application software could be Winbond's Hardware Doctor

TM

, or

Intel

TM

LDCM (LanDesk Client Management), or other management application software. Also the

users can set up the upper and lower limits (alarm thresholds) of these monitored parameters and to

activate one programmable and maskable interrupts. For the spacing saving consideration of the

Notebook system, W83L784R is in the package of 209mil 20pins-SSOP.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-6 - Revision 0.54

2. FEATURES

2.1 Monitoring Items

�

2 thermal inputs from remote thermistors or 2N3904 NPN-type transistors or Pentium

TM

II

(Deschutes) thermal diode output

�

One on-chip temperature detection

�

4 voltage inputs

--- typical for Vcore, +3.3V, +5V, Battery

�

2 sets of fan speed control and fan speed monitoring input

�

WATCHDOG comparison of all monitored values

�

Programmable hysteresis and setting points (alarm thresholds) for all monitored items

2.2 Actions Enabling

�

Issue fan fault signal as fans are abnomally stopped

�

Issue battery low signal as bettery voltage is abnomally out of range

�

2 PWM (pulse width modulation) outputs for fan speed control to support

}

Thermal Cruise

TM

~

or

}

Speed Cruise

TM

~

--- Automatically maintain the CPU or system in the specific temperature or keep the fans in the

specific speed under the H/W control

�

Issue SMI#, OVT#, GPO to activate system protection

�

PWR_DN# setting for the Power down mode

�

Warning signal pop-up in application software

2.3 Power Good

�

Issue RESET# outputs as the Power Good signal when 3V and 5V rise across a reset threshold.

2.4 General

�

I

2

C

TM

serial bus interface

�

Intel

TM

LDCM (DMI driver 2.0) support

�

Acer

TM

ADM (DMI driver 2.0) support

�

Winbond hardware monitoring application software (Hardware Doctor

TM

) support, for both

Windows 95/98

�

Meet WfM 2.0 (Wired for Management) spec.

�

5V Vcc operation

2.5 Package

�

20-pin SSOP (209mil)

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-7 - Revision 0.54

3. KEY SPECIFICATIONS

�

Voltage monitoring accuracy

�

1% (Max)

�

Monitoring Temperature Range and Accuracy

- 40

�

C to +120

�

C

�

3

�

C(Max)

�

Supply Voltage 5V

�

Operating Supply Current 2 mA typ.

�

Power Down Suppy Current 10 uA typ.

�

ADC Resolution 8 Bits

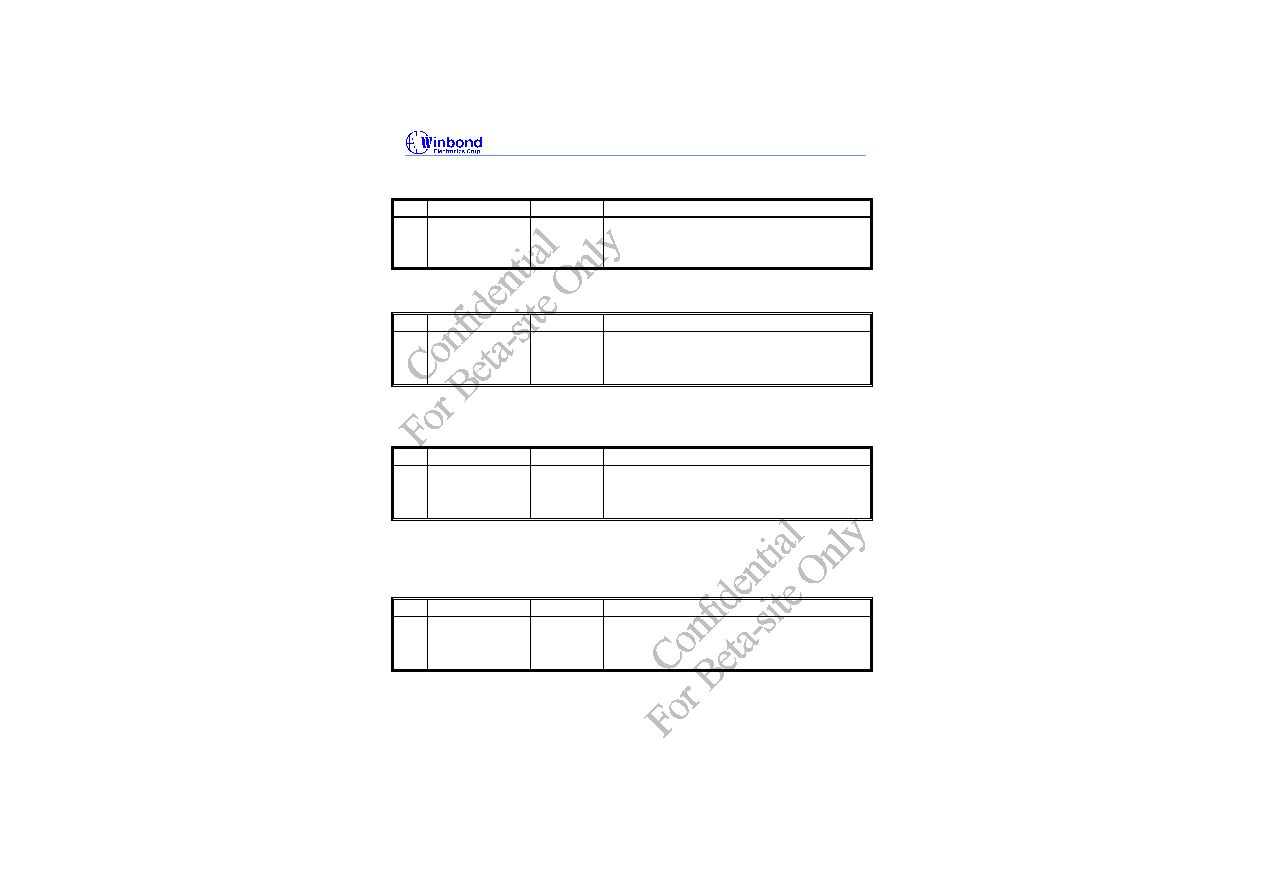

4. PIN CONFIGURATION

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

SDA

13

14

12

11

VCC

CPUT1/PII1

VREF

VIN1

RESET#

VIN2(+3.3VIN)

CPUT2/PII2

GND

FANFAULT#/GPO3

OVT#

SMI#

PWMOUT2

SCL

PWMOUT1

BATFAULT#/GPO4

FANIN2/GPO2

FANIN1/GPO1

VIN3(VBAT)

PWR_DN#

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-8 - Revision 0.54

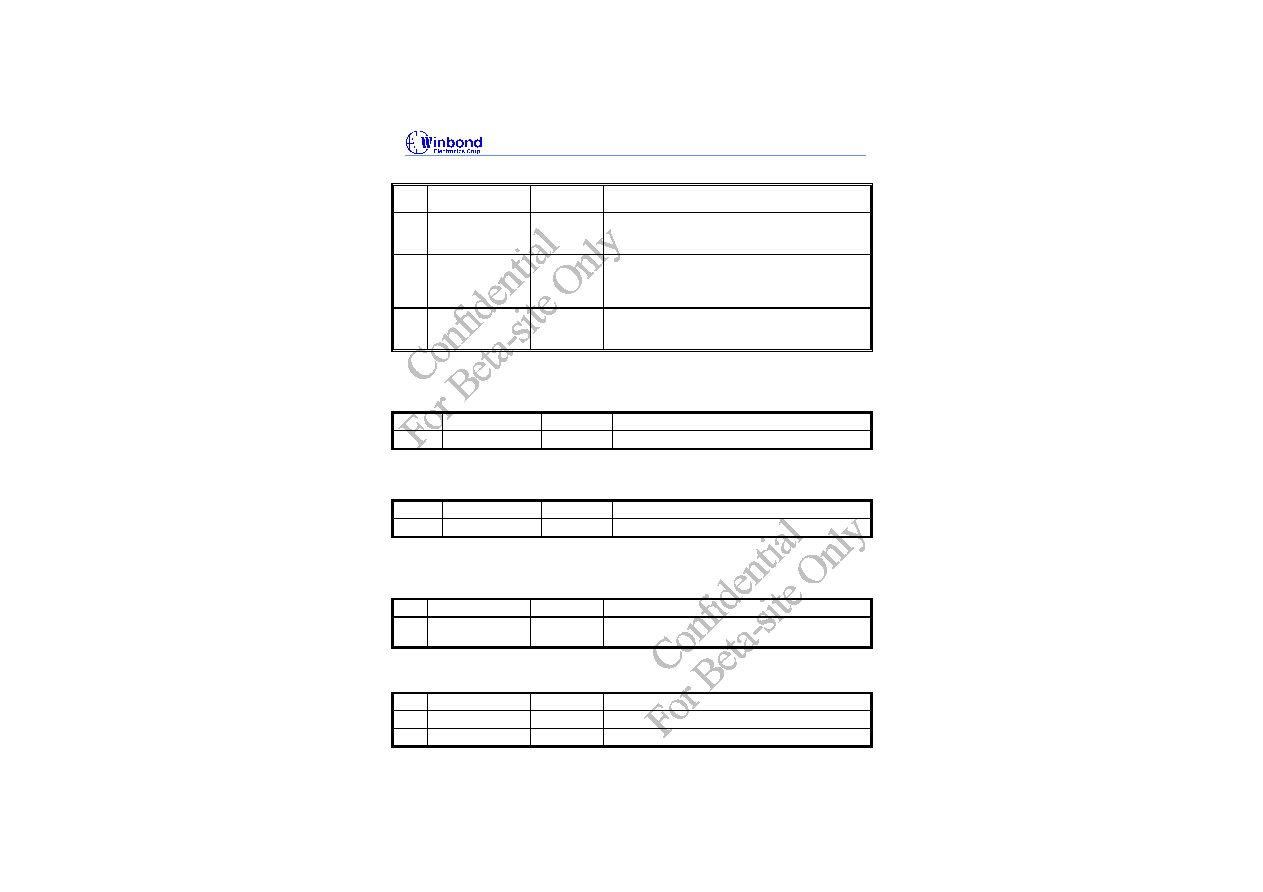

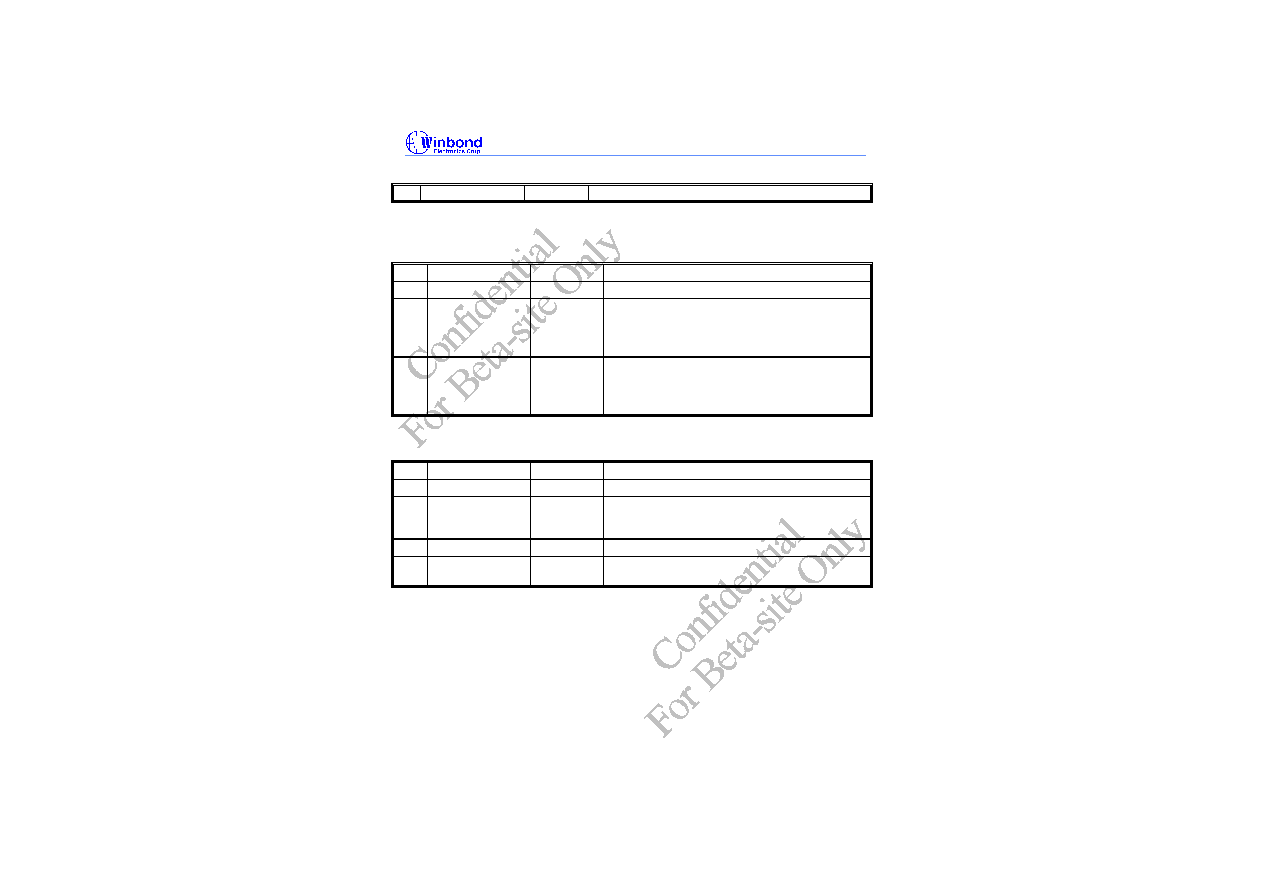

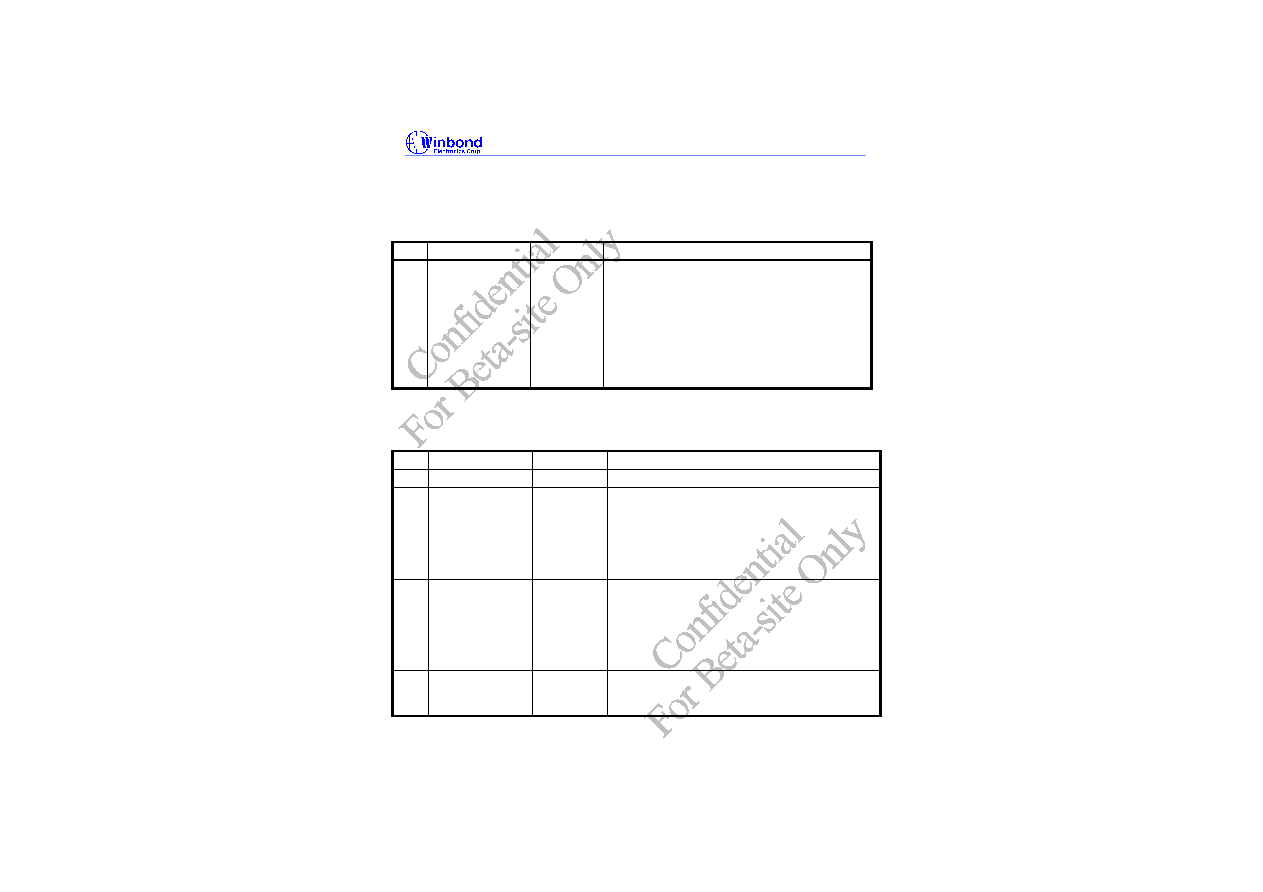

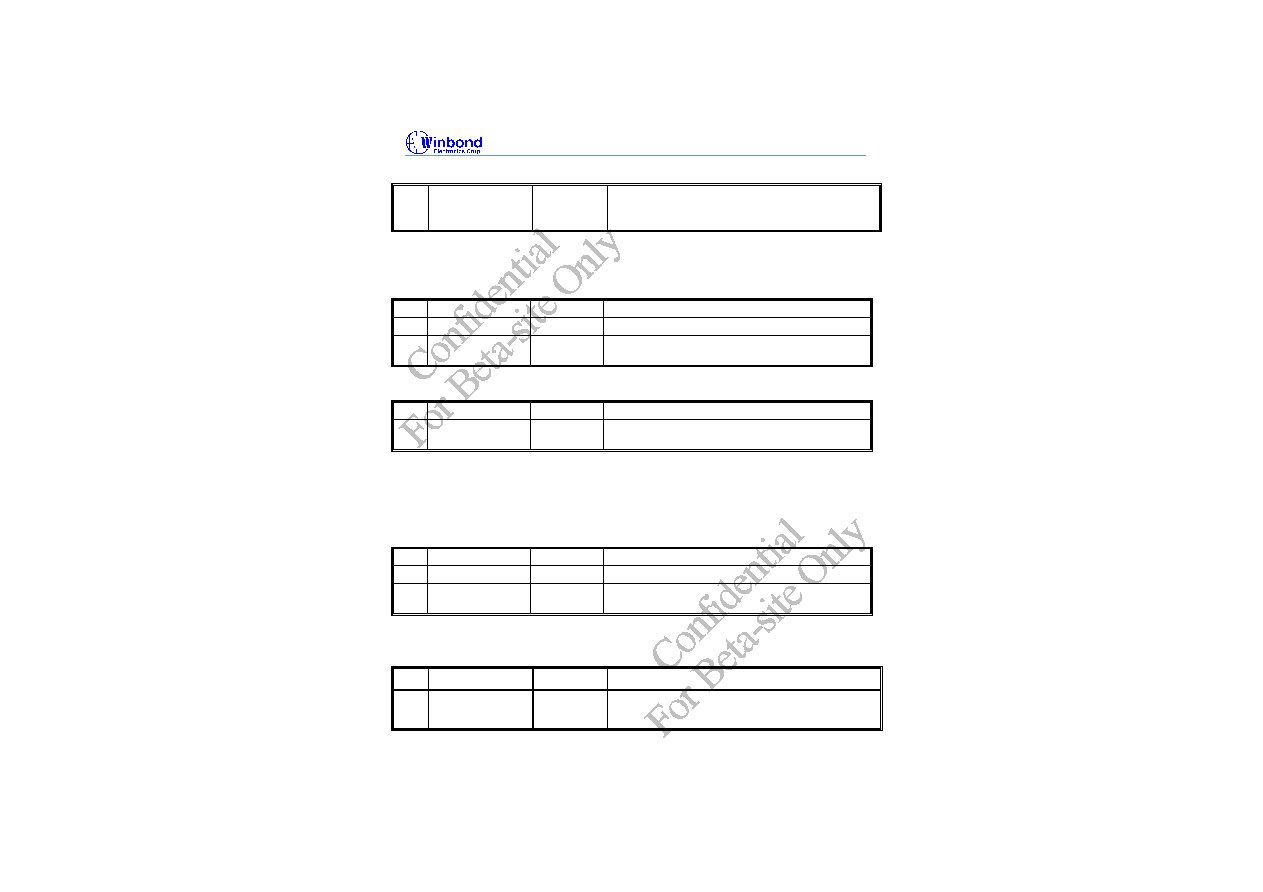

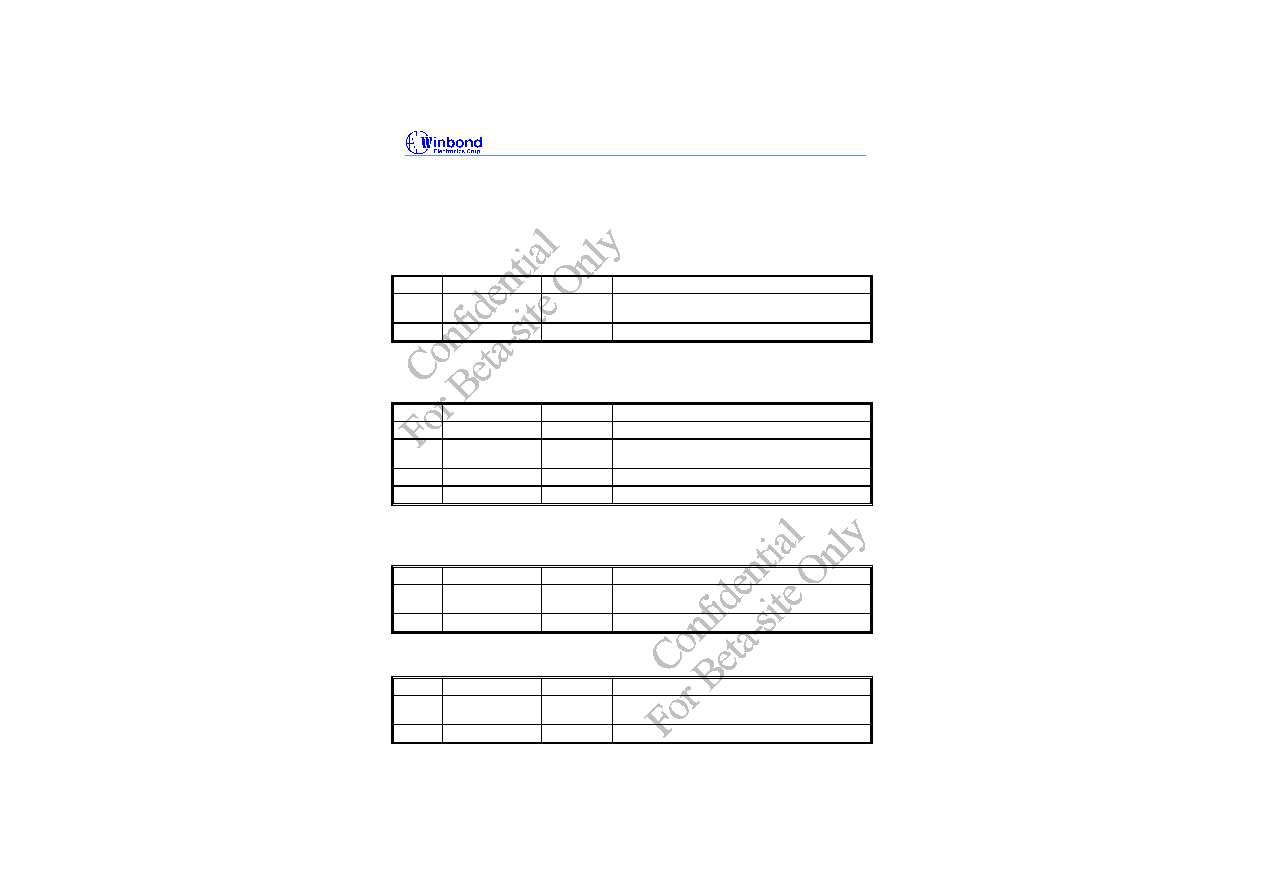

5. PIN DESCRIPTION

I/O

12t

- TTL level bi-directional pin with 12 mA source-sink capability

I/O

12ts

- TTL level and schmitt trigger

OUT

12

- Output pin with 12 mA source-sink capability

AOUT - Output pin(Analog)

OD

12

- Open-drain output pin with 12 mA sink capability

IN

t

- TTL level input pin

IN

ts

- TTL level input pin and schmitt trigger

AIN - Input pin(Analog)

PIN NAME

PIN NO.

TYPE

DESCRIPTION

FANIN1 /

GPO1

1

IN

t s

/

OUT

1 2

0V to +5V amplitude fan tachometer input. (Default) /

General purpose output .

This multi-functional pin is programmable.

FANIN2 /

GPO2

2

IN

t s

/

OUT

1 2

0V to +5V amplitude fan tachometer input. (Default) /

General purpose output .

This multi-functional pin is programmable.

PWMOUT1

3

OD

12

/

OUT

1 2

Fan speed control PWM output. This pin is

default open-drain. It

can be programmed as an output pin which can drive a HIGH or

a LOW.

PWMOUT2

4

OD

12

/

OUT

1 2

Fan speed control PWM output. This pin is

default open-drain. It

can be programmed as an output pin which can drive a HIGH or

a LOW.

FANFAULT# /

GPO3

5

OD

1 2

Active-Low output. This pin will be a logic LOW when fan1 or

fan2 is abnormally stopped. (Default) /

General purpose output .

This multi-functional pin is programmable.

PWR_DN#

6

IN

t

Power down input. When set this pin LOW, all output pins would

be tristate except the pin15 RESET# which will keep HIGH.

SMI#

7

OD

12

System Management Interrupt.

OVT#

8

OD

12

Over temperature Shutdown Output.

SCL

9

IN

t s

Serial Bus Clock.

SDA

10

OD

12

Serial Bus bi-directional Data.

BATFAULT#

/

GPO4

11

OD

1 2

Active-Low output. This pin will be a logic LOW when Battery

abnormally drops below the low limit or above the high limit.

(Default) /

General purpose output .

This multi-functional pin is programmable.

GND

12

Ground

Ground.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-9 - Revision 0.54

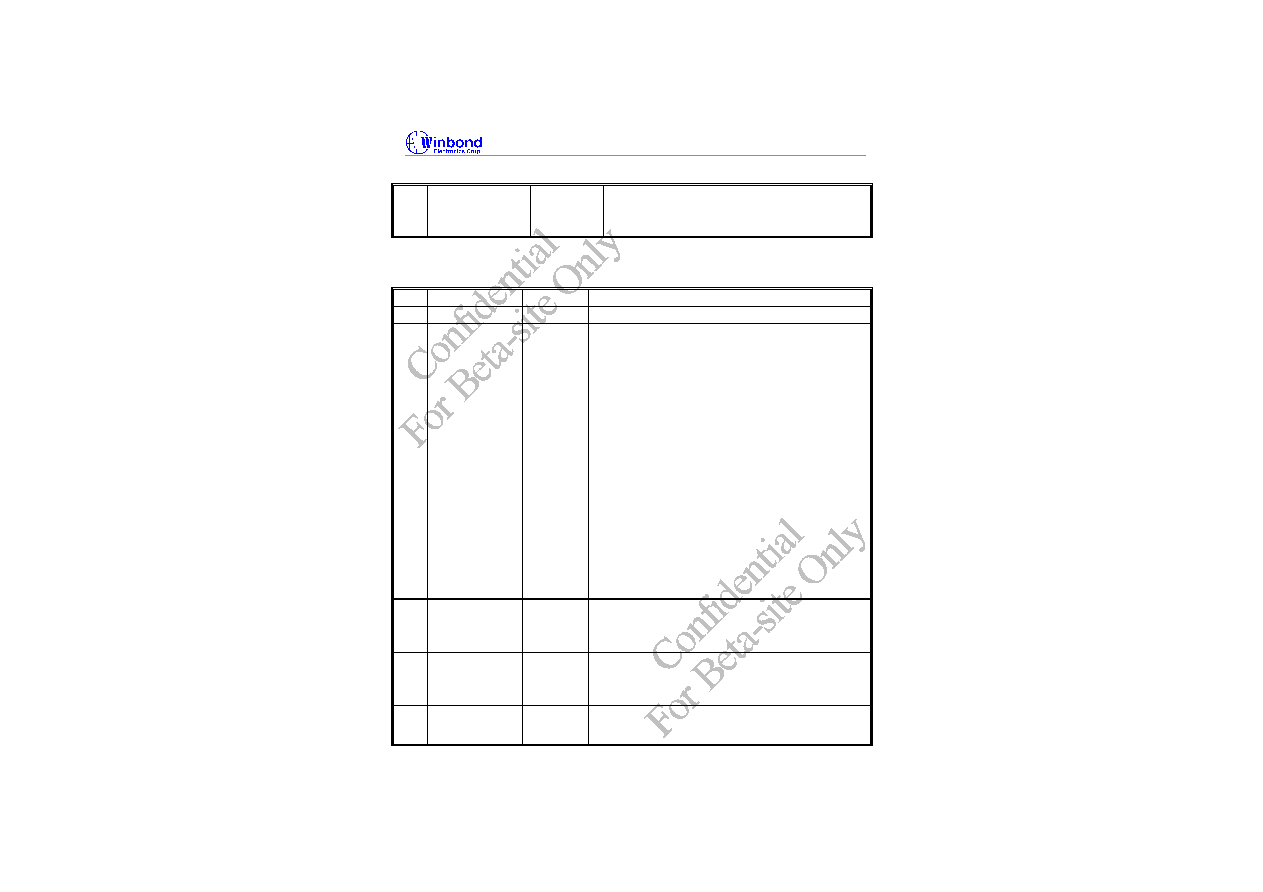

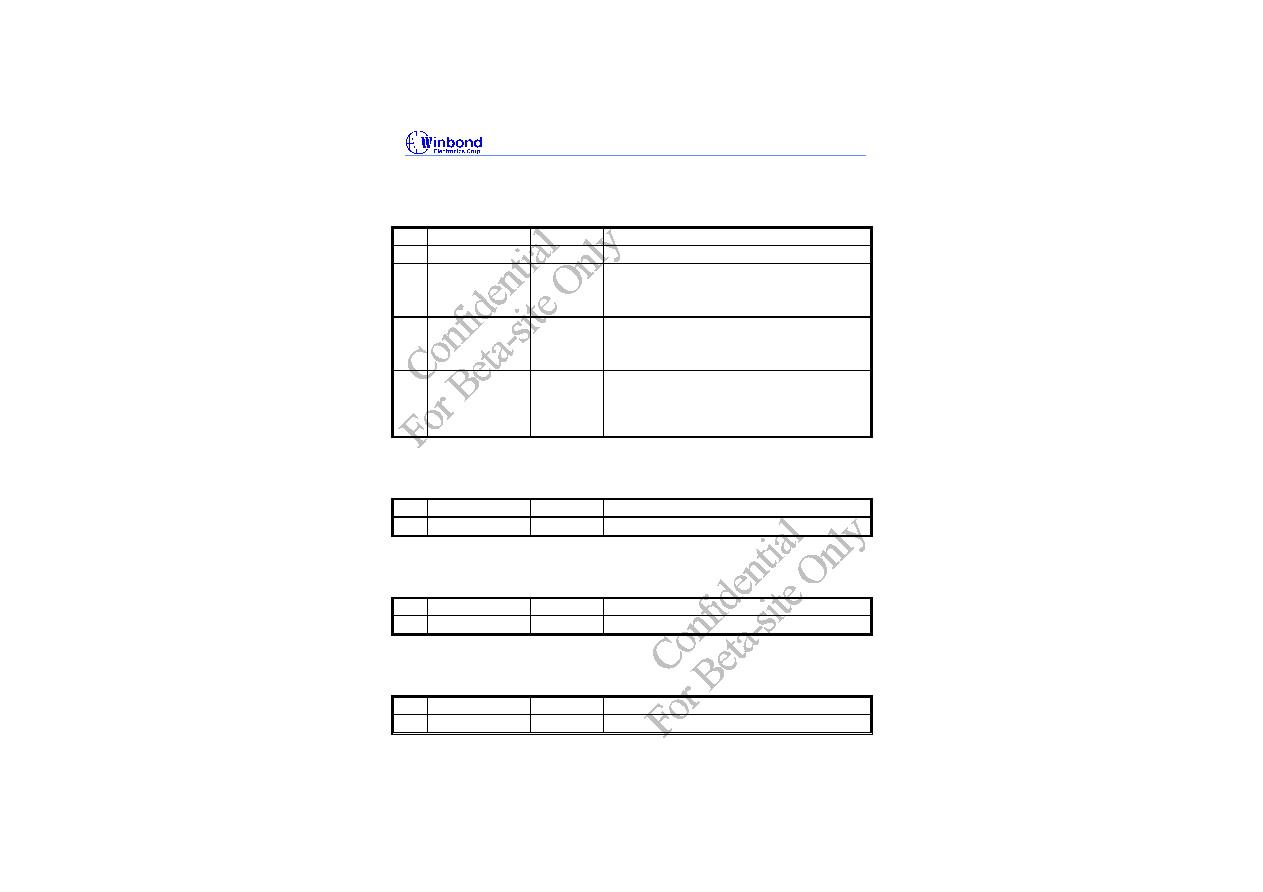

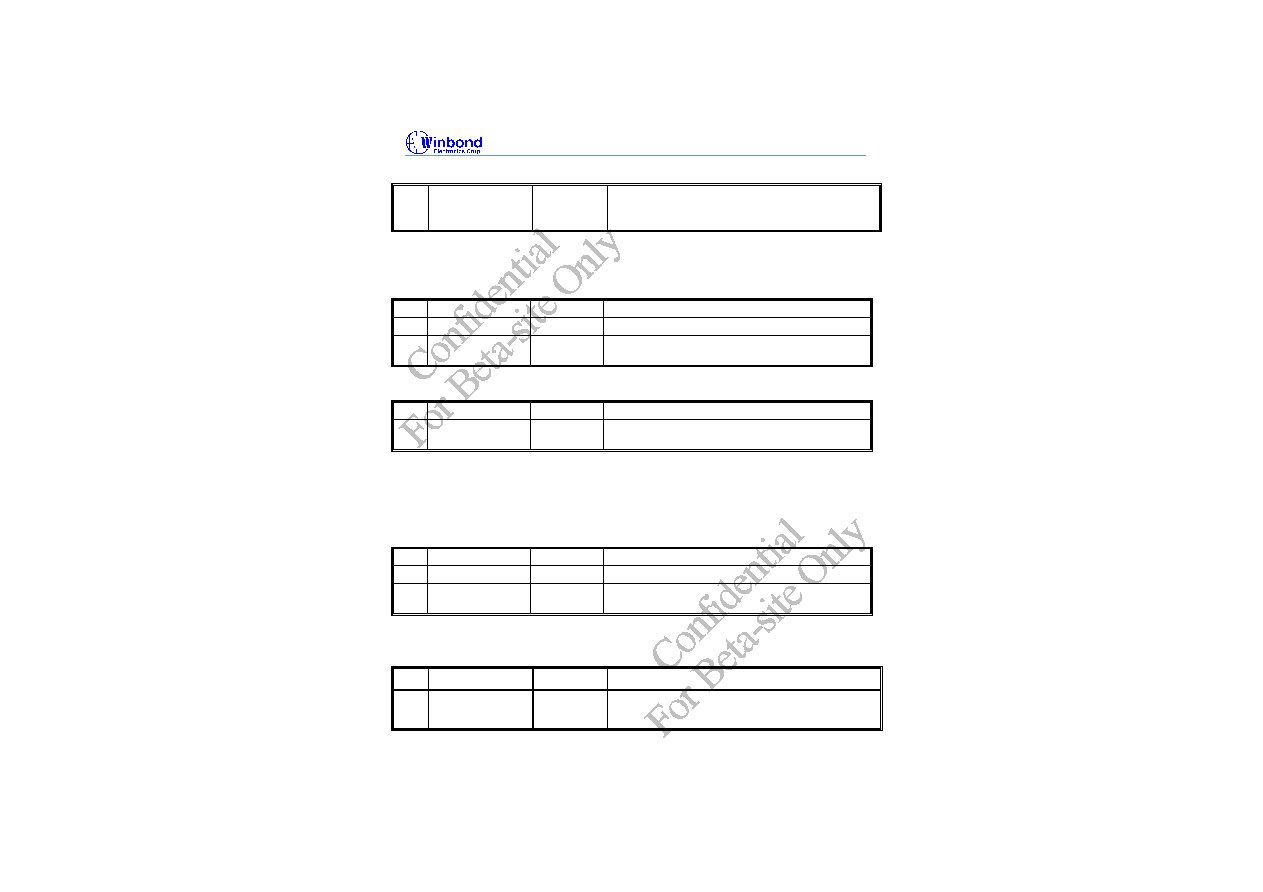

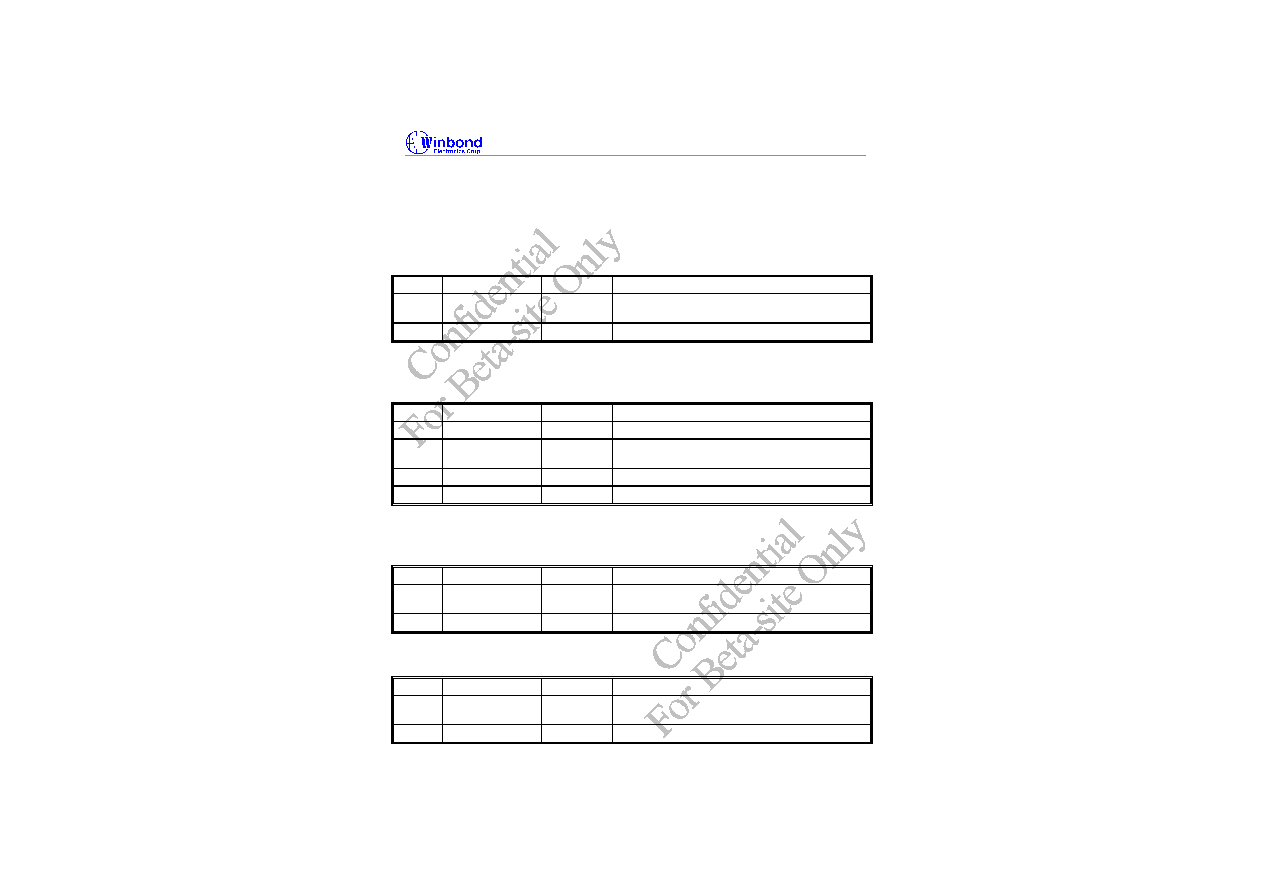

Pin Discription, continued

PIN NAME

PIN NO.

TYPE

DESCRIPTION

VIN3(VBAT)

13

AIN

0V to 4.096V FSR Analog Inputs. ( This pin should be

connected to DC BATTERY. If this voltage is above 4.096V, it

should be reduced with the external resistors so that the input

voltage will be under 4.096V. )

VIN2(+3.3VIN)

14

AIN

0V to 4.096V FSR Analog Inputs. (This pin should be

connected to 3VCC .)

RESET#

15

OUT

1 2

Active-Low reset output. RESET# remains LOW while the

5VCC and +3.3V are below the reset threshold. It remains

LOW for 200ms after the reset condition is terminated .

VIN1(VCORE)

16

AIN

0V to 4.096V FSR Analog Inputs.

VREF

17

AOUT

Reference Voltage.

CPUT2 /

PII2

18

AIN

Thermistor terminal input.(Default) /

Pentium

TM

II diode input.

This multi-functional pin is programmable.

CPUT1 /

PII1

19

AIN

Thermistor terminal input.(Default) /

Pentium

TM

II diode input.

This multi-functional pin is programmable.

VCC

20

POWER

+5VCC power supply input.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-10 - Revision 0.54

6. FUNCTIONAL DESCRIPTION

6.1 General Description

The W83L784R provides at most 4 analog positive inputs, 2 fan speed monitors, 2 sets for

fan PWM (Pulse Width Modulation) Smart Fan Control , 2 remote thermal inputs from remote

thermistors or 2N3904 transistors or Pentium

TM

II (Deschutes) thermal diode outputs and one on-chip

thermal detection. W83L784R also provides the power good (reset) output for 3V and 5V power

detection and two fault output pins issuing hardware warning if battery and fans become abnormal.

When start the monitor function on the chip, the watch dog machine monitor every function and store

the value to registers. If the monitor value exceeds the limit value, the interrupt status will be set to 1.

6.2 Access Interface

The W83L784R provides I

2

C Serial Bus to read/write internal reigsters. In the W83L784R

there are three serial bus address. The first address defined at CR[4Ah] can read/write all registers

excluding CPUT1/CPUT2 temperature sensor registers and its address default value is 0101101. The

address for CPUT1 defined at CR[4Bh] bit2-0 only read/write CPUT1 temperature sensor registers

and the address default value is 1001001. The address for CPUT2 defined at CR[4Bh] bit2-0 only

read/write CPUT1 temperature sensor registers and the address default value is 1001000.

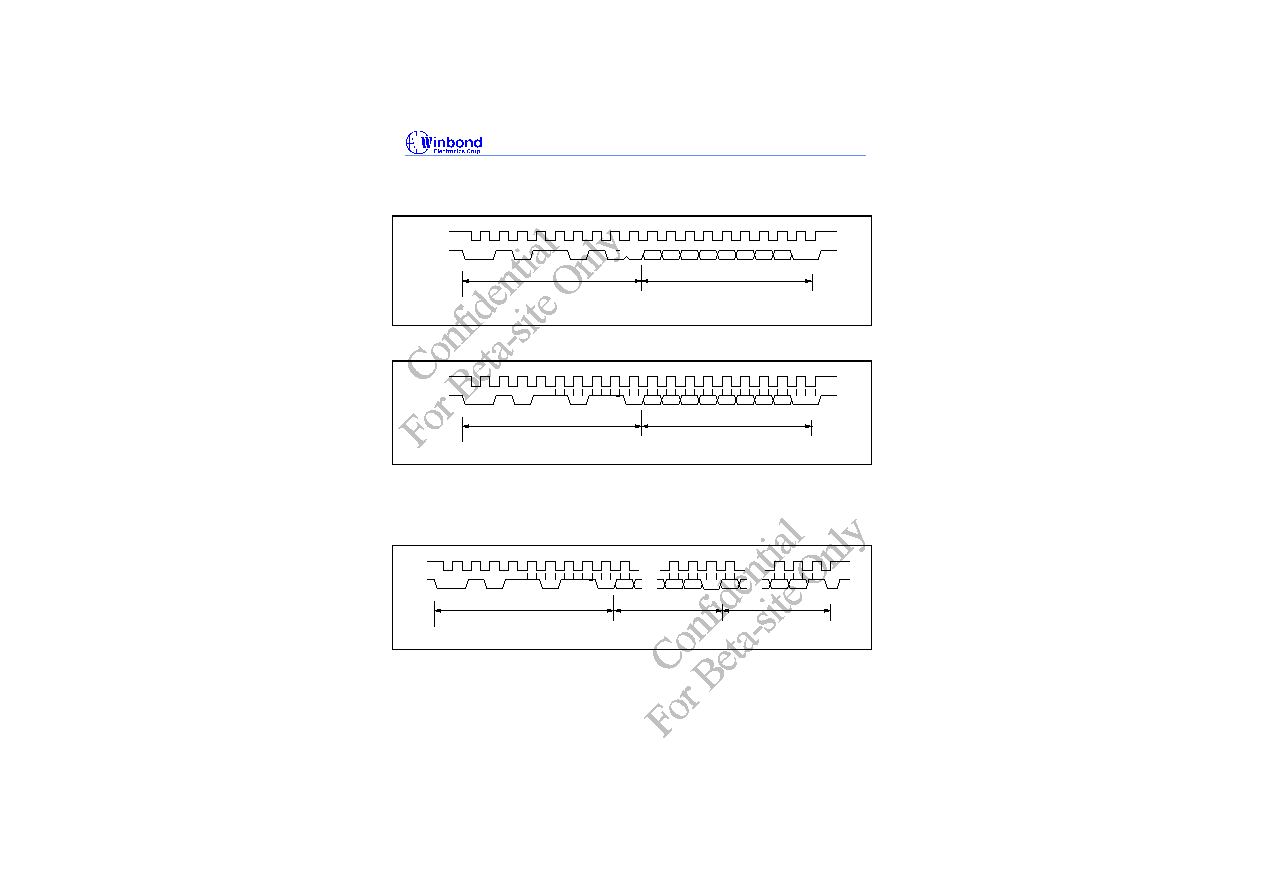

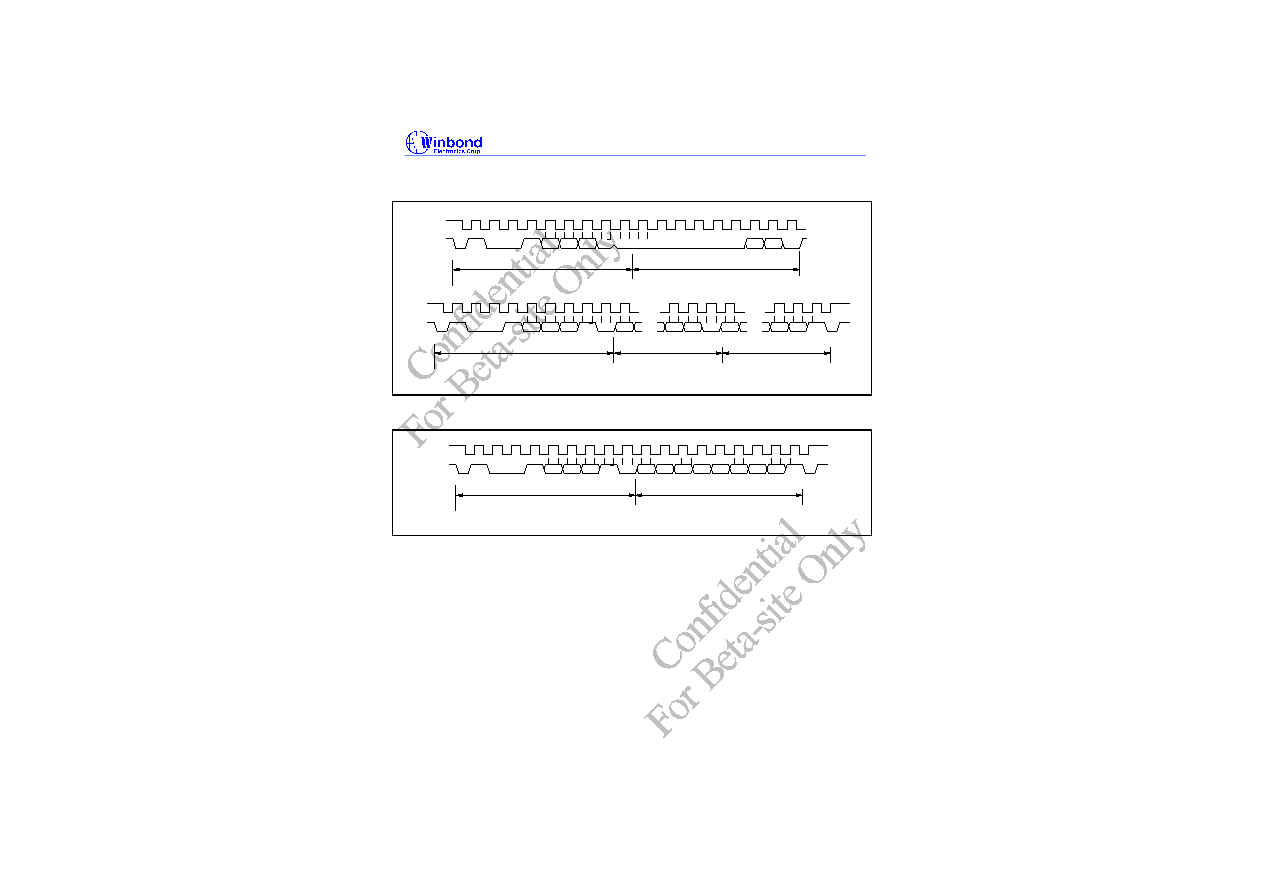

6.2.1 The first serial bus access timing are shown as follow:

(a) Serial bus write to internal address register followed by the data byte

0

Start By

Master

0

1

0

1

1

0

1

D7

D6

D5

D4

D3

D2

D1

D0

Ack

by

784R

R/W

Ack

by

784R

SCL

SDA

D7

D6

D5

D4

D3

D2

D1

D0

Ack

by

784R

Stop

by

Master

SCL

SDA (Continued)

7

8

0

7

8

0

7

8

Frame 2

Internal Index Register Byte

(Continued)

Frame 3

Data Byte

Frame 1

Serial Bus Address Byte

Figure 1. Serial Bus Write to Internal Address Register followed by the Data Byte

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-11 - Revision 0.54

(b) Serial bus write to internal address register only

0

Start By

Master

0

1

0

1

1

0

1

D7

D6

D5

D4

D3

D2

D1

D0

Ack

by

784R

R/W

Ack

by

784R

SCL

SDA

7

8

0

7

8

0

Frame 2

Internal Index Register Byte

Frame 1

Serial Bus Address Byte

Figure 2. Serial Bus Write to Internal Address Register Only

Stop by

Master

(c) Serial bus read from a register with the internal address register prefer to desired location

0

Start By

Master

0

1

0

1

1

0

1

D7

D6

D5

D4

D3

D2

D1

D0

Ack

by

Master

R/W

Ack

by

784R

SCL

SDA

7

8

0

7

8

0

Frame 2

Internal Index Register Byte

Frame 1

Serial Bus Address Byte

Figure 3. Serial Bus Read from Internal Address Register

Stop by

Master

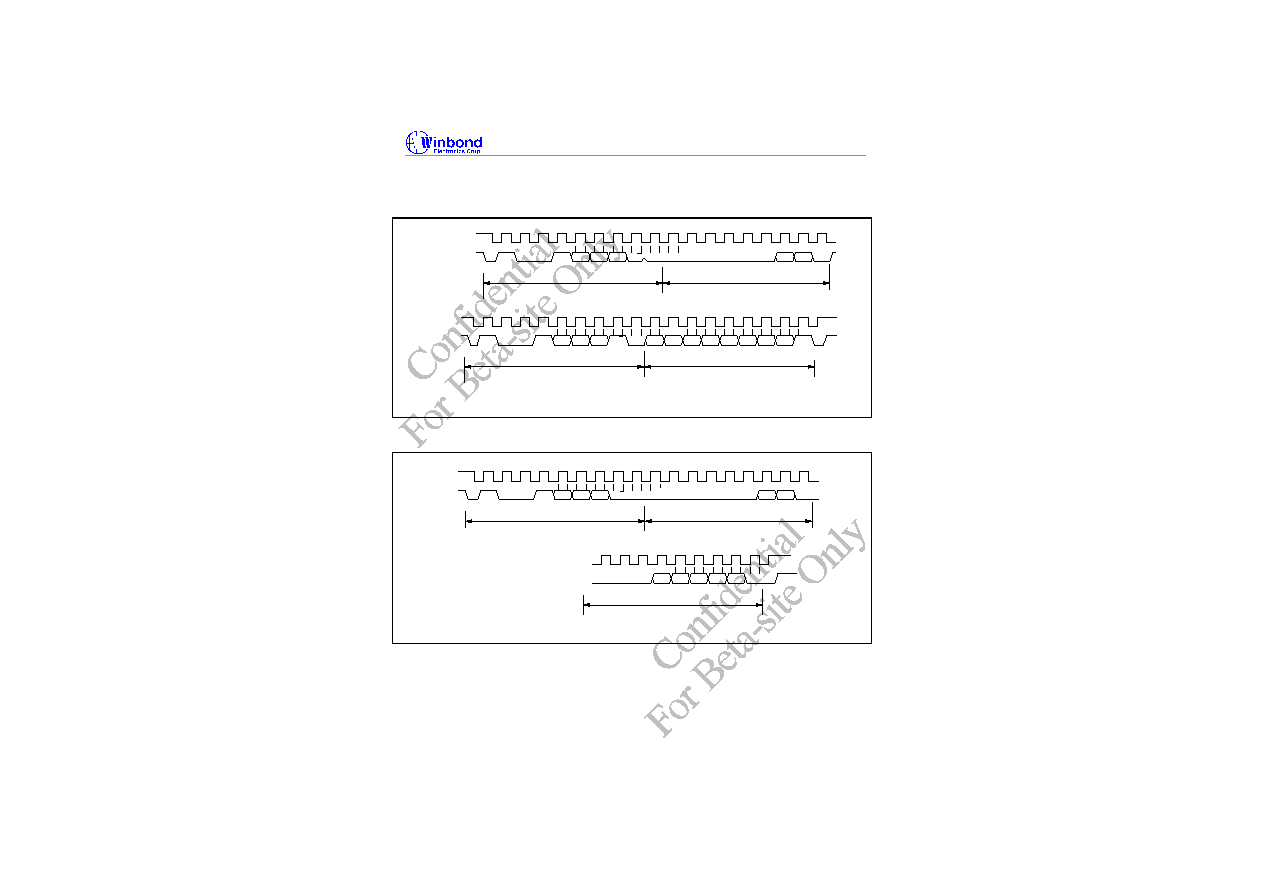

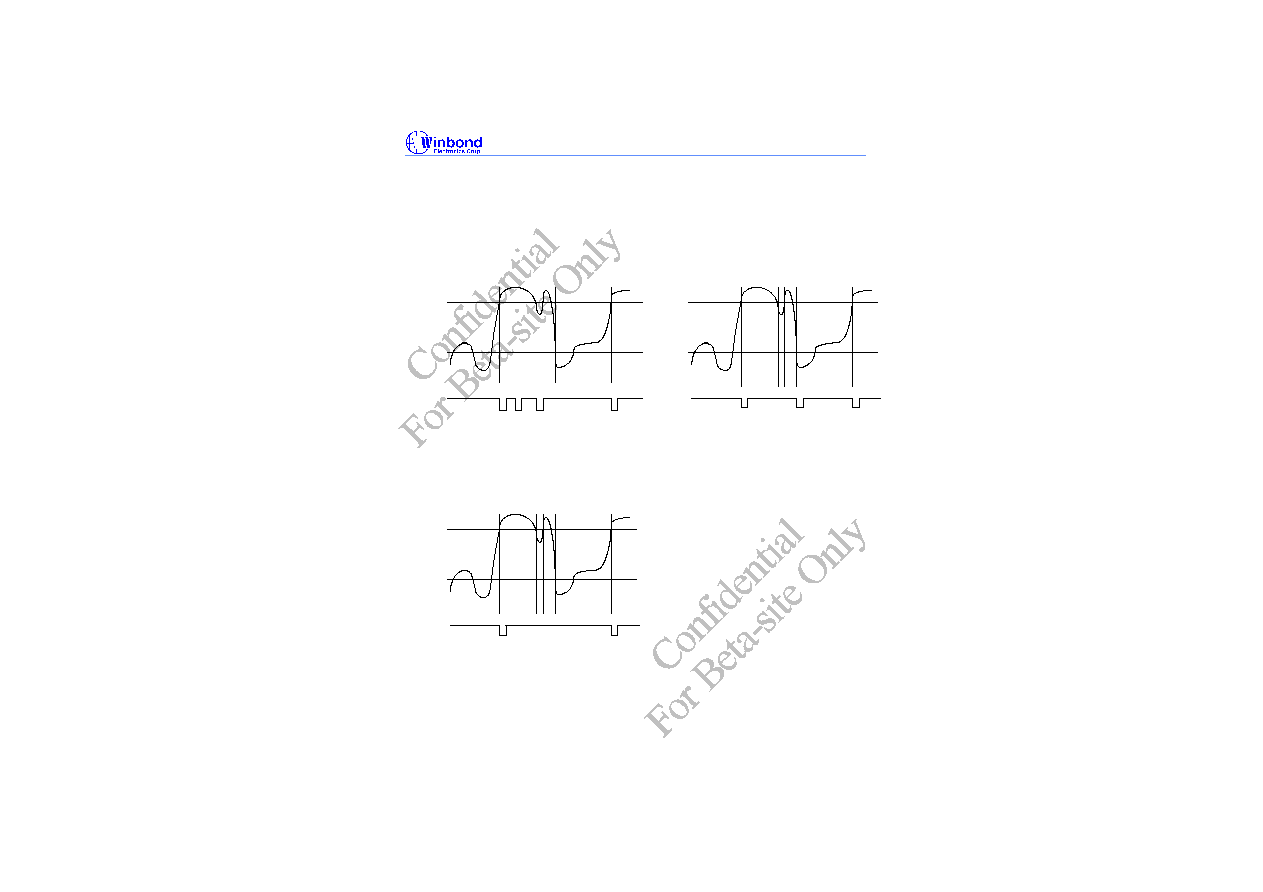

6.2.2 The serial bus timing of the temperature CPUT1 and CPUT2 is shown as follow:

(a) Typical 2-byte read from preset pointer location (Temp, T

OS

, T

HYST

)

0

Start By

Master

0

1

0

1

1

0

1

D7

D1

D0

Ack

by

Master

R/W

Ack

by

784R

SCL

SDA

7

8

0

7

8

Frame 2

MSB Data Byte

Frame 1

Serial Bus Address Byte

Figure 4. Typical 2-Byte Read From Preset Pointer Location

D7

D1

D0

0

7

Stop by

Master

...

...

...

No Ack

by

Master

...

Frame 3

LSB Data Byte

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-12 - Revision 0.54

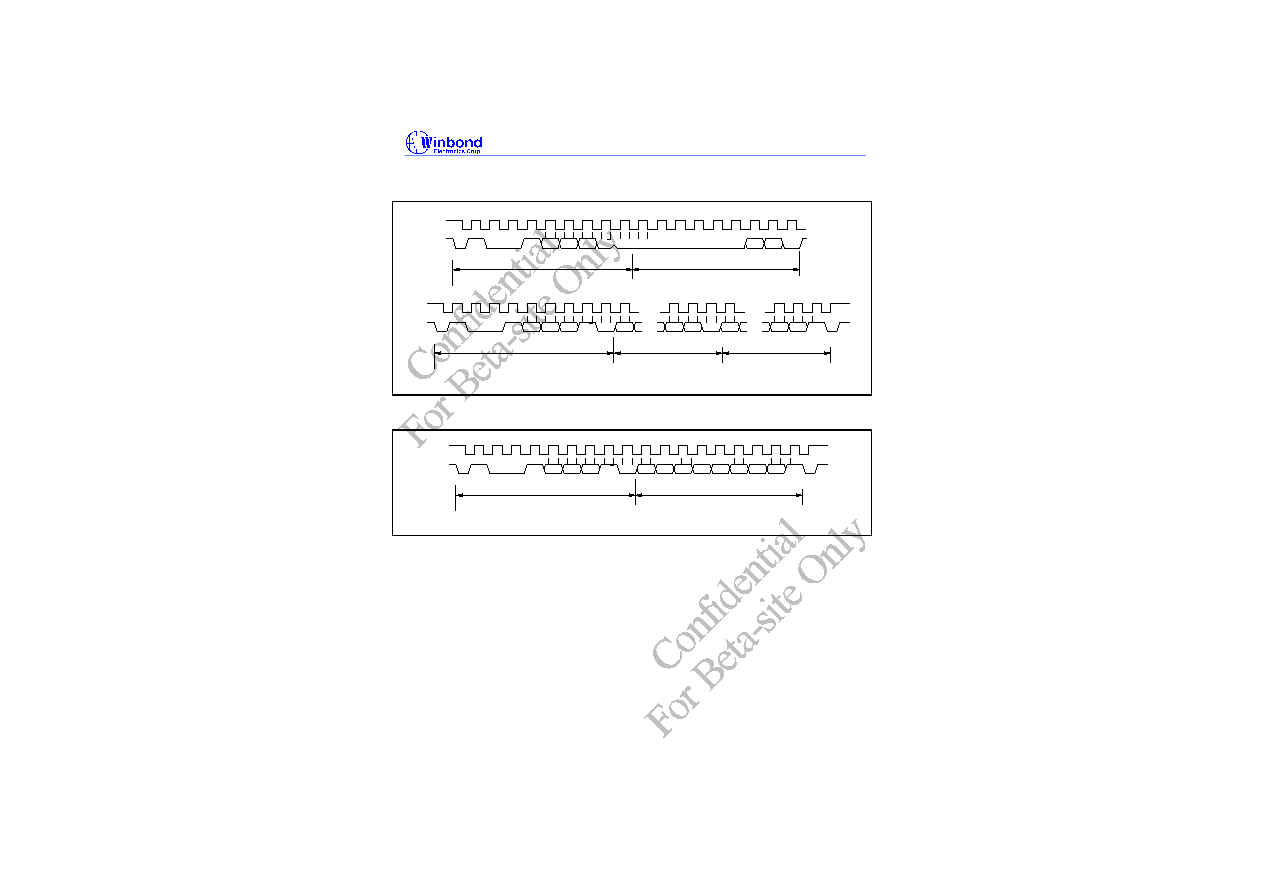

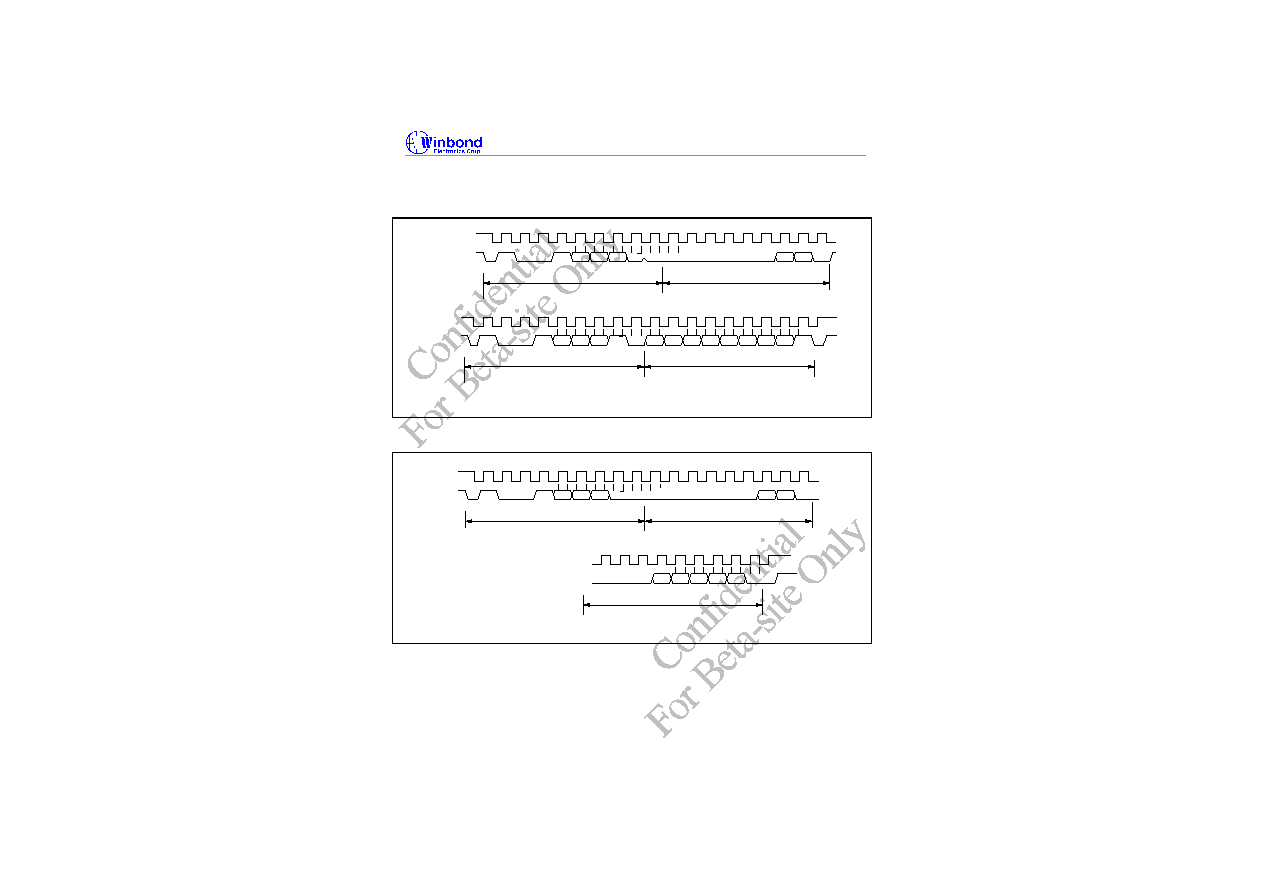

(b) Typical pointer set followed by immediate read for 2-byte register (Temp, T

OS

, T

HYST

)

0

Start By

Master

D7

D1

D0

Ack

by

Master

Ack

by

784R

SCL

SDA

7

8

0

7

8

0

Frame 4

MSB Data Byte

Frame 3

Serial Bus Address Byte

Figure 5. Typical Pointer Set Followed by Immediate Read for 2-Byte Register

D7

D1

D0

0

7

Stop by

Master

...

...

...

No Ack

by

Master

...

Frame 5

LSB Data Byte

0

Start By

Master

1

0

0

1

A2

A1

A0

R/W

Ack

by

784R

SCL

SDA

7

8

0

Frame 1

Serial Bus Address Byte

4

D1

D0

Ack

by

784R

Frame 2

Pointer Byte

1

0

0

1

A2

A1

A0

R/W

0

0

0

0

0

0

(c) Typical read 1-byte from configuration register with preset pointer

0

Start By

Master

D7

D2

Ack

by

782D

SCL

SDA

7

8

0

Frame 2

Data Byte

Frame 1

Serial Bus Address Byte

Figure 6. Typical 1-Byte Read From Configuration With Preset Pointer

D0

7

Stop by

Master

No Ack

by

Master

1

0

0

1

A2

A1

A0

R/W

D1

D5

D4

D3

D6

8

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-13 - Revision 0.54

(d) Typical pointer set followed by immediate read from configuration register

0

Repea

Start

By

Master

D7

D5

D4

Ack

by

784R

SCL (Cont..)

SDA (Cont..)

7

8

0

Frame 4

MSB Data Byte

Frame 3

Serial Bus Address Byte

Figure 7. Typical Pointor Set Followed by Immediate Read from Temp 2/3 Configuration Register

D2

D1

D0

7

Stop by

Master

No Ack

by

Master

0

Start By

Master

1

0

0

1

A2

A1

A0

R/W

Ack

by

784R

SCL

SDA

7

8

0

Frame 1

Serial Bus Address Byte

4

D1

D0

Ack

by

784R

Frame 2

Pointer Byte

1

0

0

1

A2

A1

A0

R/W

...

...

D6

D3

8

7

8

0

0

0

0

0

0

(e) Temperature configuration register Write

0

Ack

by

784R

SCL (Cont...)

SDA (Cont...)

7

8

Frame 3

Configuration Data Byte

Figure 8. Configuration Register Write

0

Start By

Master

1

0

0

1

A2

A1

A0

R/W

Ack

by

784R

SCL

SDA

7

8

0

Frame 1

Serial Bus Address Byte

4

D1

D0

Ack

by

784R

Frame 2

Pointer Byte

0

0

D4

D3

D2

D1

0

D0

Stop

by

Master

0

0

0

0

0

0

0

7

8

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-14 - Revision 0.54

(f) Temperature T

OS

and T

HYST

write

0

Ack

by

784R

SCL (Cont...)

SDA (Cont...)

7

8

Frame 3

MSB Data Byte

Figure 9. Configuration Register Write

0

Start By

Master

1

0

0

1

A2

A1

A0

R/W

Ack

by

784R

SCL

SDA

7

8

0

Frame 1

Serial Bus Address Byte

4

D1

D0

Ack

by

784R

Frame 2

Pointer Byte

D6

D5

D4

D3

D2

D1

D7

D0

0

7

8

D6

D5

D4

D3

D2

D1

D7

D0

Ack

by

784R

Stop

by

Master

Frame 4

LSB Data Byte

7

8

0

0

0

0

0

0

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-15 - Revision 0.54

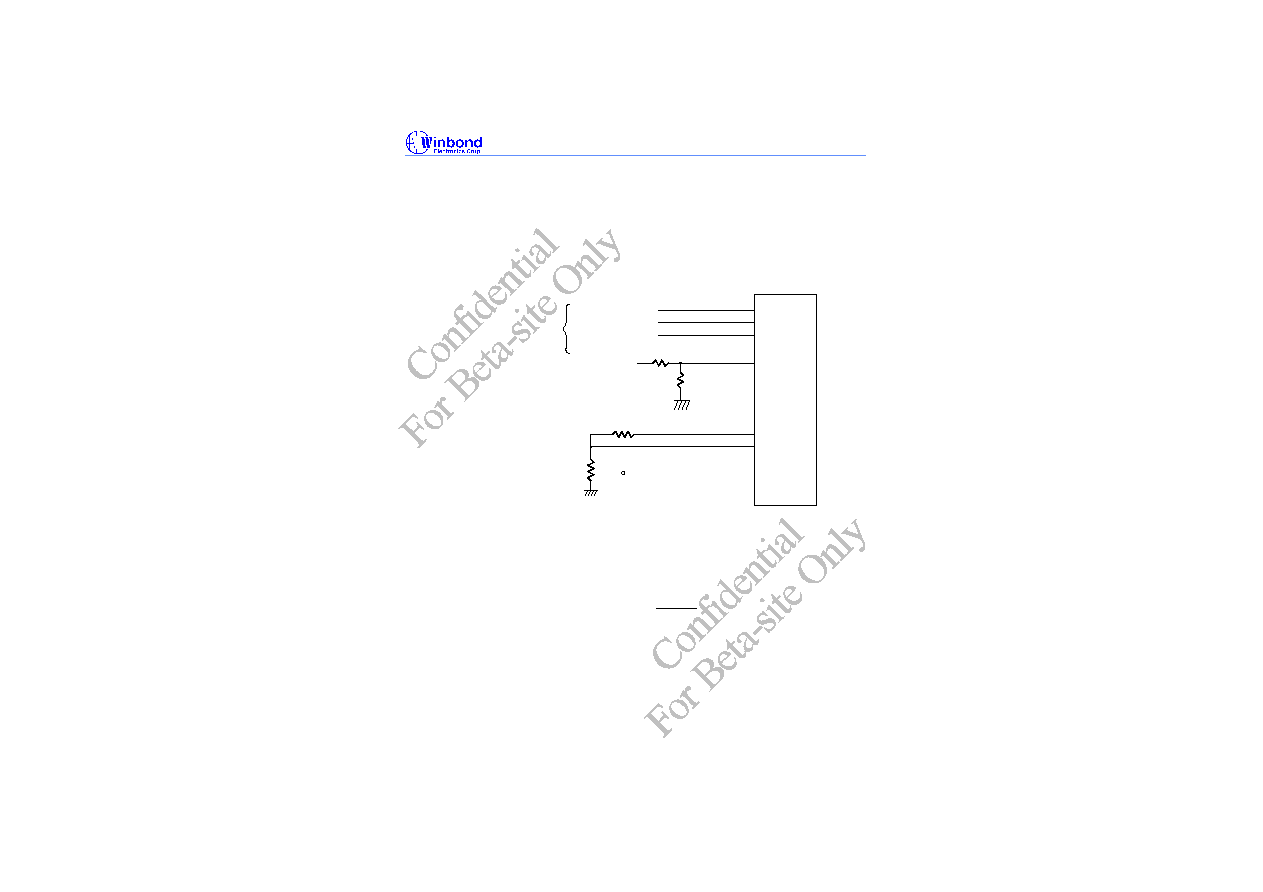

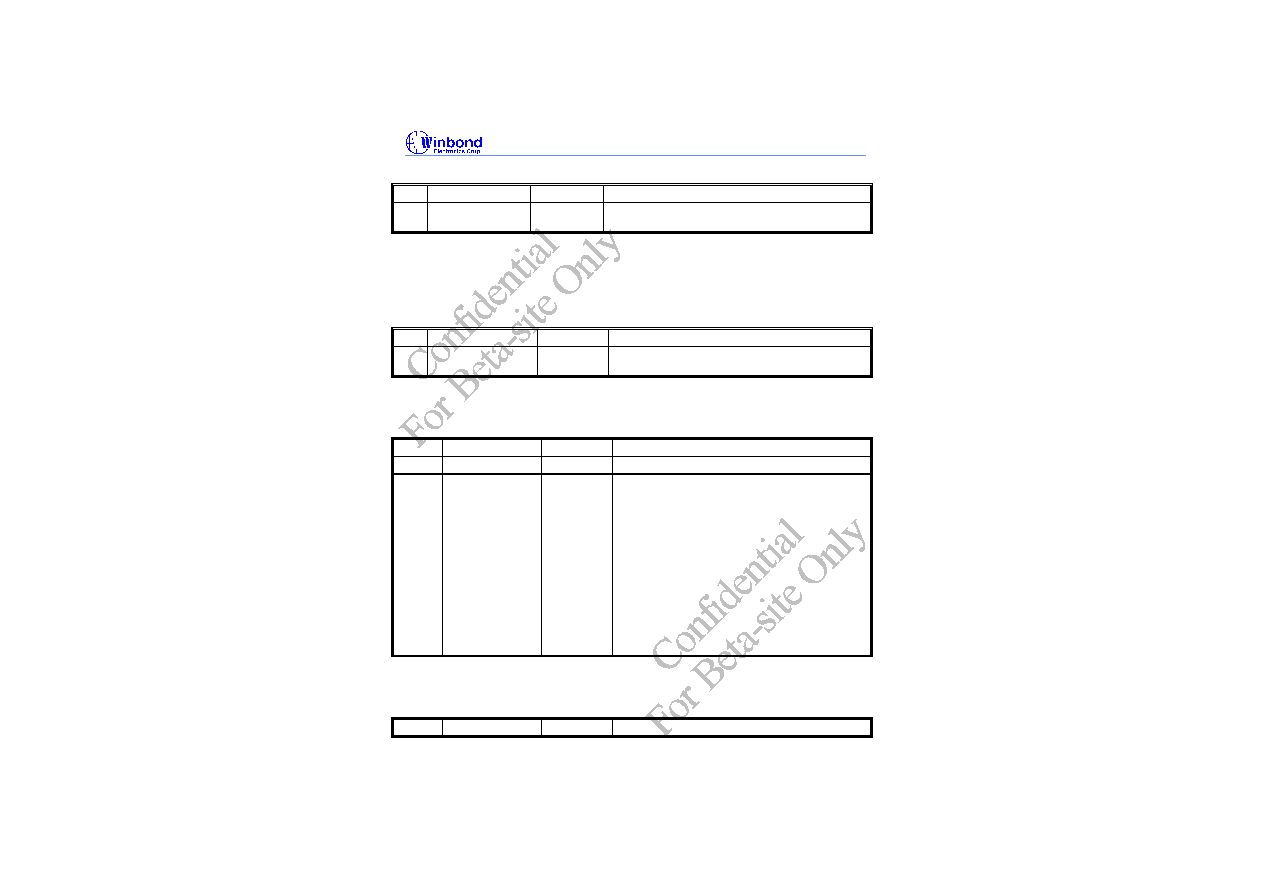

6.3 Analog Inputs

The maximum input voltage of the analog pin is 4.096V because the 8-bit ADC has a 16mv LSB.

Really, the application of the PC monitoring would most often be connected to power suppliers. The

CPU V-core voltage and +3.3V voltage can directly connected to these analog inputs. The 5VSB and

battery inputs should be reduced a factor with external resistors so as to obtain the input range. As

Figure 10 shows.

VIN1(VCORE)

VIN2(+3.3V)

VIN3(VBAT)

Pin 14

Pin 13

Pin 20

VCC

R1

10V(Battery DC)

8-bit ADC

with

16mV LSB

Typical Thermister

Connection

232K, 1%

RTHM

Pin 17

CPUT1

Pin 19

Positive Inputs

10K, 25 C

**The connections of CPUT2

is same as CPUT1

R2

R

Pin 16

VREF

10K, 1%

99K, 1%

Figure. 10.

6.3.1 Monitor over 4.096V voltage:

The input voltage VIN3 can be expressed as following equation.

VIN

V

R

R

R

BAT DC

3

2

1

2

=

�

+

-

The value of R1 and R2 can be selected to 232K Ohms and 99K Ohms, respectively, when the input

voltage V

BAT-DC

is 10V. The node voltage of VIN3 can be subject to less than 4.096V for the maximun

input range of the 8-bit ADC. The pin 24 is connected to the power supply VCC with +5V. There are

two functions in this pin with 5V. The first function is to supply internal analog power in the W83L784R

and the second function is that this voltage with 5V is connected to internal serial resistors to monitor

the +5V voltage. The value of two serial resistors are 34K ohms and 50K ohms so that input voltage

to ADC is 2.98V which is less than 4.096V of ADC maximum input voltage. The express equation can

represent as follows.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-16 - Revision 0.54

V

VCC

K

K

K

V

in

=

�

+

50

50

34

2 98

.

where VCC is set to 5V.

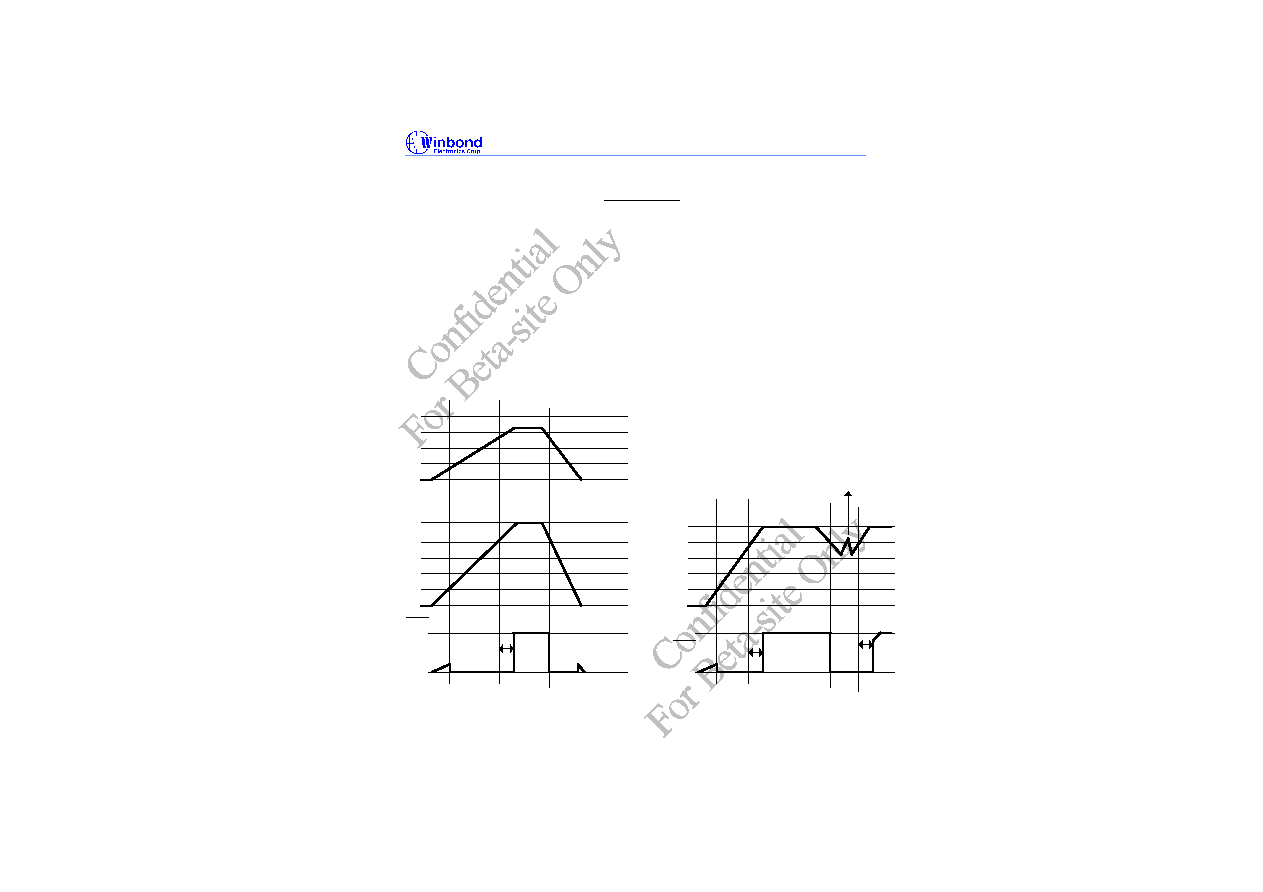

6.3.2 Power good for 3V and 5V

On power up, once VCC(5V) reaches 1V, RESET# will be a logic low. As 3V and VCC(5V)

rise, RESET# remains asserted. If 3V and VCC(5V) both exceed the reset threshold, RESET

becomes a logic high after a time equal to the reset pulse width (tRST, typically 200ms).(Figure 11).

If a power fail or a brownout happens(i.e. 3V or VCC(5V) drops below the threshold), RESET# output

is asserted. As long as the 3V and VCC(5V) remain below the reset threshold, RESET# output

remains asserted. Therefore, a brownout condition that interrupts a previously initiated reset pulse

causes an additional 200ms delay from the time the latest interruption occurred. On power-on, once

3Vor VCC(5V) drops below the reset threshold, RESET# are guaranteed to be asserted for VCC

1V.

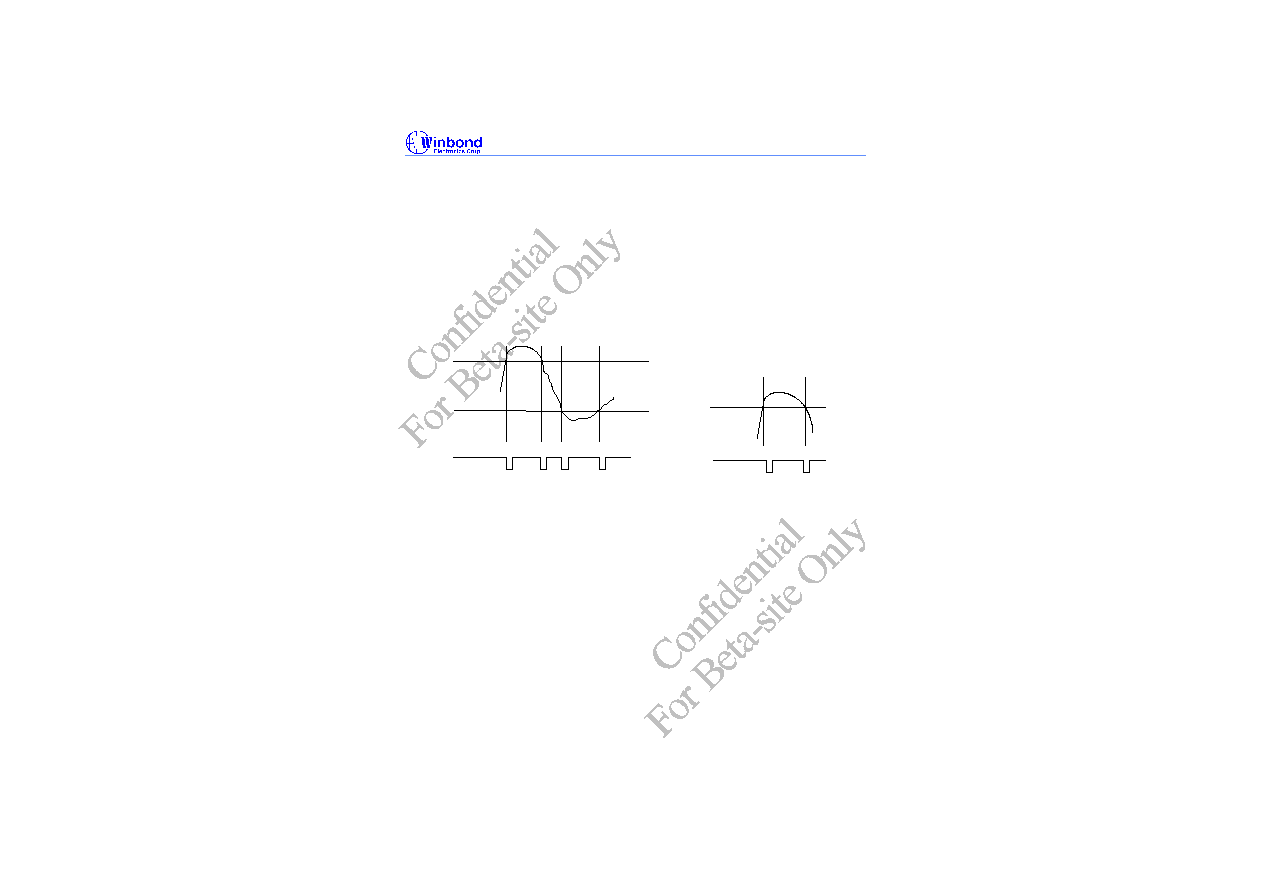

0

1

2

3

RESET

0

5

4

5

V

RST

tRST

V

RST

VCC

0

1

2

3

4

V

RST

V

RST

3.3V

0

1

2

3

RESET

0

5

4

5

V

RS

T

tRST

V

RS

T

tRST

V

RS

T

VCC

The time of voltage over 4V

is less than tRST

Figure 11

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-17 - Revision 0.54

6.3.3 Battery Fault Alarm

W83L784R provides a good protection for DC battery. Set VIN3 to monitor DC battery

voltage and enable VBAT fault function. When VIN3(pin13) voltage exceeds high or low limit value,

pin BATFAULT# will be asserted.

6.4 Temperature Measurement Machine

The temperature data format is 8-bit two?-complement for internal sensor and 9-bit two -complement

for sensor CPUT1 and CPUT2. The 8-bit temperature data can be obtained by reading the CR[27h].

The 9-bit temperature data (CPUT1 and CPUT2) can be obtained by reading CR[00h] of its serial bus

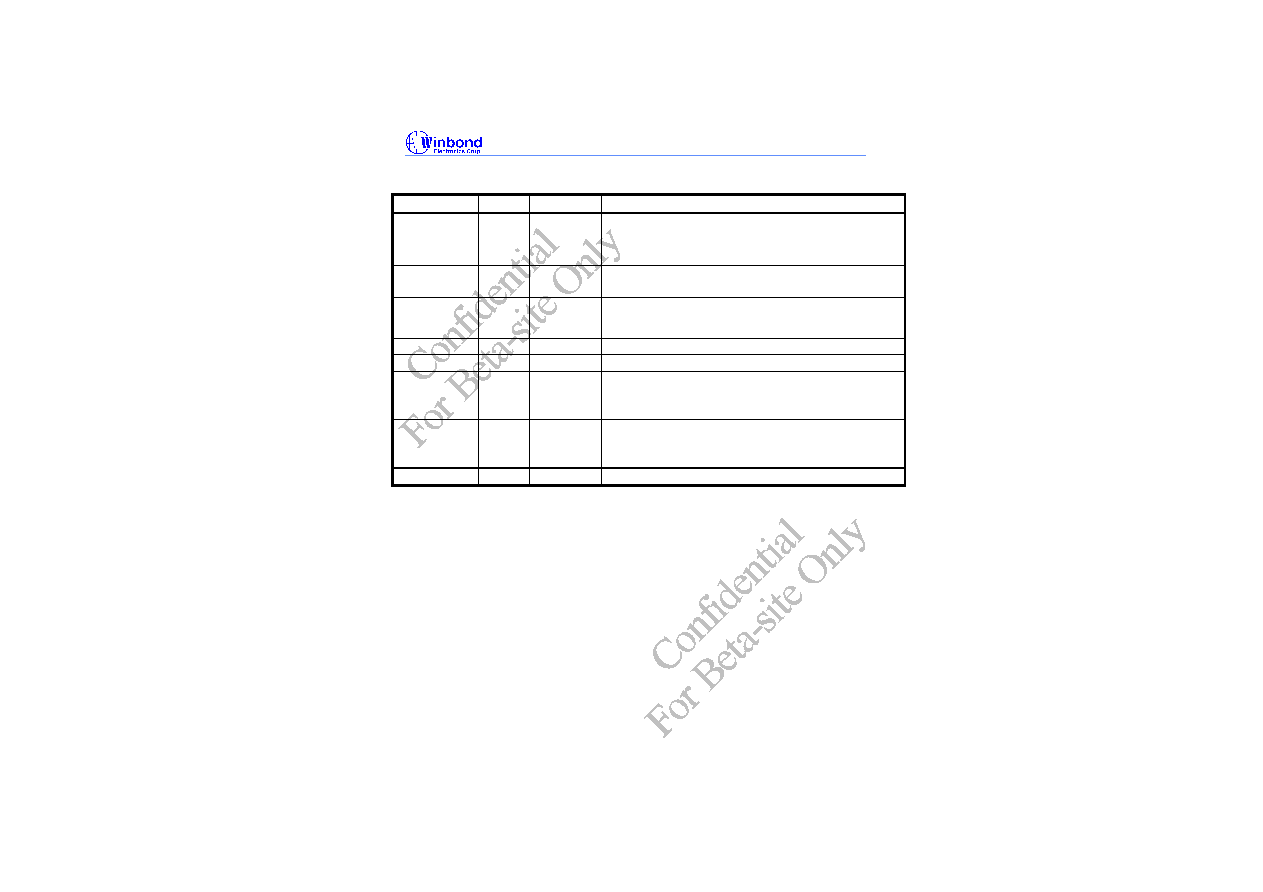

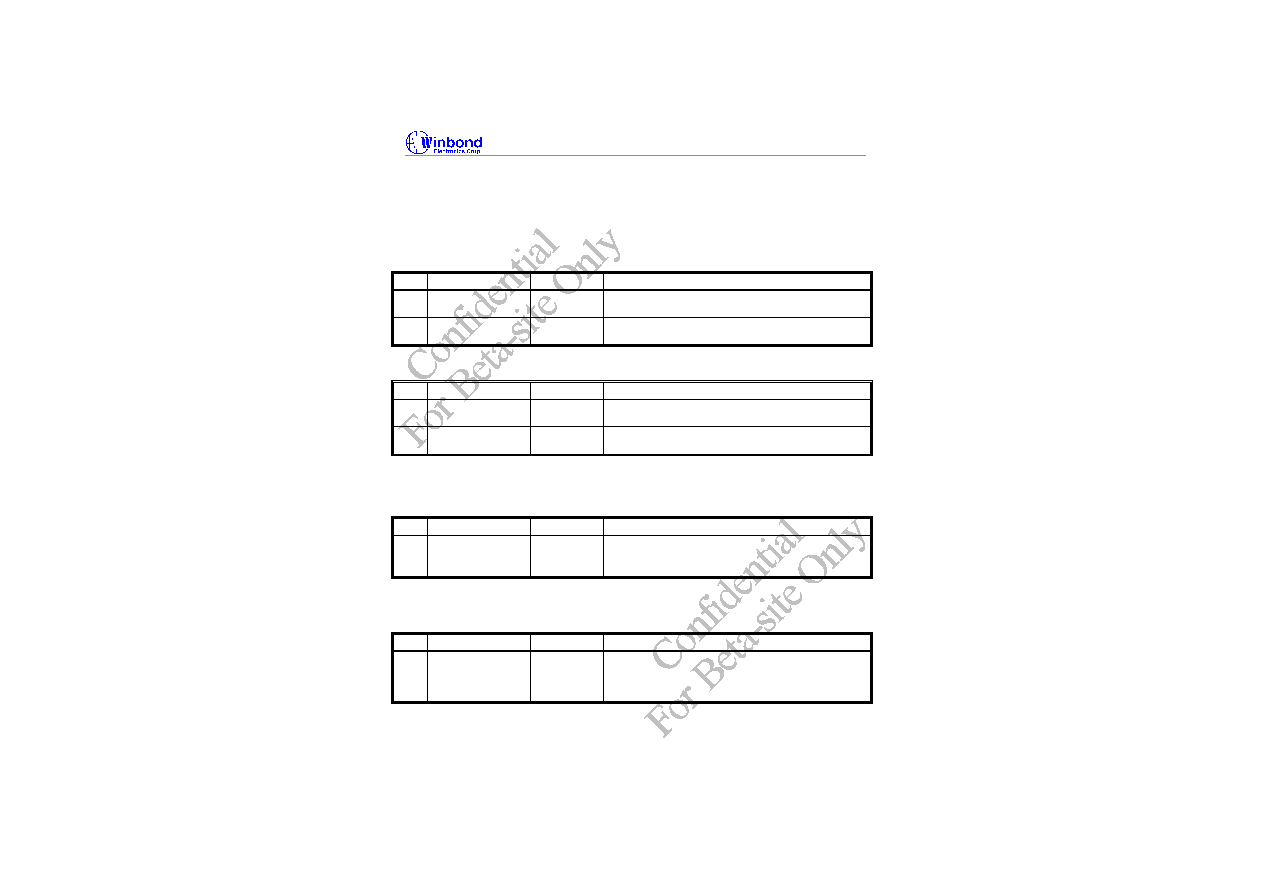

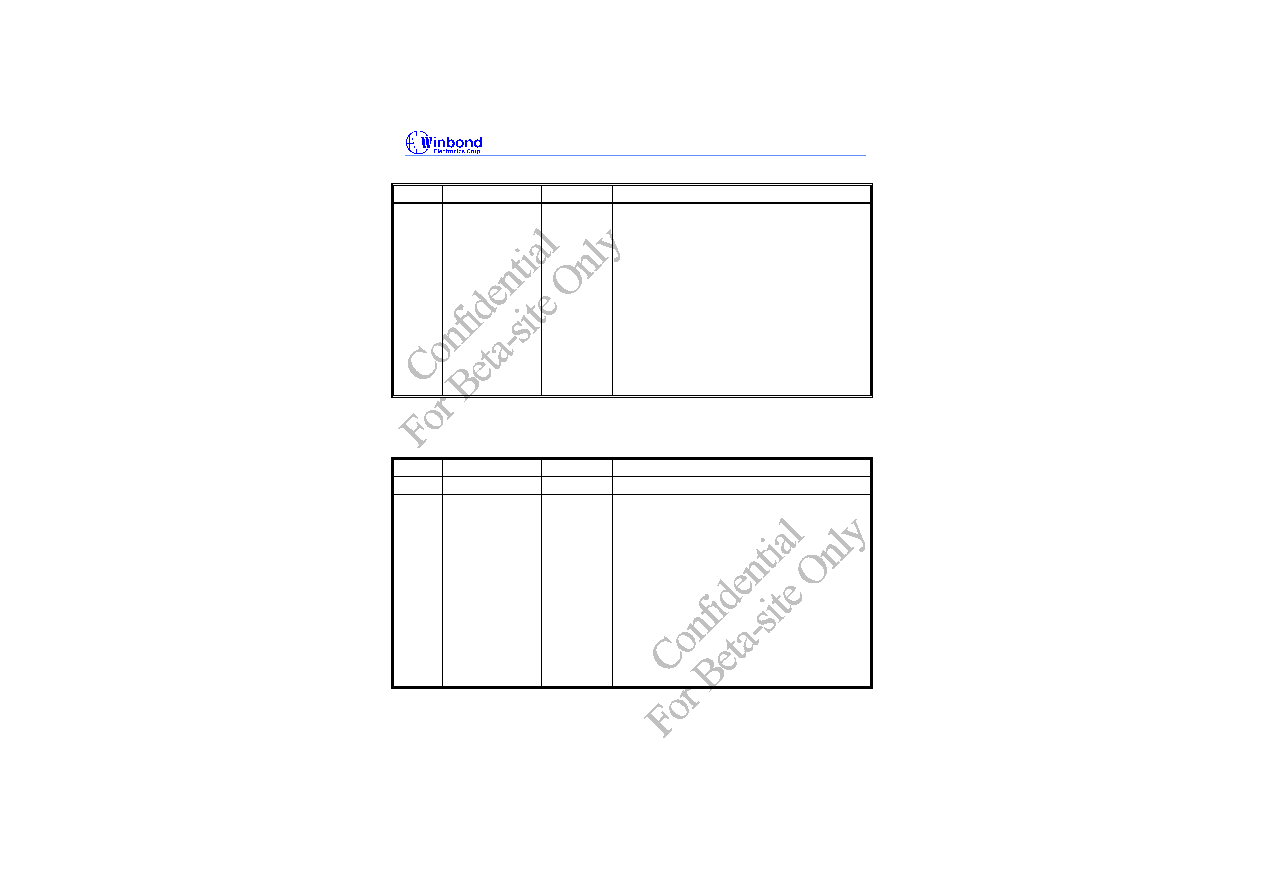

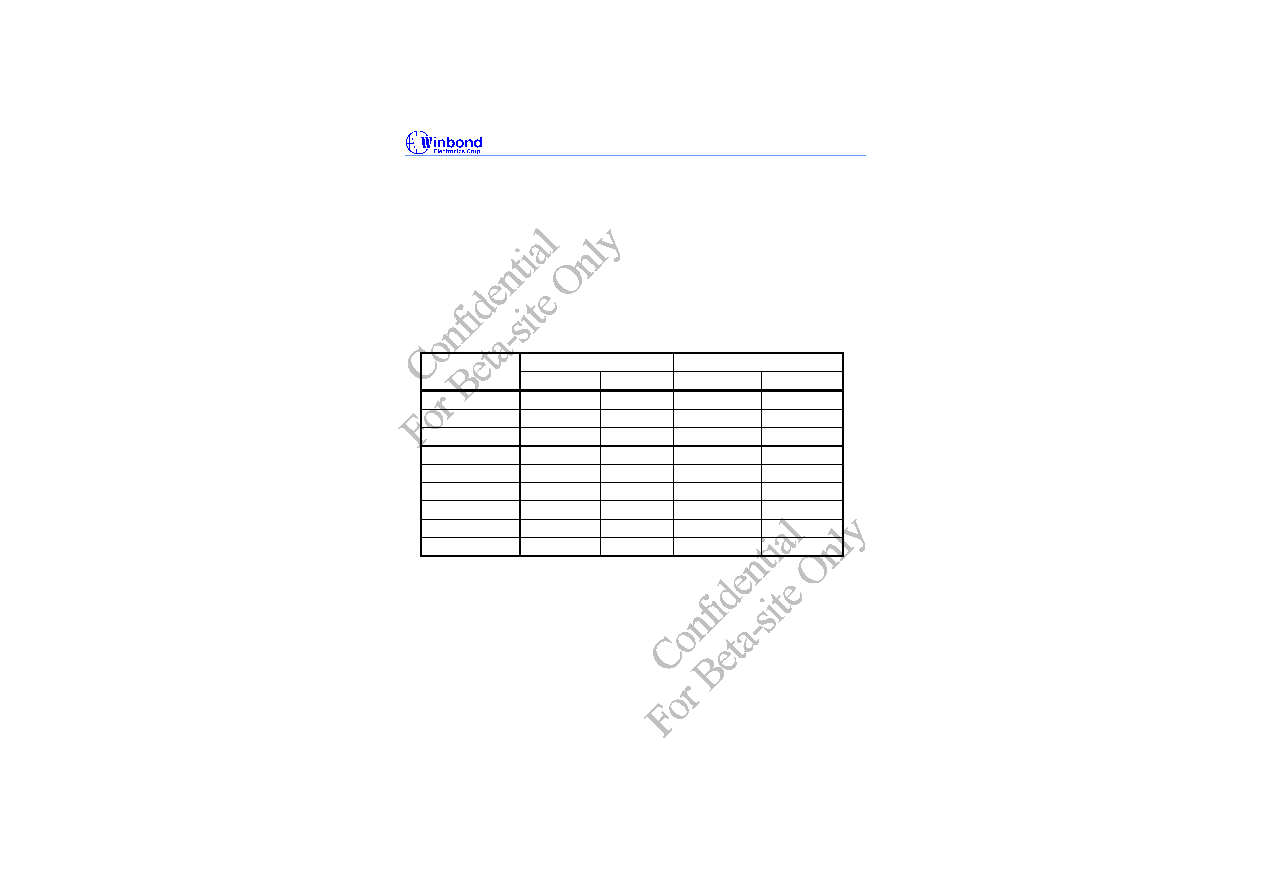

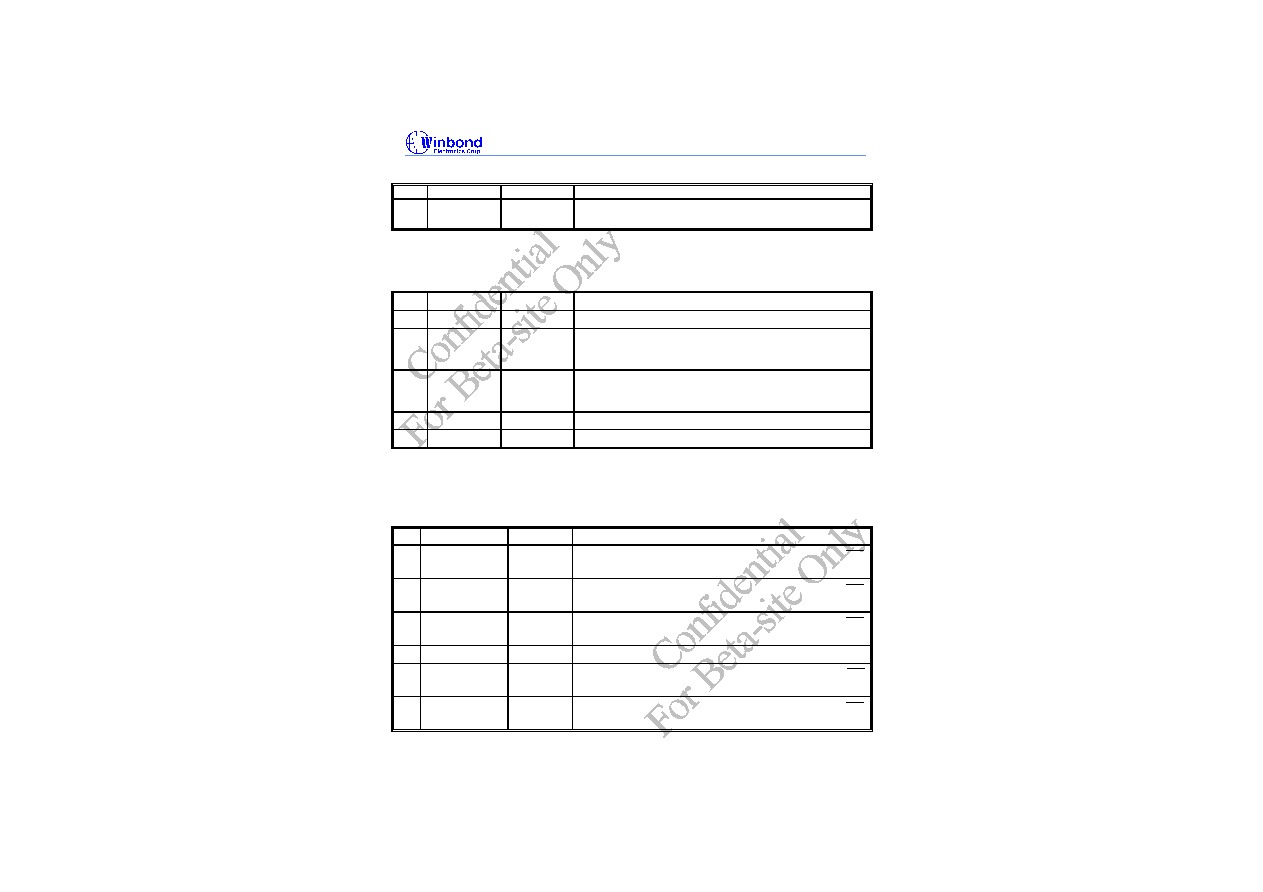

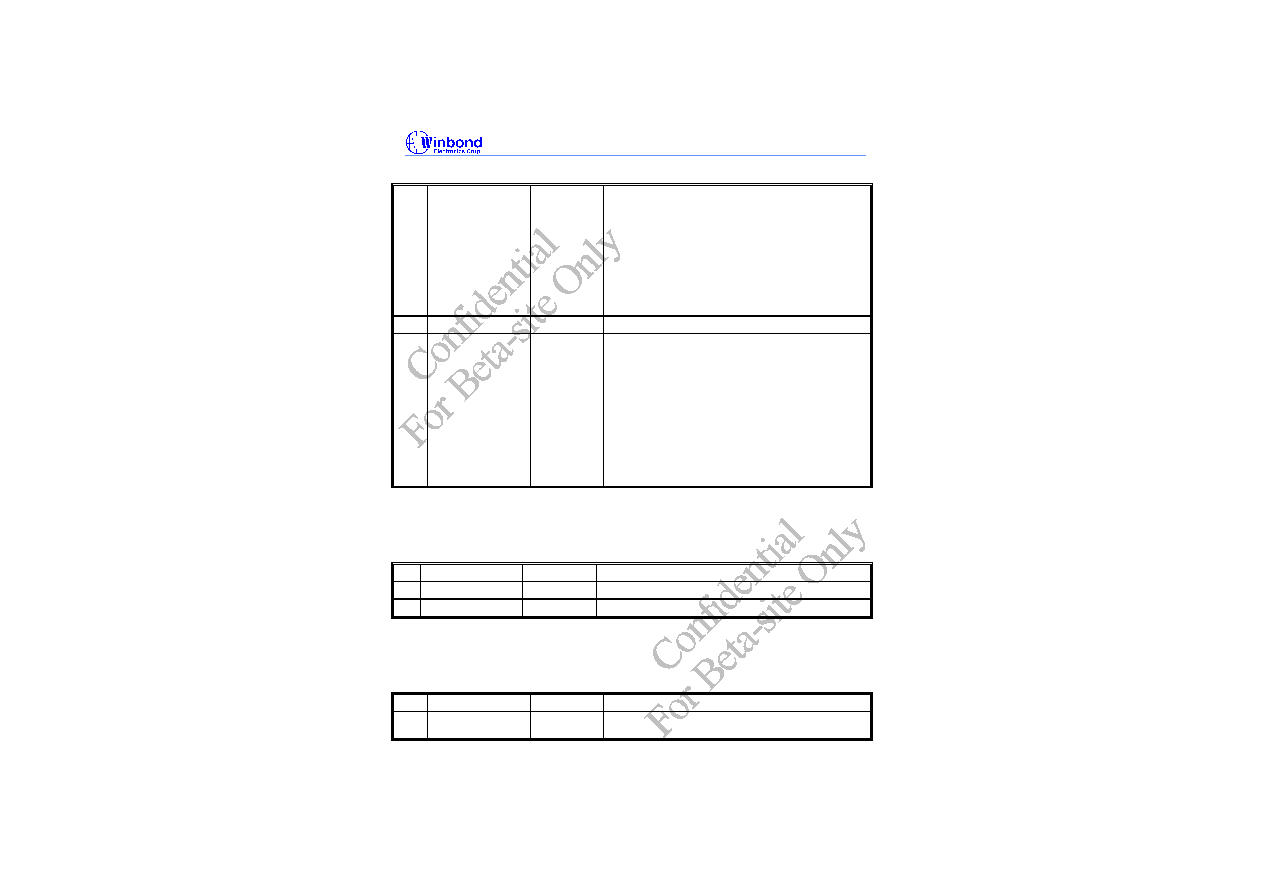

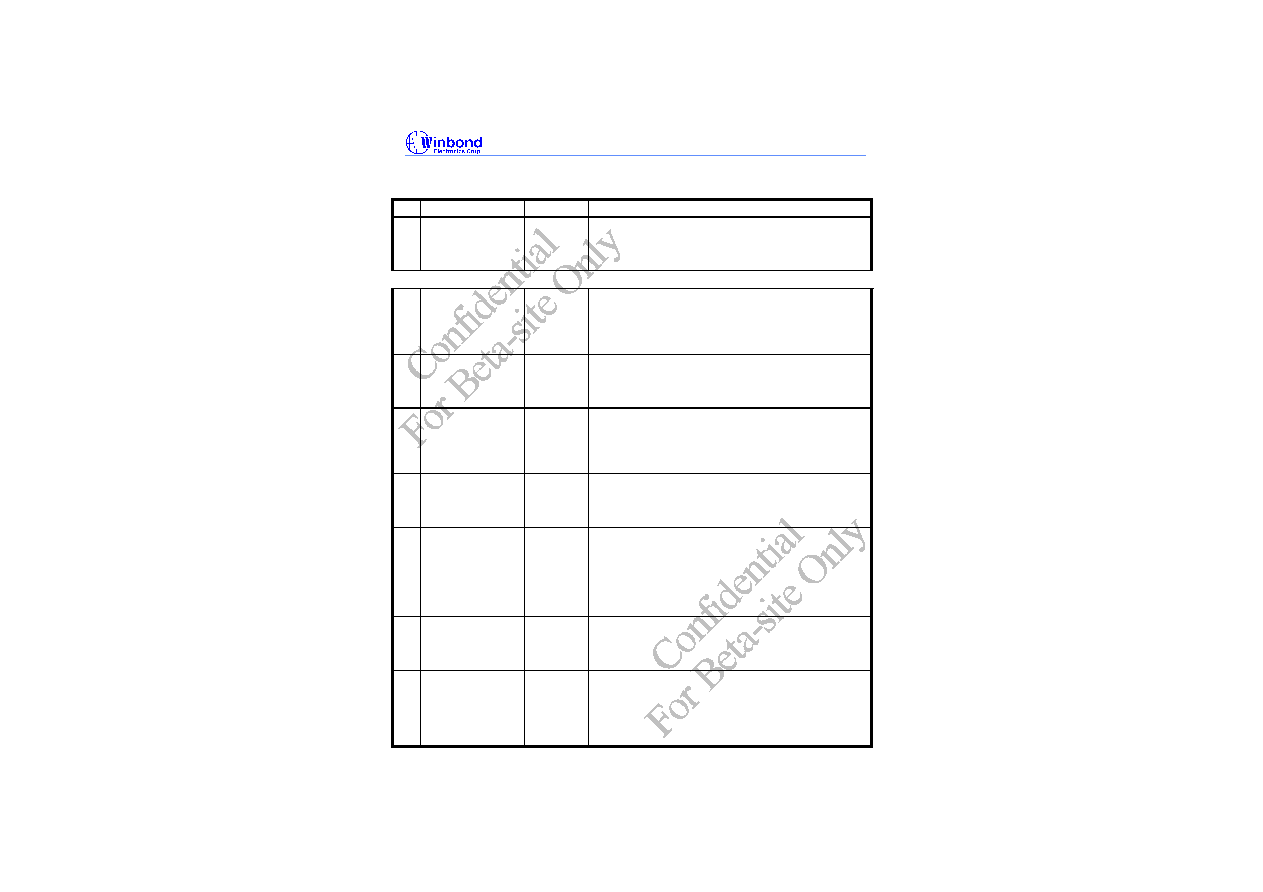

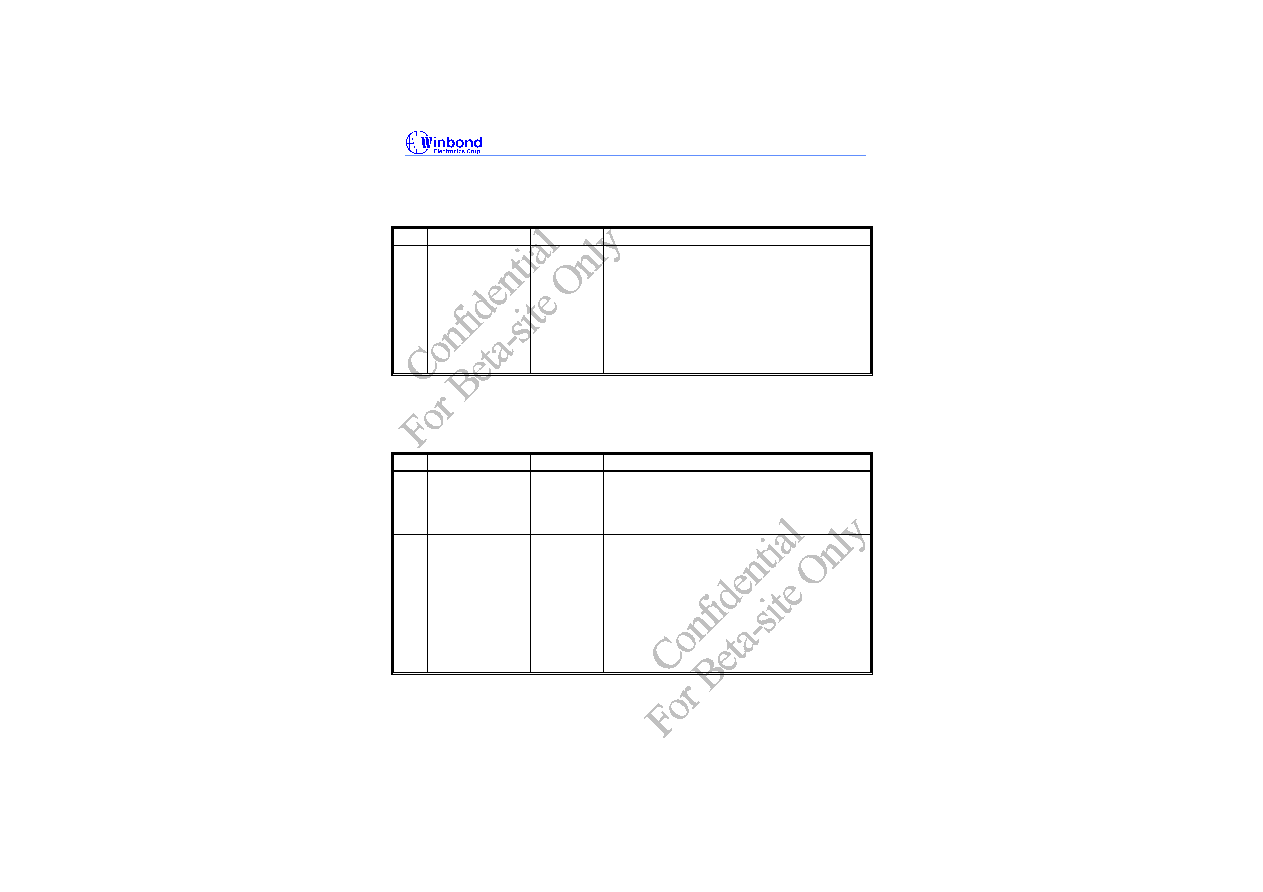

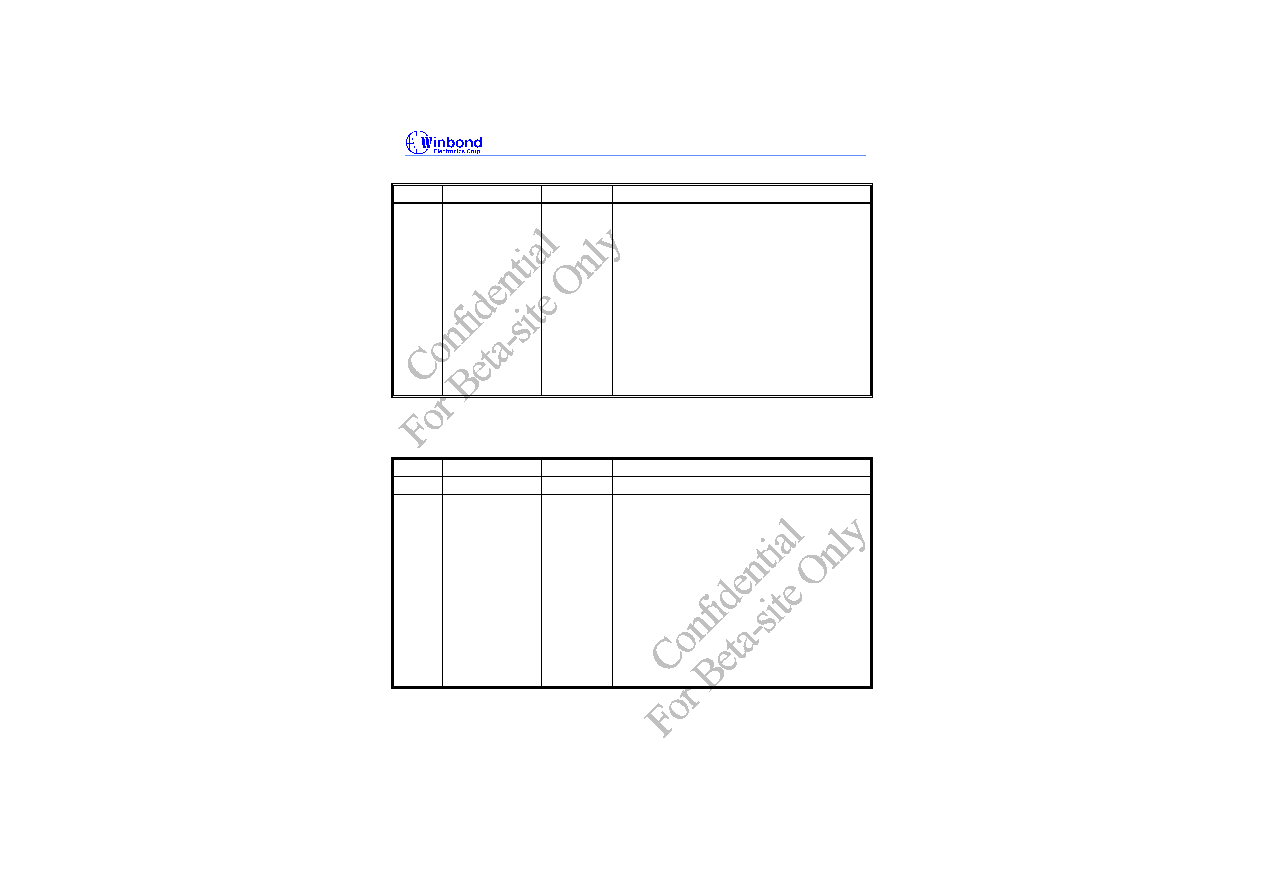

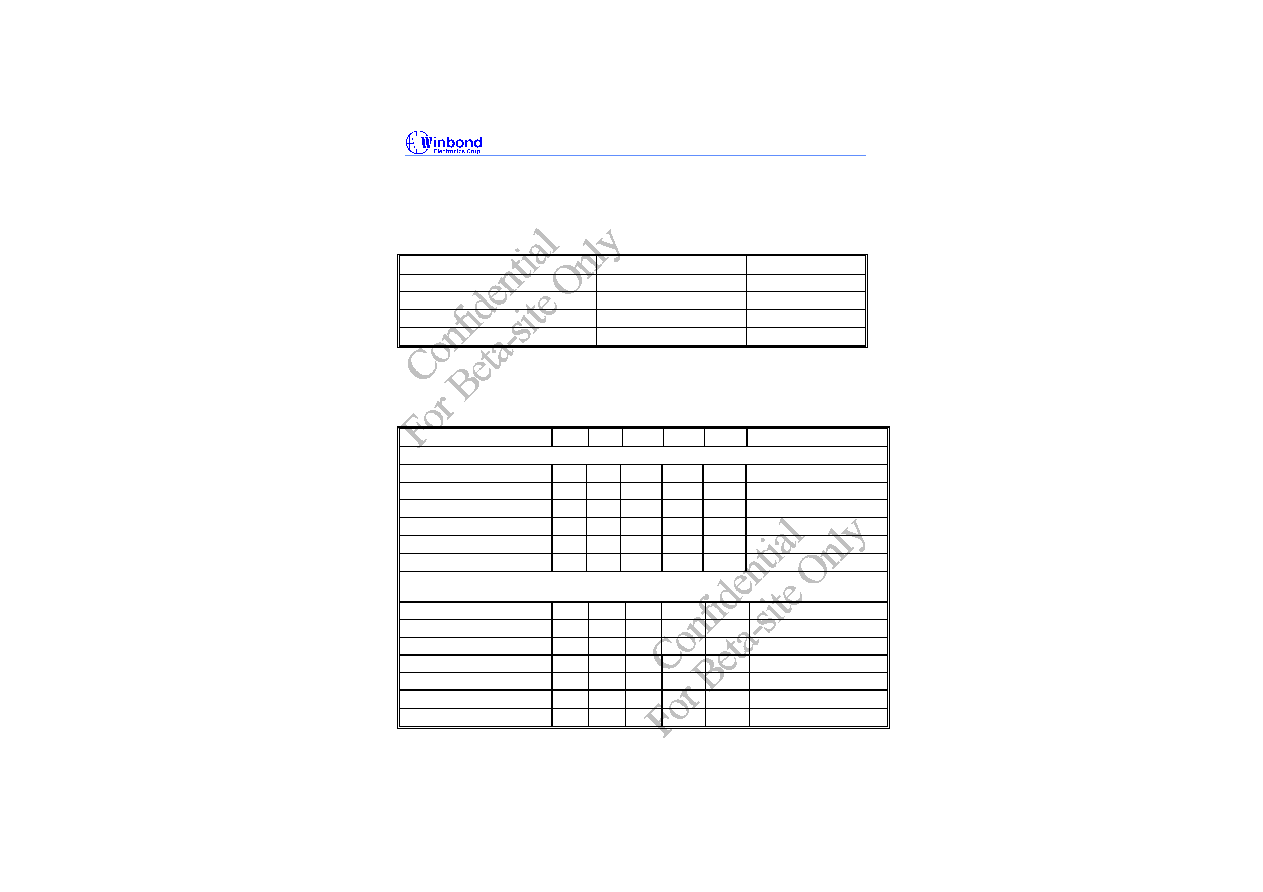

address. The format of the temperature data is show in Table 1.

Temperature

8-Bit Digital Output

9-Bit Digital Output

8-Bit Binary

8-Bit Hex

9-Bit Binary

9-Bit Hex

+125

�

C

0111,1101

7Dh

0,1111,1010

0FAh

+25

�

C

0001,1001

19h

0,0011,0010

032h

+1

�

C

0000,0001

01h

0,0000,0010

002h

+0.5

�

C

-

-

0,0000,0001

001h

+0

�

C

0000,0000

00h

0,0000,0000

000h

-0.5

�

C

-

-

1,1111,1111

1FFh

-1

�

C

1111,1111

FFh

1,1111,1110

1FFh

-25

�

C

1110,0111

E7h

1,1100,1110

1CEh

-55

�

C

1100,1001

C9h

1,1001,0010

192h

Table 1.

6.4.1 Monitor temperature from thermistor:

The W83L784R can connect three thermistors to measure three different envirment temperature. The

specification of thermistor should be considered to (1)

value is 3435K, (2) resistor value is 10K

ohms at 25

�

C. In the Figure 10, the themistor is connected by a serial resistor with 10K Ohms, then

connect to VREF (pin 17).

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-18 - Revision 0.54

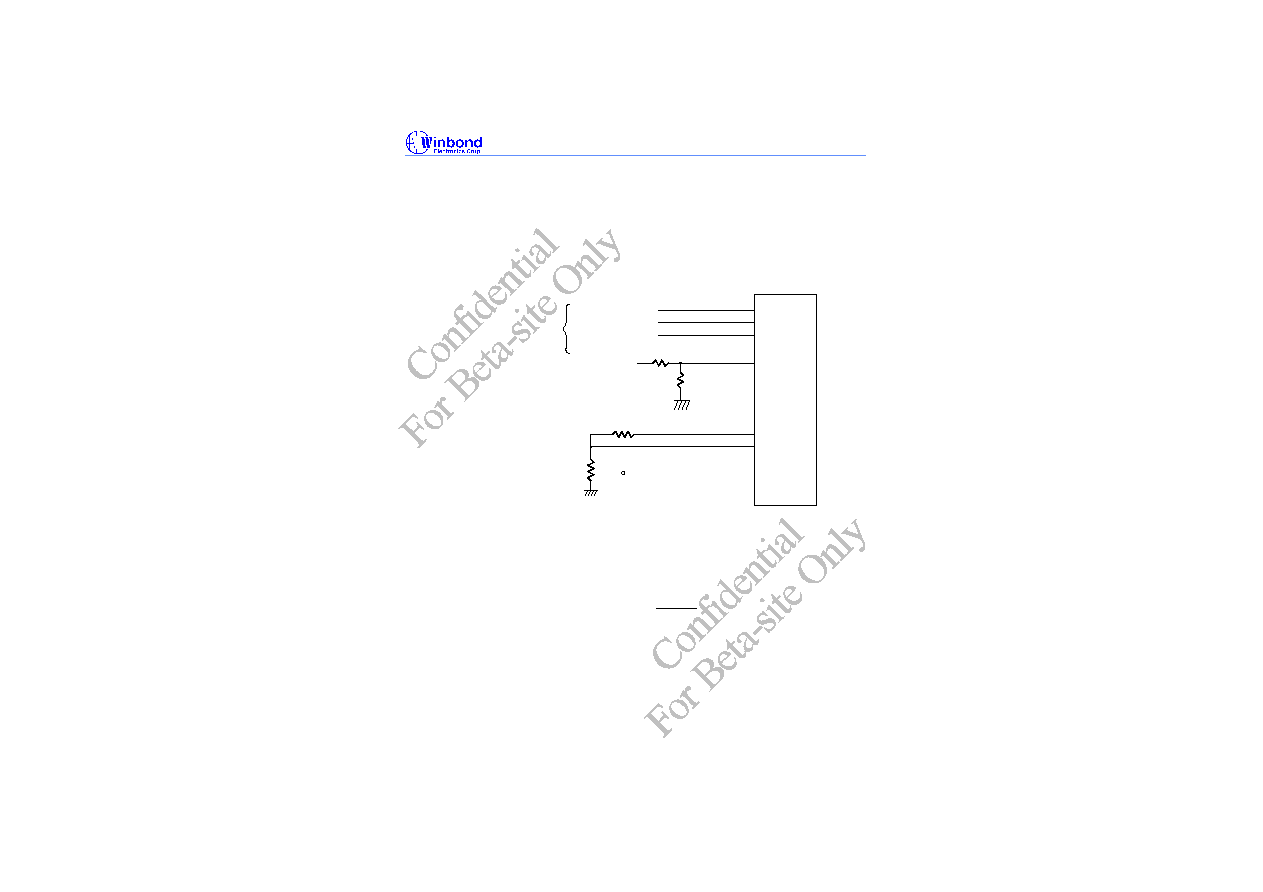

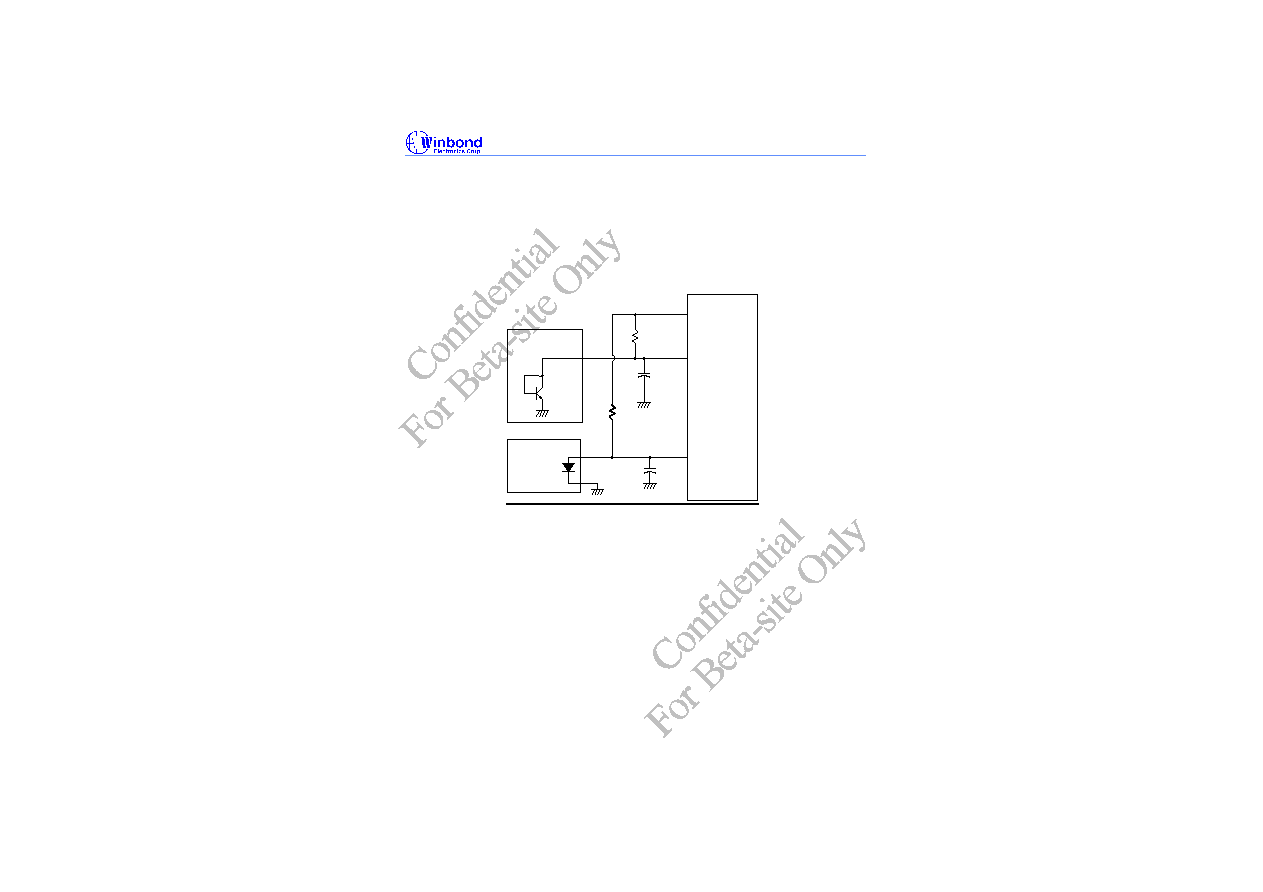

6.4.2 Monitor temperature from Pentium II

TM

thermal diode or bipolar transistor 2N3904

The W83L784R can alternate the thermistor to Pentium II

TM

(Deschutes) thermal diode interface or

transistor 2N3904 and the circuit connection is shown as Figure 12. The pin of Pentium II

TM

D- is

connected to power supply ground (GND) and the pin D+ is connected to pin PIIx in the W83L784R.

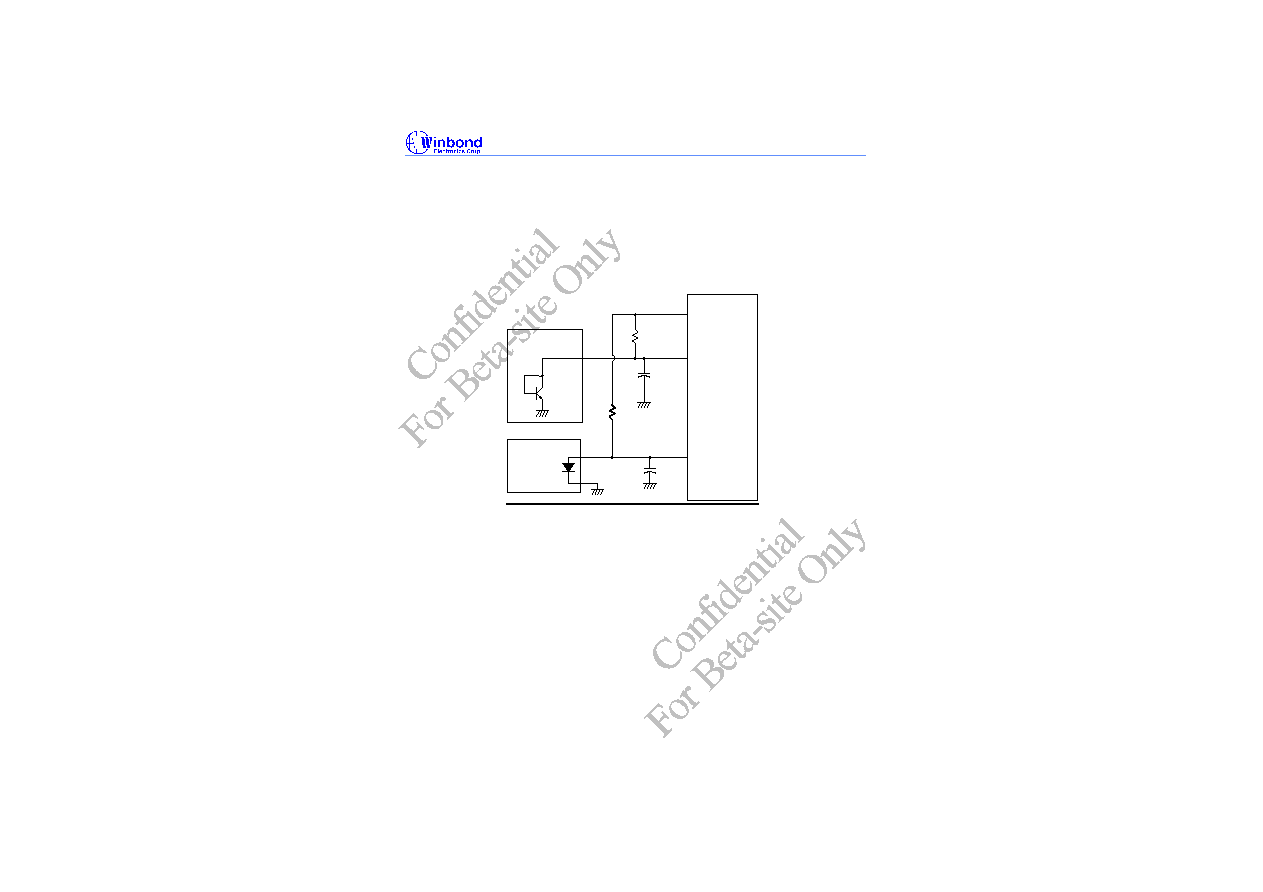

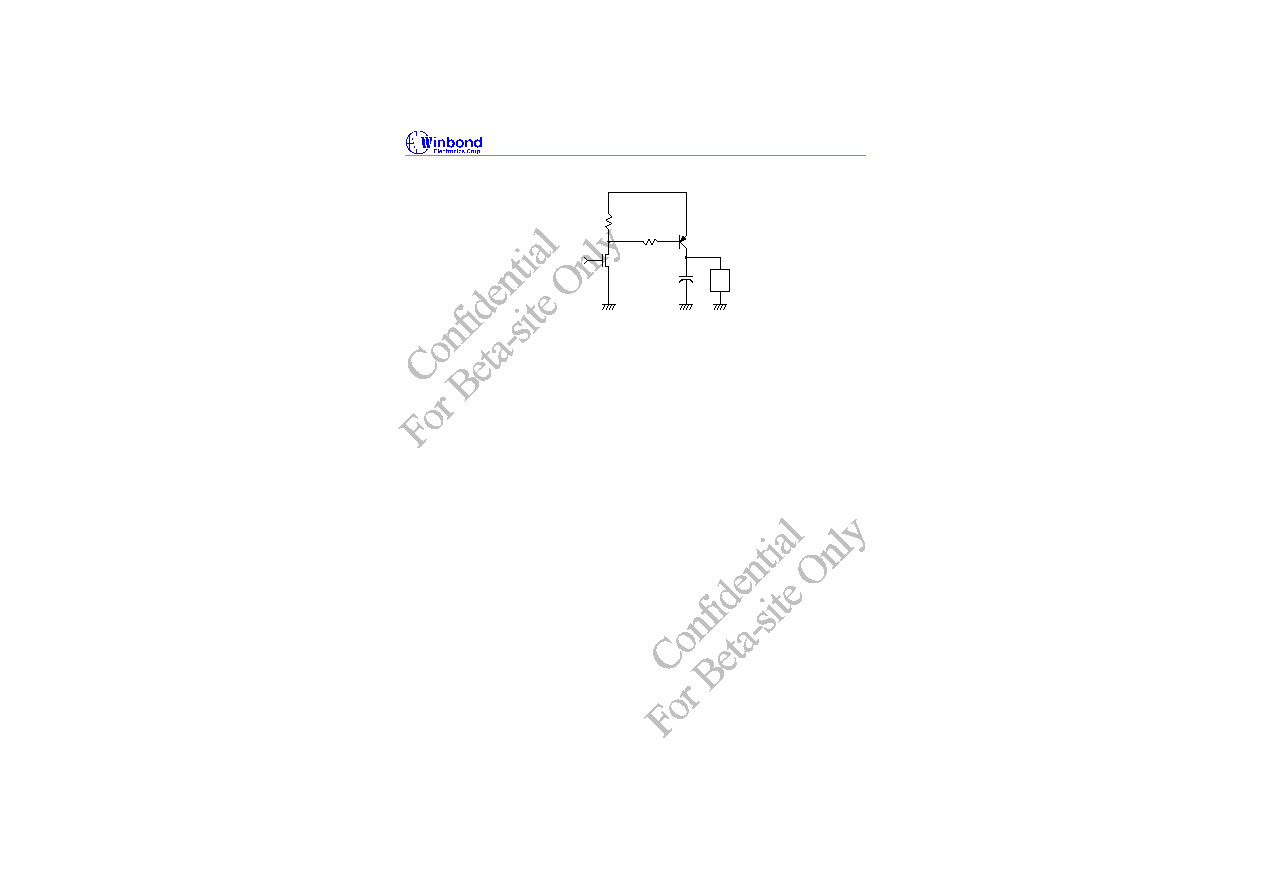

The resistor R=30K ohms should be connected to VREF to supply the diode bias current and the

bypass capacitor C=3300pF should be added to filter the high frequency noise. The transistor 2N3904

should be connected to a form with a diode, that is, the Base (B) and Collector (C) in the 2N3904

should be tied togeter to act as a thermal diode.

2N3904

C

E

B

R=30K, 1%

C=3300pF

Bipolar Transistor

Temperature Sensor

Pentium II

CPU

D+

D-

Therminal

Diode

C=3300pF

R=30K, 1%

VREF

PIITDx

PIITDx

OR

W83L784R

Figure 12.

6.4.3 Over Temperature

W83L784R provides two external thermal sensors to detect temperature. When detected

temperature exceeds the over-temperature value, pin OVT# will be asserted until the

temperature goes below the hysteresis temperature. Pin OVT# has 3 operating modes:

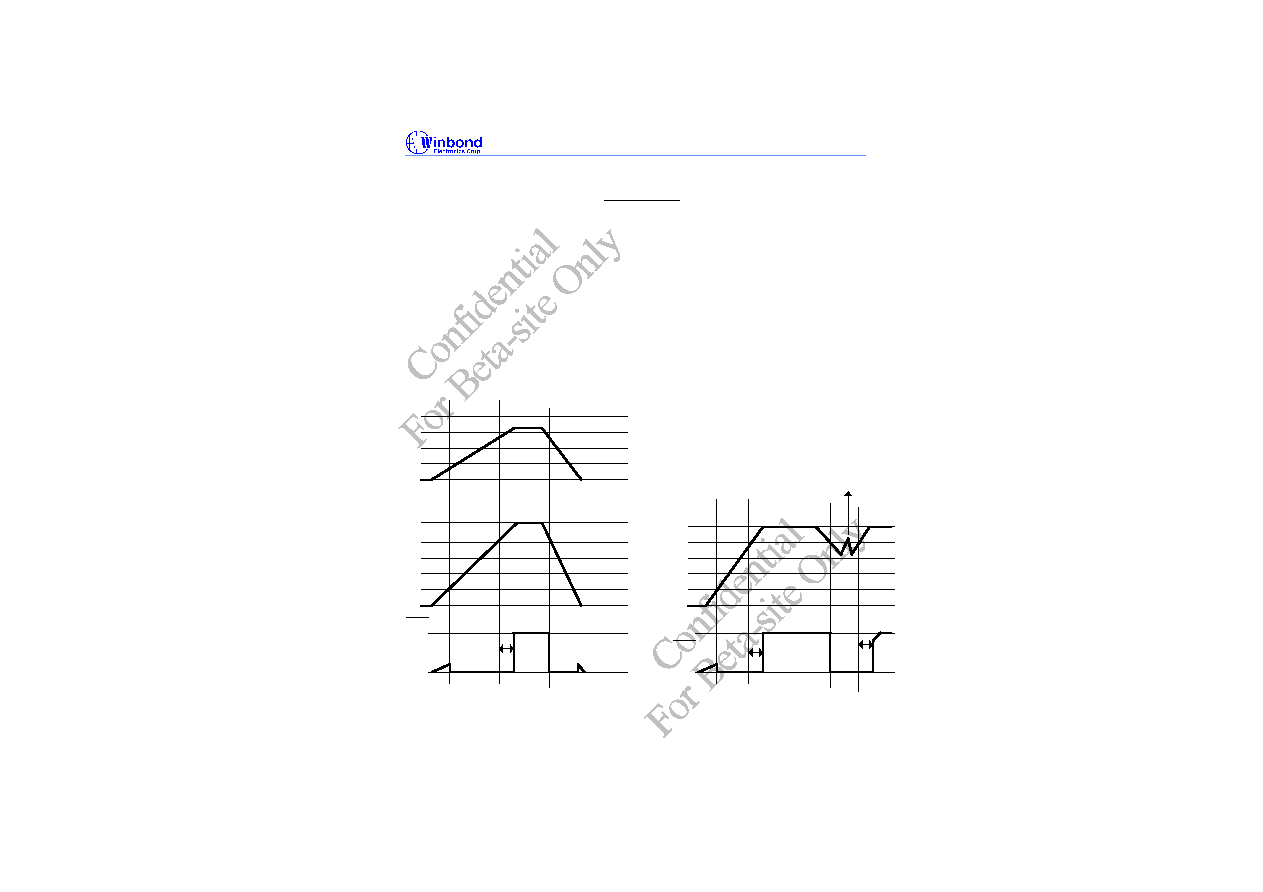

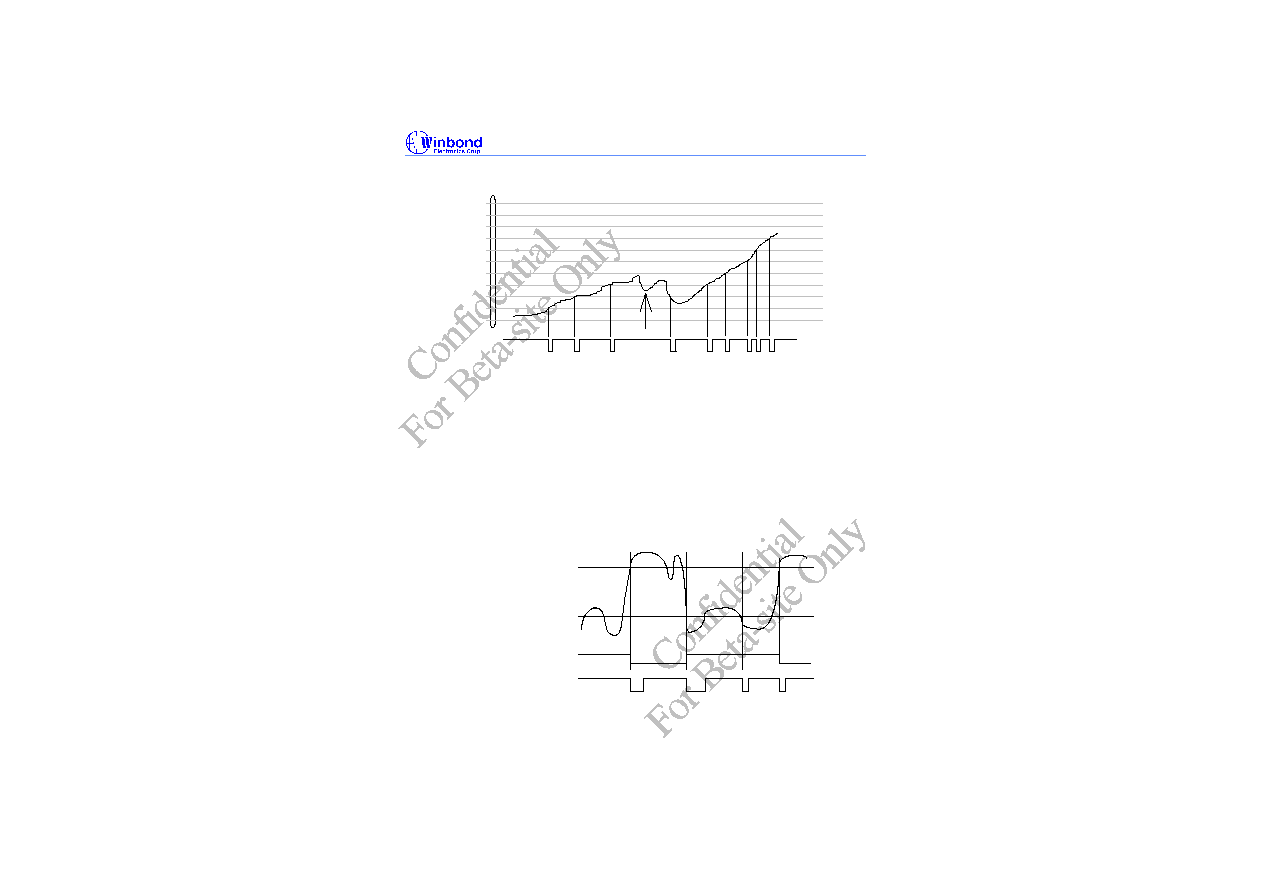

6.4.3.1 ACPI Mode :

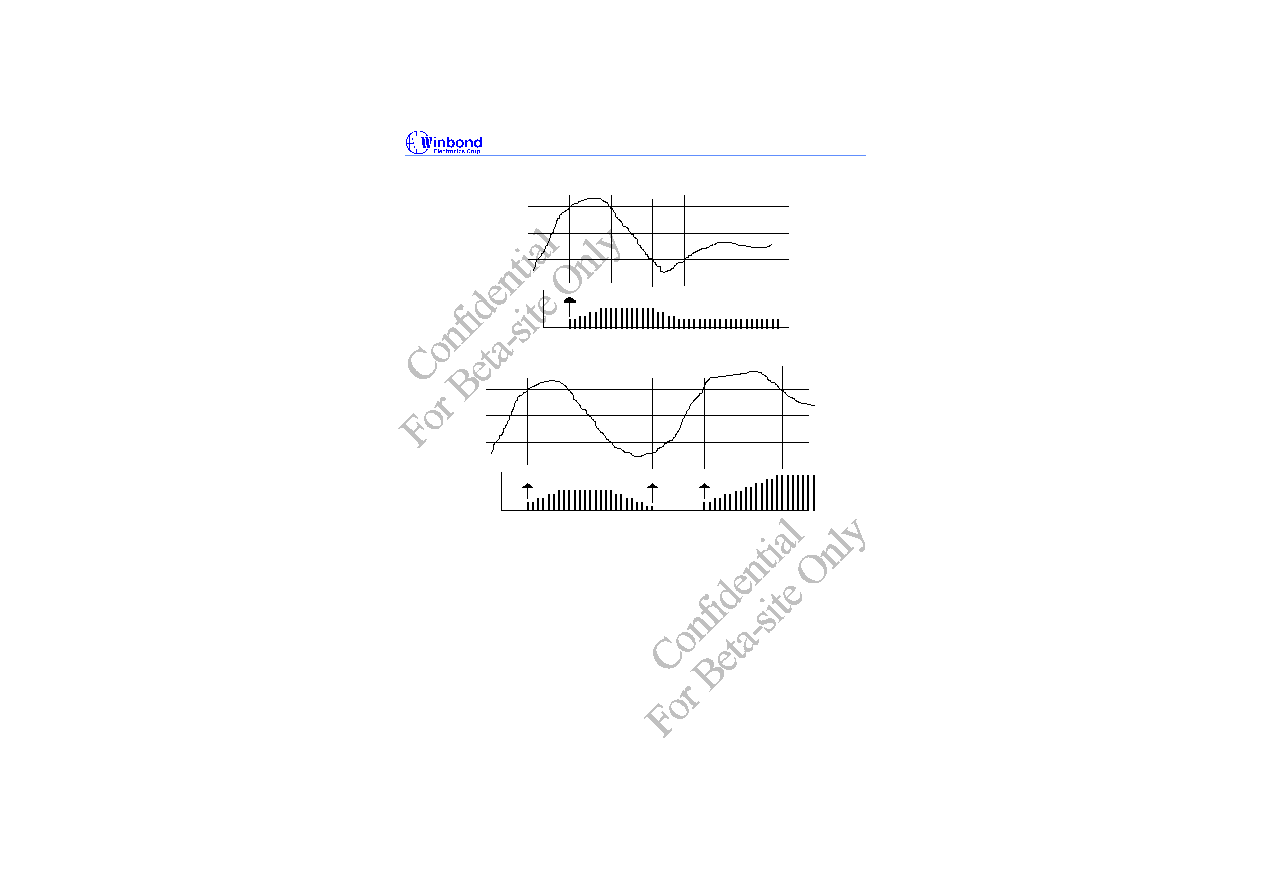

At this mode, temperature exceeding one level of temperature sepeartion , starting from 0

degree, causes the OVT# output activated. OVT# will be activated again once temperature

exceeding the next level. OVT# output will act the same manner when temperature goes down.

(Figure 13). The granularity of temperature separation between each OVT# output signal can be

programmed at Bank0 CR[4Fh].

The piority of this mode is higher than Comparator mode and Interrupt mode .

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-19 - Revision 0.54

0

10

20

30

40

5

0

100

90

80

70

60

OVT#

('C)

Current Temperature

Figure 13.

6.4.3.2 Comparator Mode :

At this mode, temperature exceeding T

O

causes the OVT# output activated until the temperature

is less than T

HYST

. ( Figure 14)

6.4.3.3 Interrupt Mode:

At this mode, temperature exceeding T

O

causes the OVT# output activated indefinitely until reset

by reading CPUT1 or CPUT2 registers. Temperature exceeding T

O

, then OVT# asserted, and

then temperature going below T

HYST

will also cause the OVT# activated indefinitely until reset by

reading temperature sensor2 or sensor 3 registers. Once the OVT# is activated by exceeding T

O

, then reset, if the temperature remains above T

HYST

, the OVT# will not be activated again.(

Figure 14)

T

HYST

*

*

*

*Interrupt Reset when CPUT1/CPUT2 is read

OVT#

OVT#

*

(Comparator Mode; default)

(Interrupt Mode)

To

Figure 14.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-20 - Revision 0.54

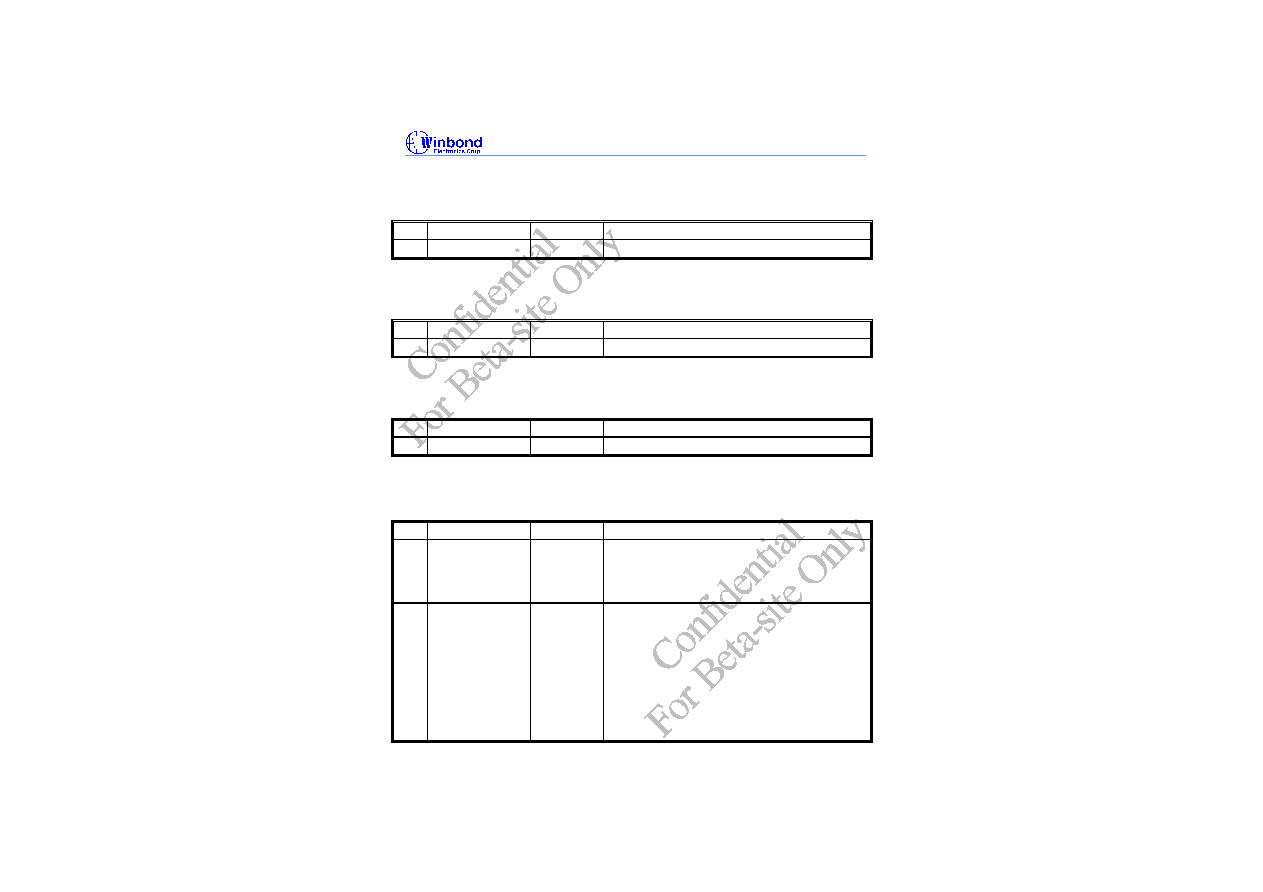

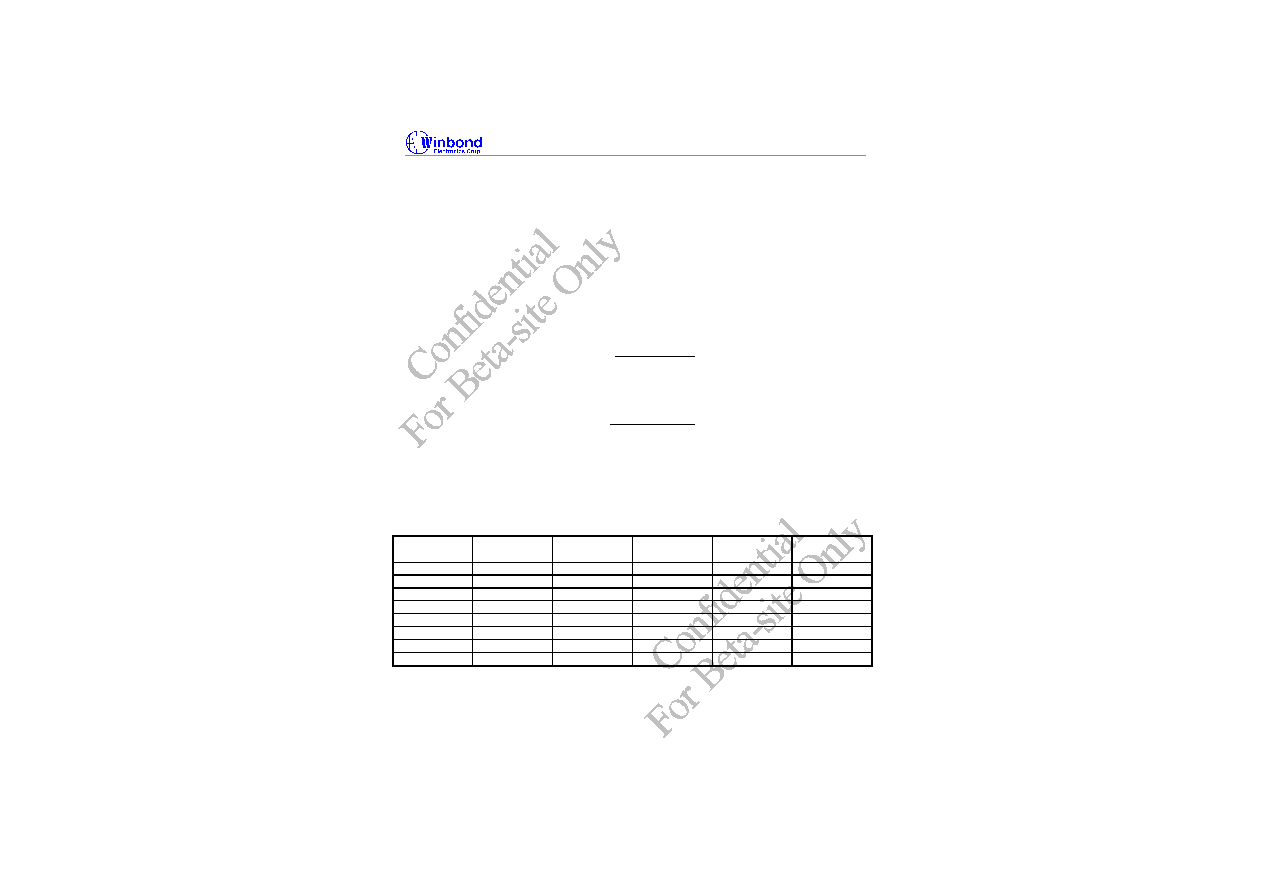

6.5 FAN Speed Count and FAN Speed Control

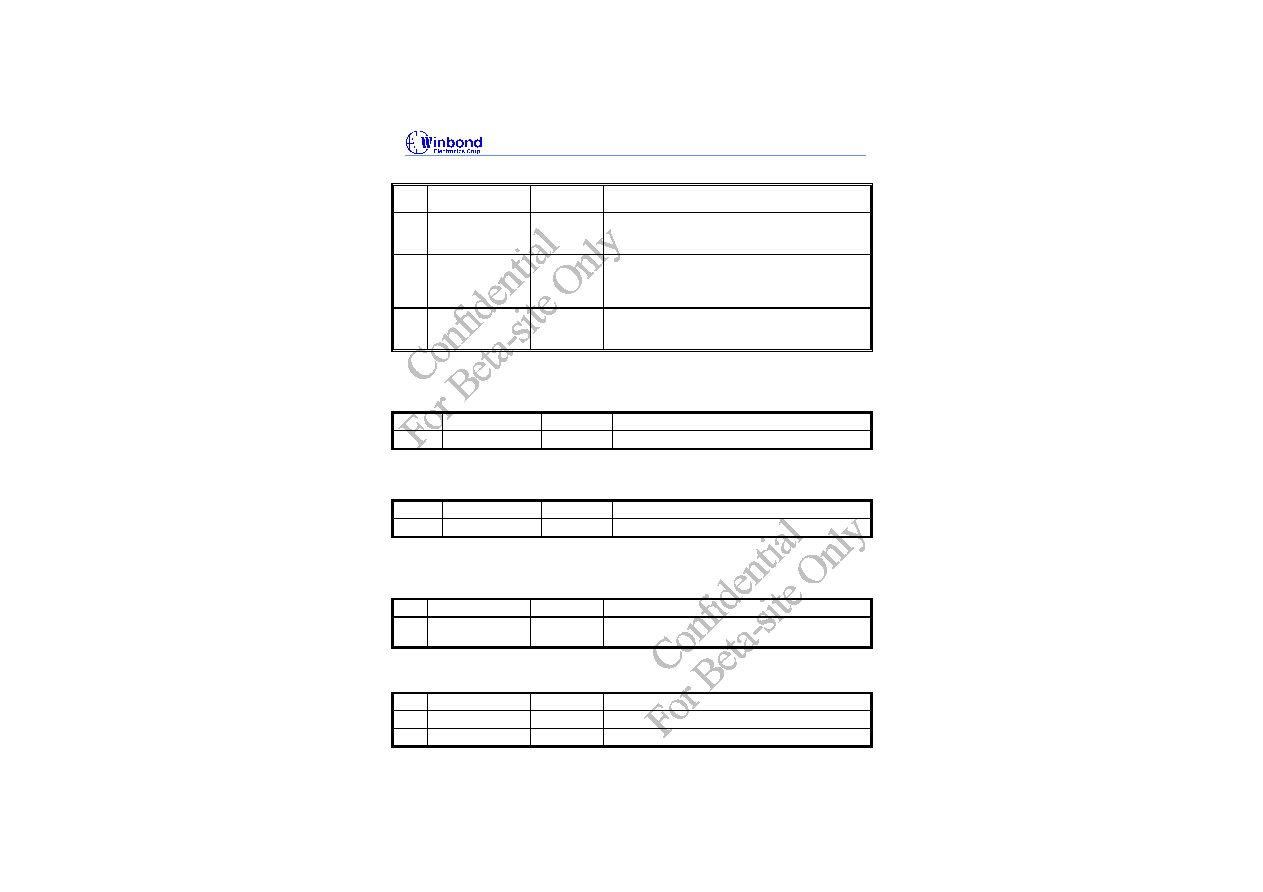

6.5.1 Fan speed count

Inputs are provides for signals from fans equipped with tachometer outputs. The level of these signals

should be set to TTL level, and maximum input voltage can not be over +5.5V. If the input signals

from the tachometer outputs are over the VCC, the external trimming circuit should be added to

reduce the voltage to obtain the input specification. The normal circuit and trimming circuits are

shown as Figure 15.

Determine the fan counter according to:

Count

RPM

Divisor

=

�

�

1 35

10

6

.

In other words, the fan speed counter has been read from register CR28 or CR29 or CR2A, the fan

speed can be evaluated by the following equation.

RPM

Count

Divisor

=

�

�

1 35

10

6

.

The default divisor is 2 and defined at CR49.bit0~2, bit4~6 which are three bits for divisor. That

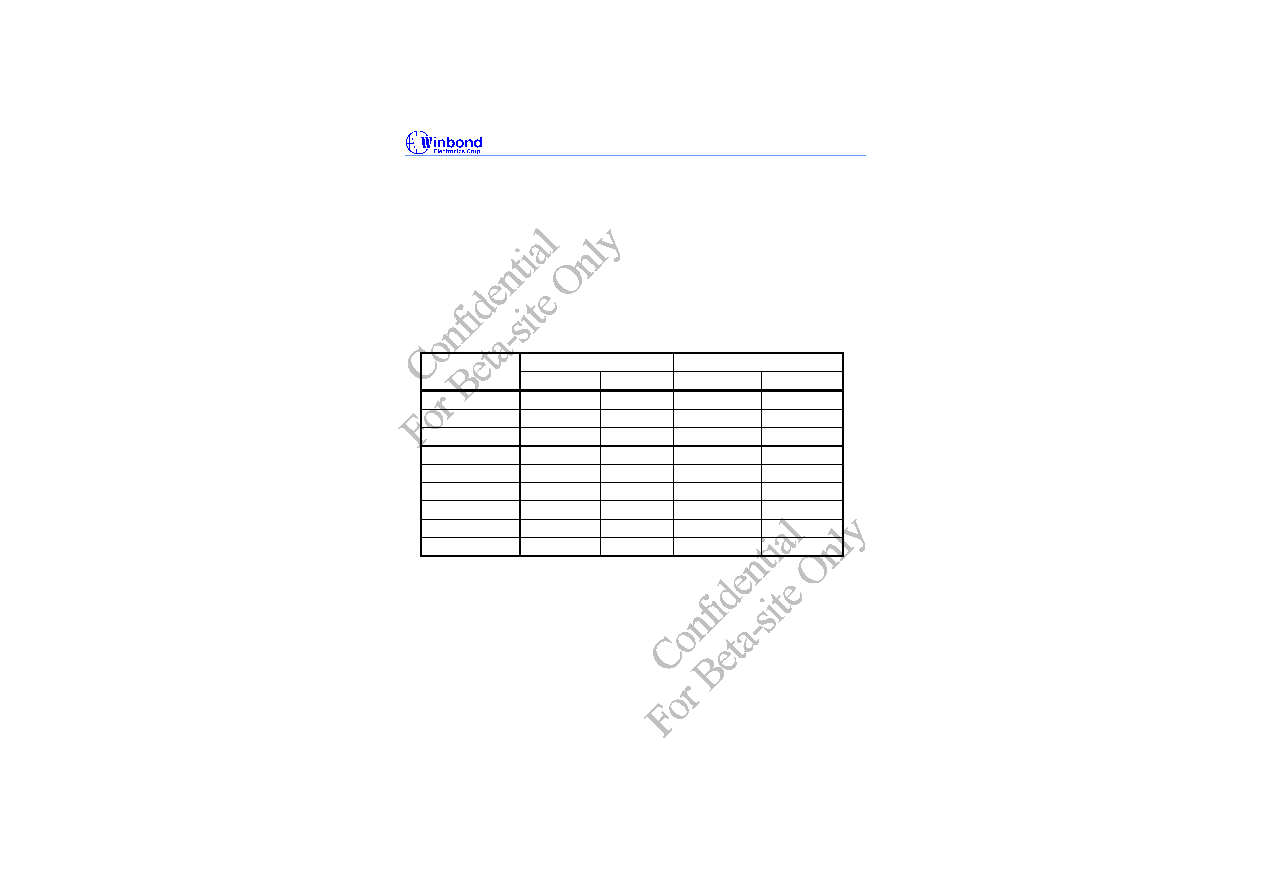

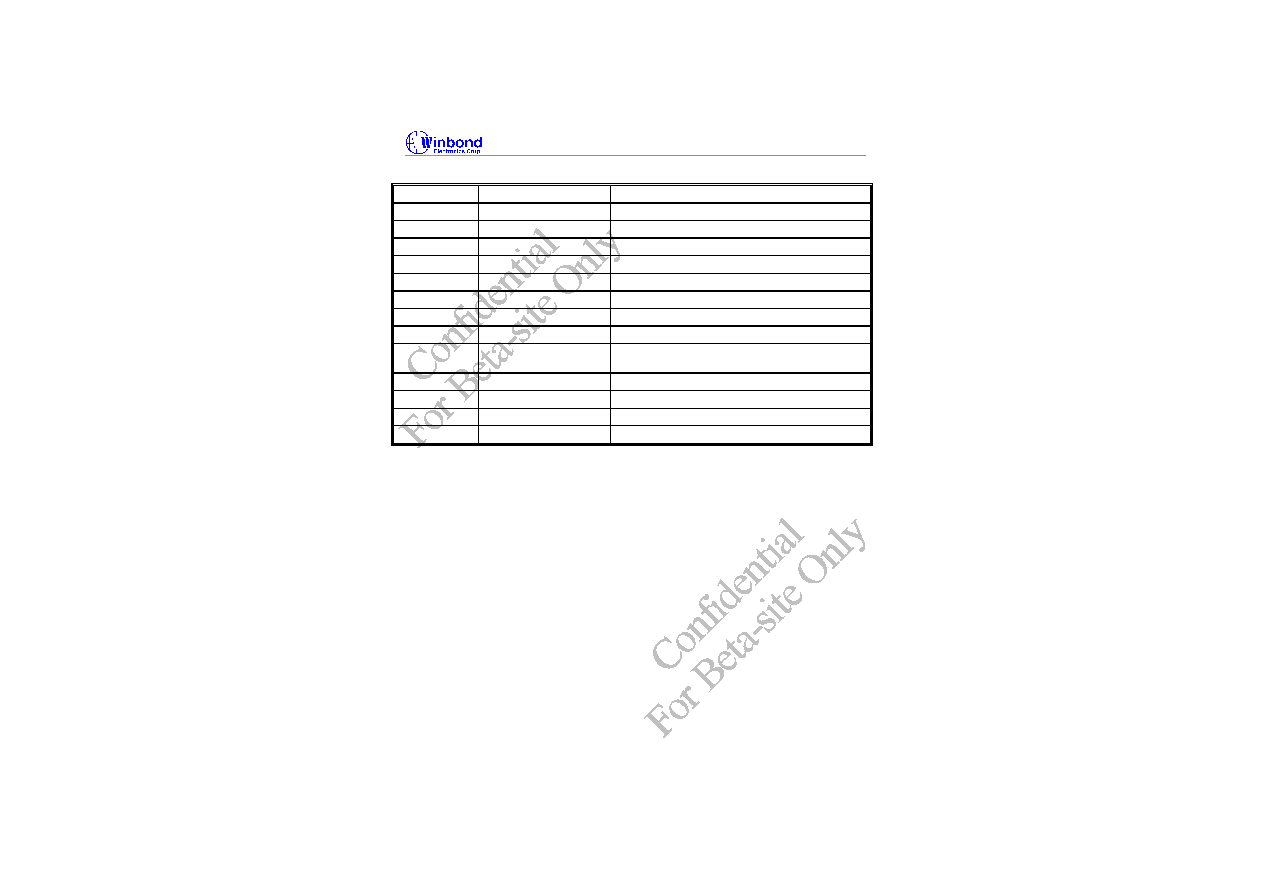

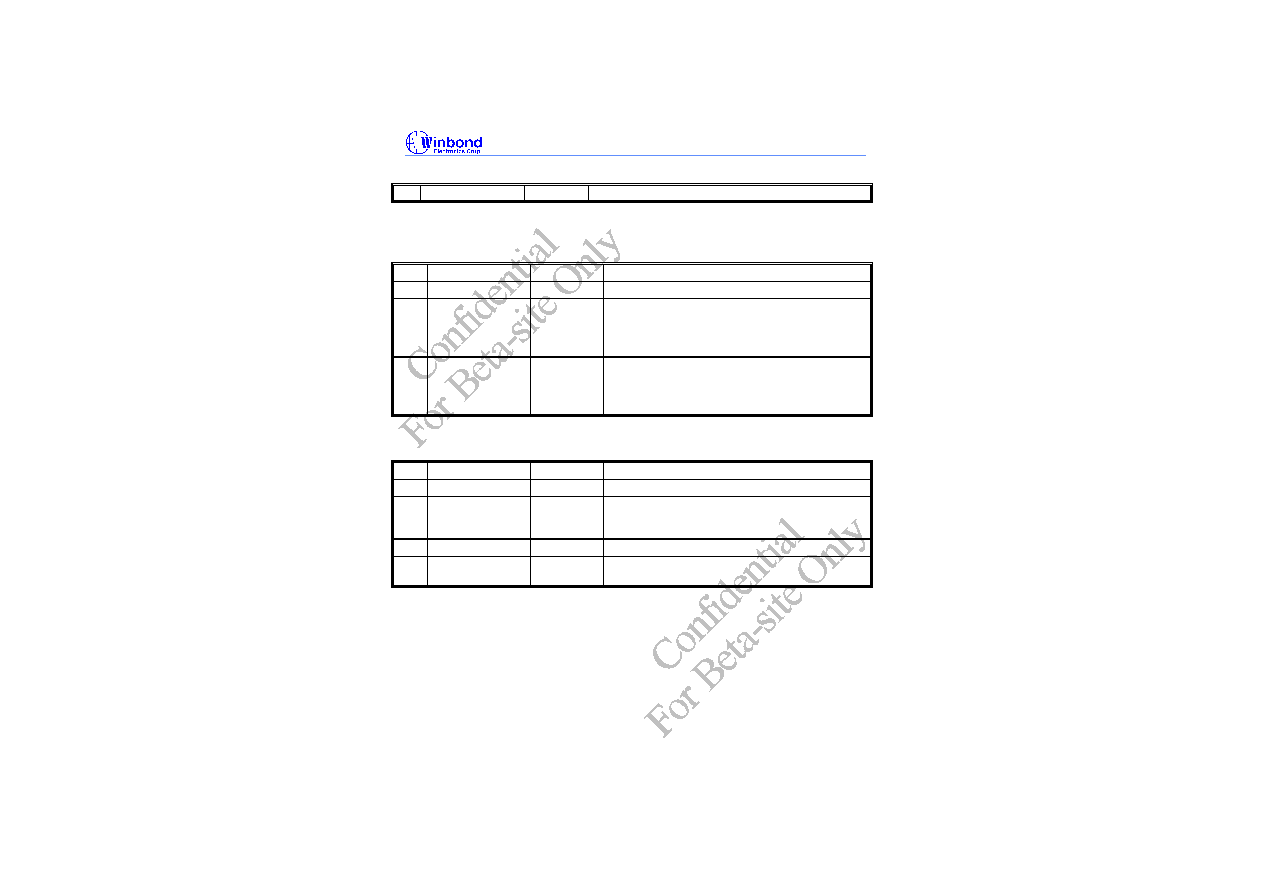

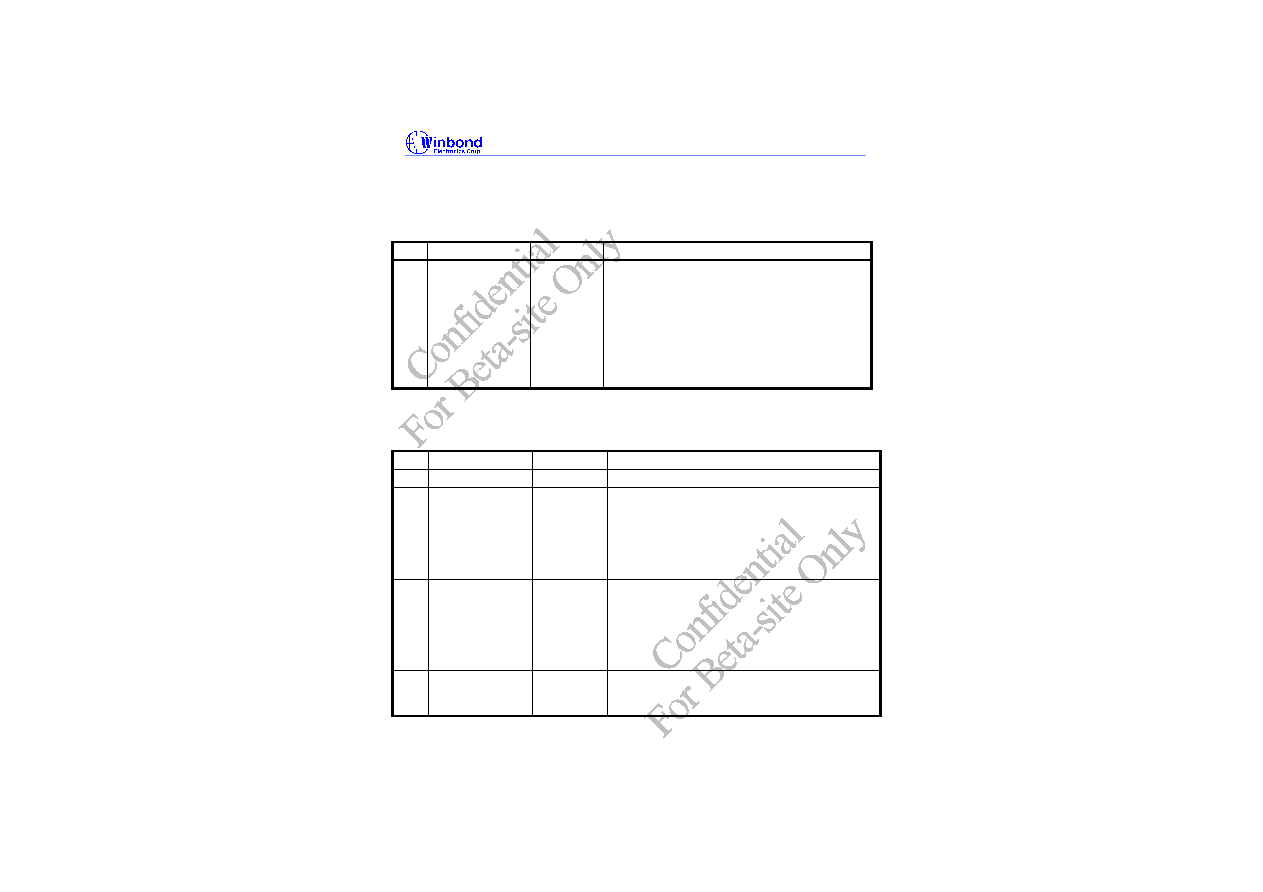

provides very low speed fan counter such as power supply fan. The followed table is an example for

the relation of divisor, PRM, and count.

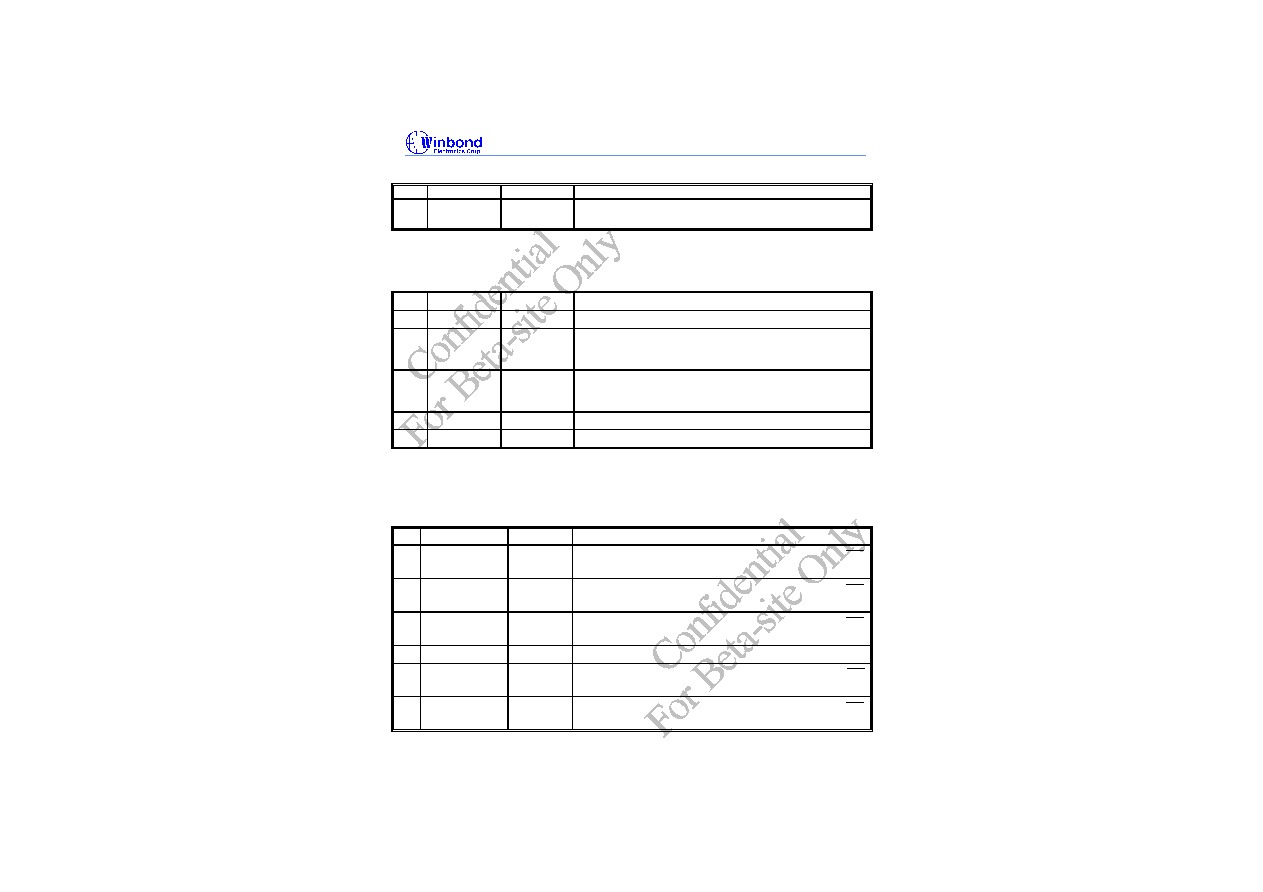

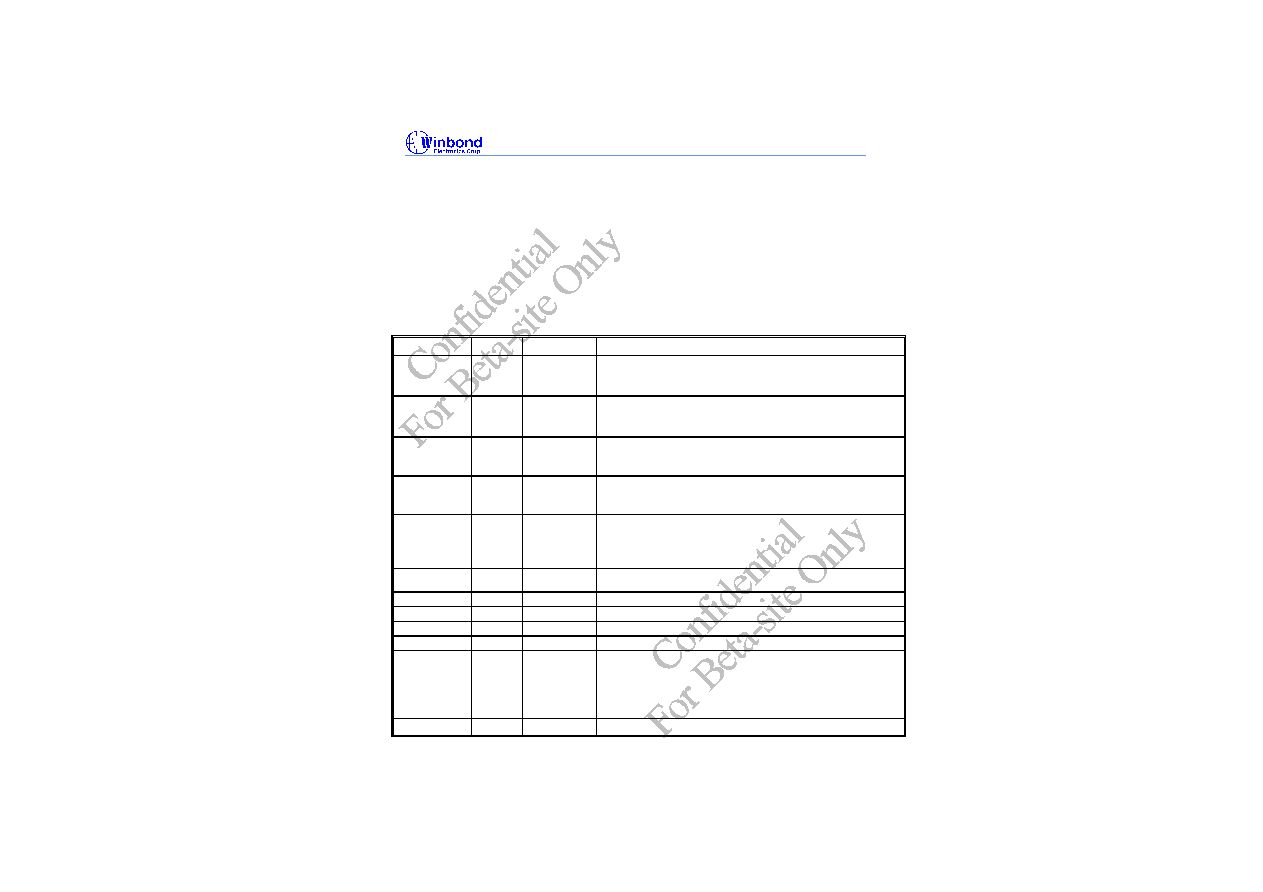

Divisor

Nominal

PRM

Time per

Revolution

Counts

70% RPM

Time for 70%

1

8800

6.82 ms

153

6160

9.74 ms

2 (default)

4400

13.64 ms

153

3080

19.48 ms

4

2200

27.27 ms

153

1540

38.96 ms

8

1100

54.54 ms

153

770

77.92 ms

16

550

109.08 ms

153

385

155.84 ms

32

275

218.16 ms

153

192

311.68 ms

64

137

436.32 ms

153

96

623.36 ms

128

68

872.64 ms

153

48

1246.72 ms

Table 2.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-21 - Revision 0.54

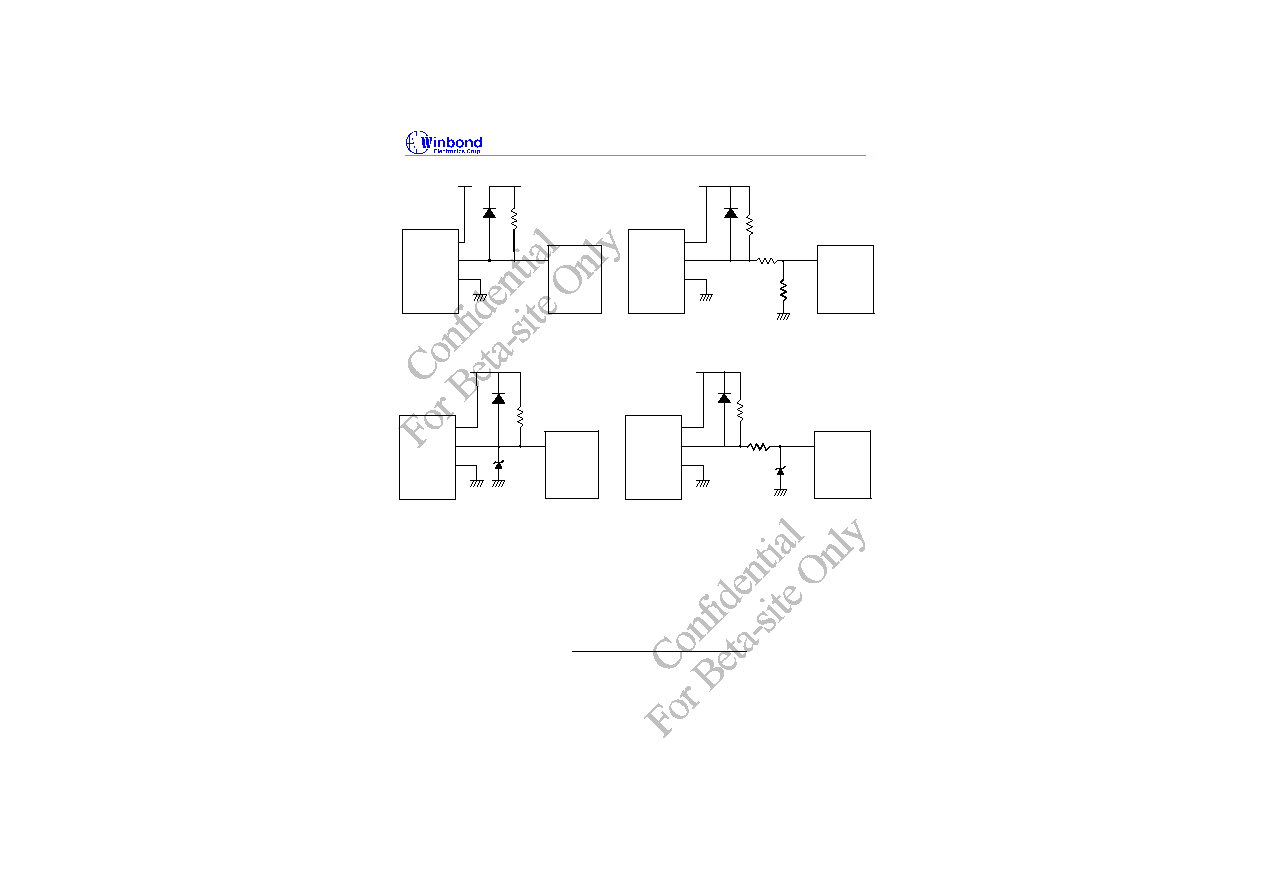

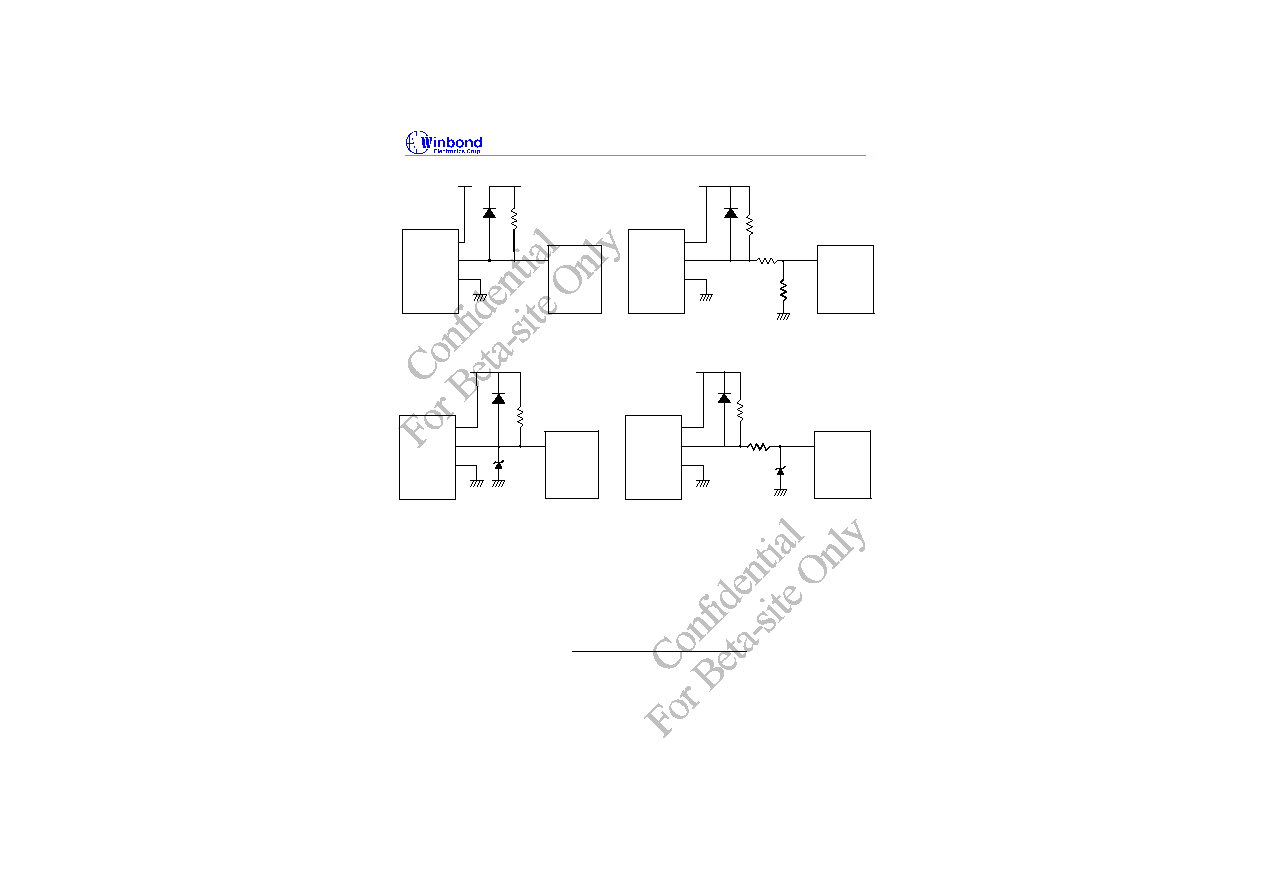

FAN

Connector

FAN Out

+5V

GND

Pull-up resister

4.7K Ohms

+5V

+5V

Fan Input

Pin 1 / 2

W83L784

R

FAN

Connector

FAN Out

+5V

GND

Pull-up resister

4.7K Ohms

+5V

Fan Input

Pin 1 / 2

W83L784R

2K

10K

Figure 15-2. Fan with Tach Pull-Up to +5V, or Totem-Pole

Output and Register Attenuator

Figure 15-1. Fan with Tach Pull-Up to +5V

FAN

Connector

FAN Out

+5V

GND

Pull-up resister

> 1K

+5V

Fan Input

Pin 1 / 2

W83L784

R

FAN

Connector

FAN Out

+5V

GND

Pull-up resister < 1K

or totem-pole output

+5V

Fan Input

Pin 1 / 2

W83L784R

> 1K

Figure 15-4. Fan with Tach Pull-Up to +5V, or

Totem-Pole Putput and Zener Clamp

Figure 15-3. Fan with Tach Pull-Up to +5V

and Zener Clamp

3.9V Zener

3.9V Zener

diode

diode

diode

diode

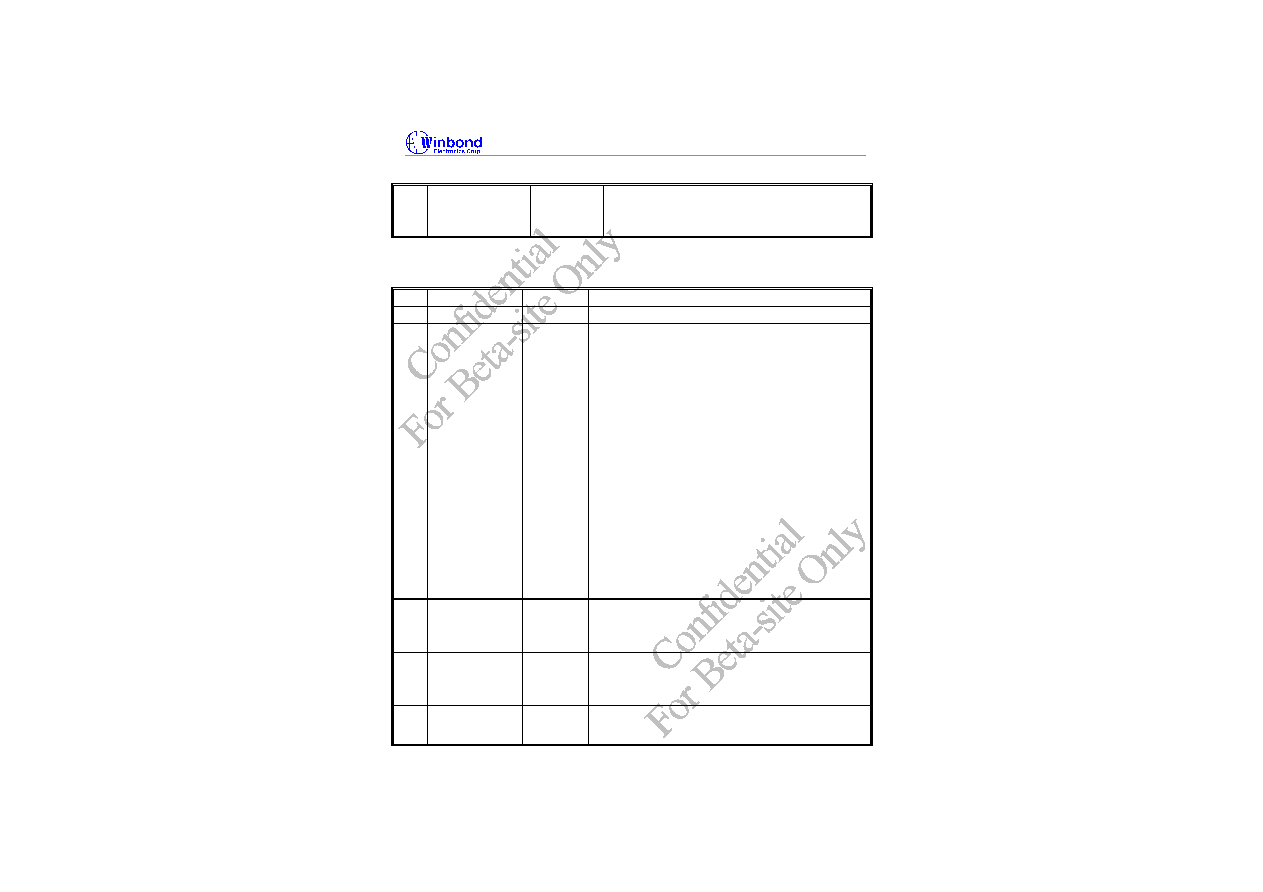

6.5.2 Fan speed control

The W83L784R provides four sets for fan PWM speed control. The duty cycle of PWM can be

programmed by a 8-bit register which are defined in the Bank0 CR81h and CR83h. The default duty

cycle is set to 100%, that is, the default 8-bit registers is set to FFh. The expression of duty can be

represented as follows.

Duty

cycle

Programmed 8 - bit Register Value

255

-

=

�

(%)

1 0 0 %

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-22 - Revision 0.54

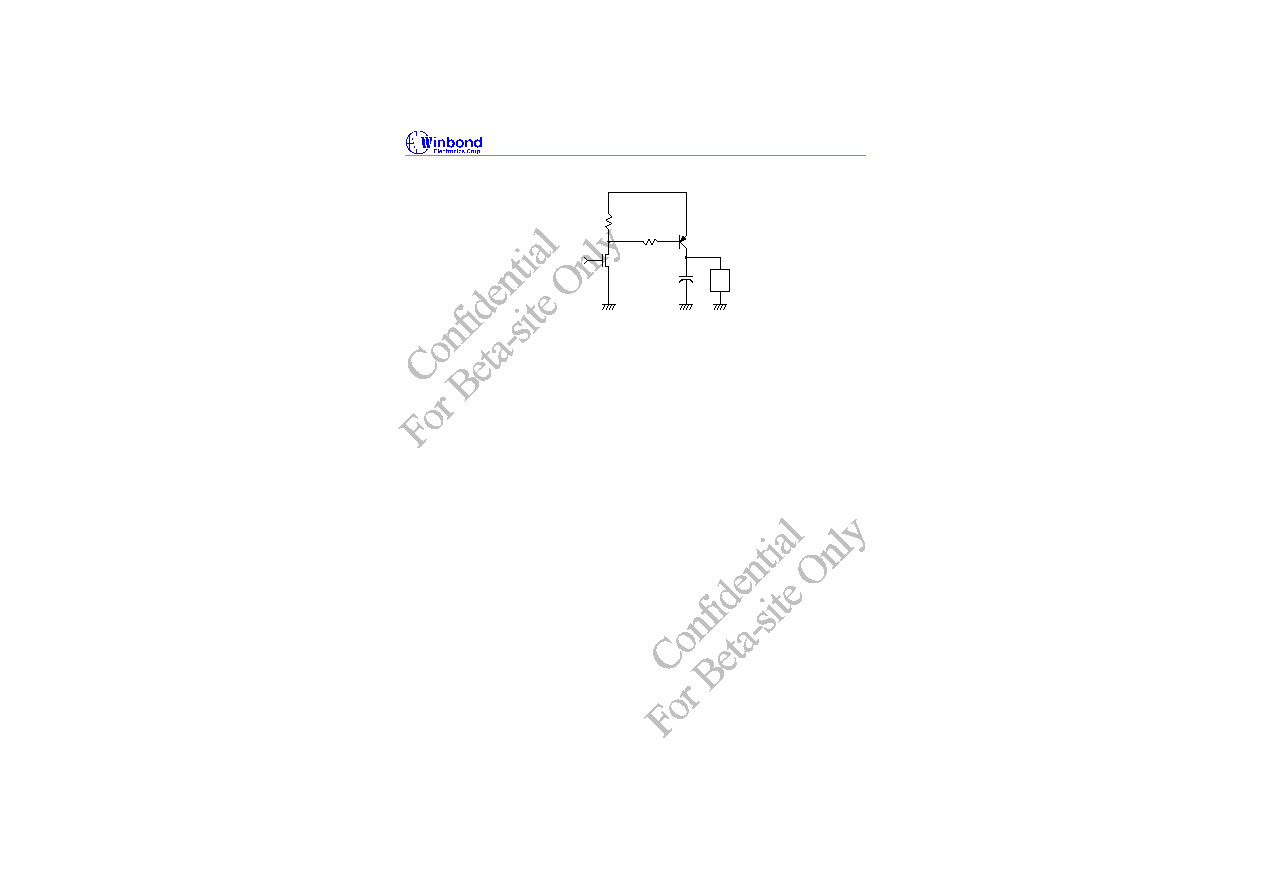

+5V

FAN

R1

R2

NMOS

PNP Transistor

C

+

-

PWM Clock Input

D

S

G

Figure 16.

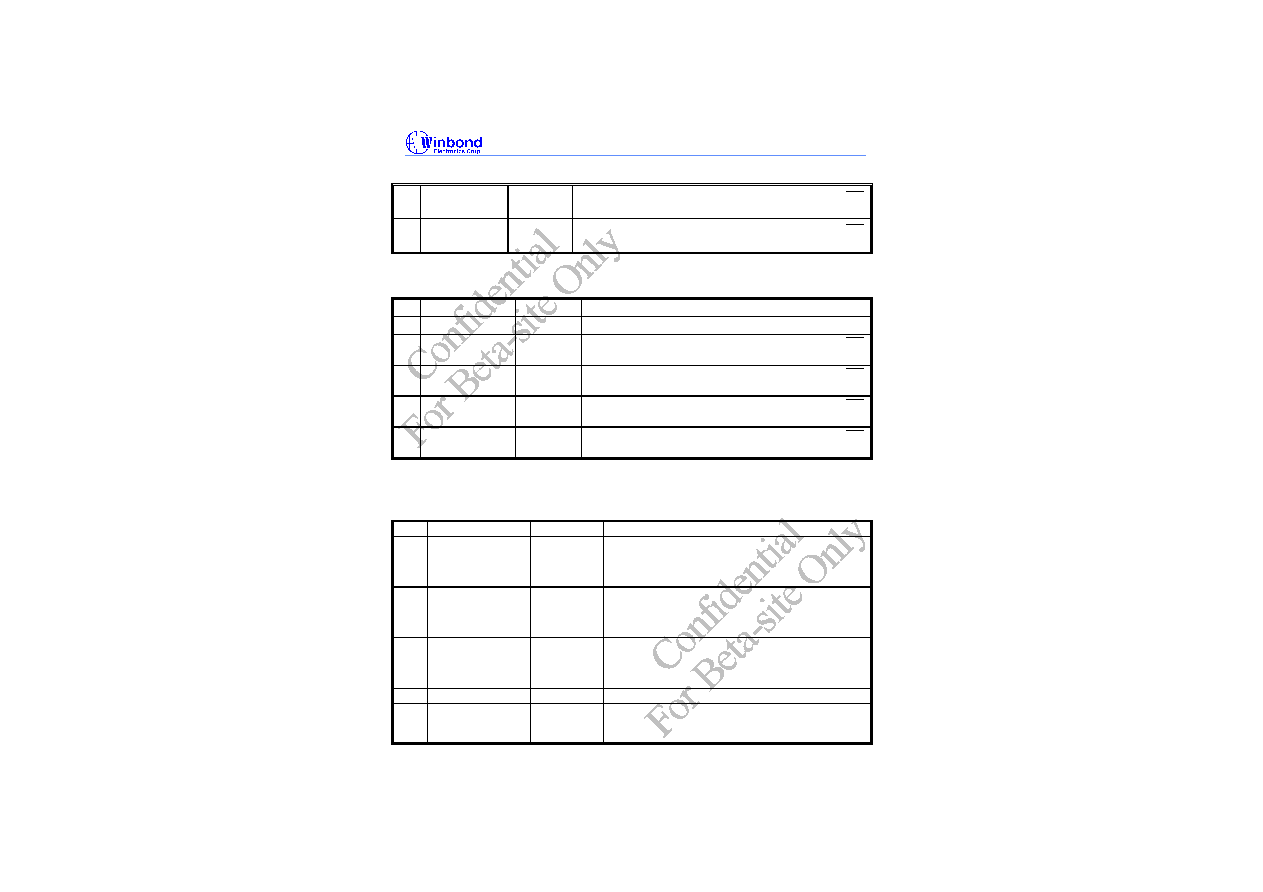

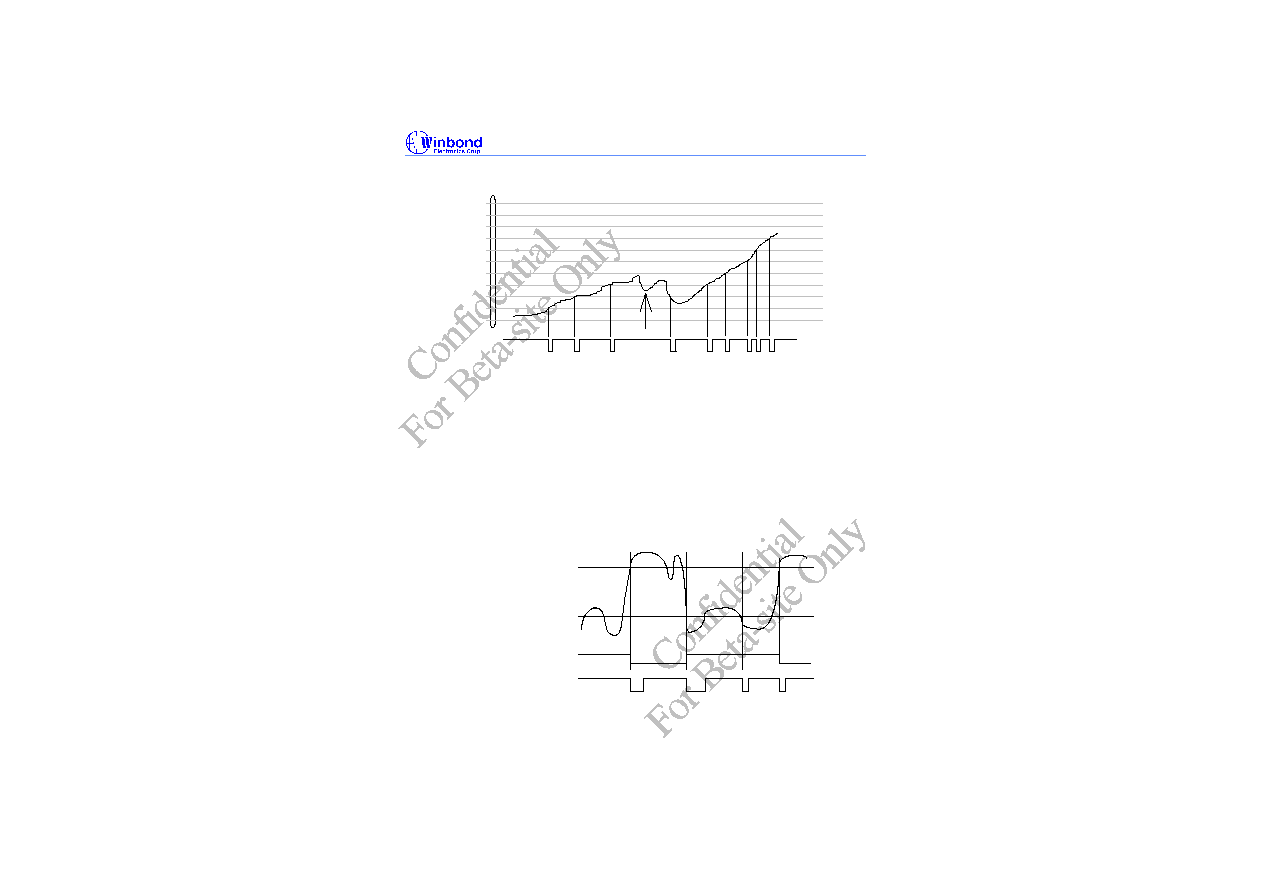

6.5.3 Smart Fan Control

Smart Fan Control provides two mechanisms. One is Thermal Cruise mode and the other is

Fan Speed Cruise mode.

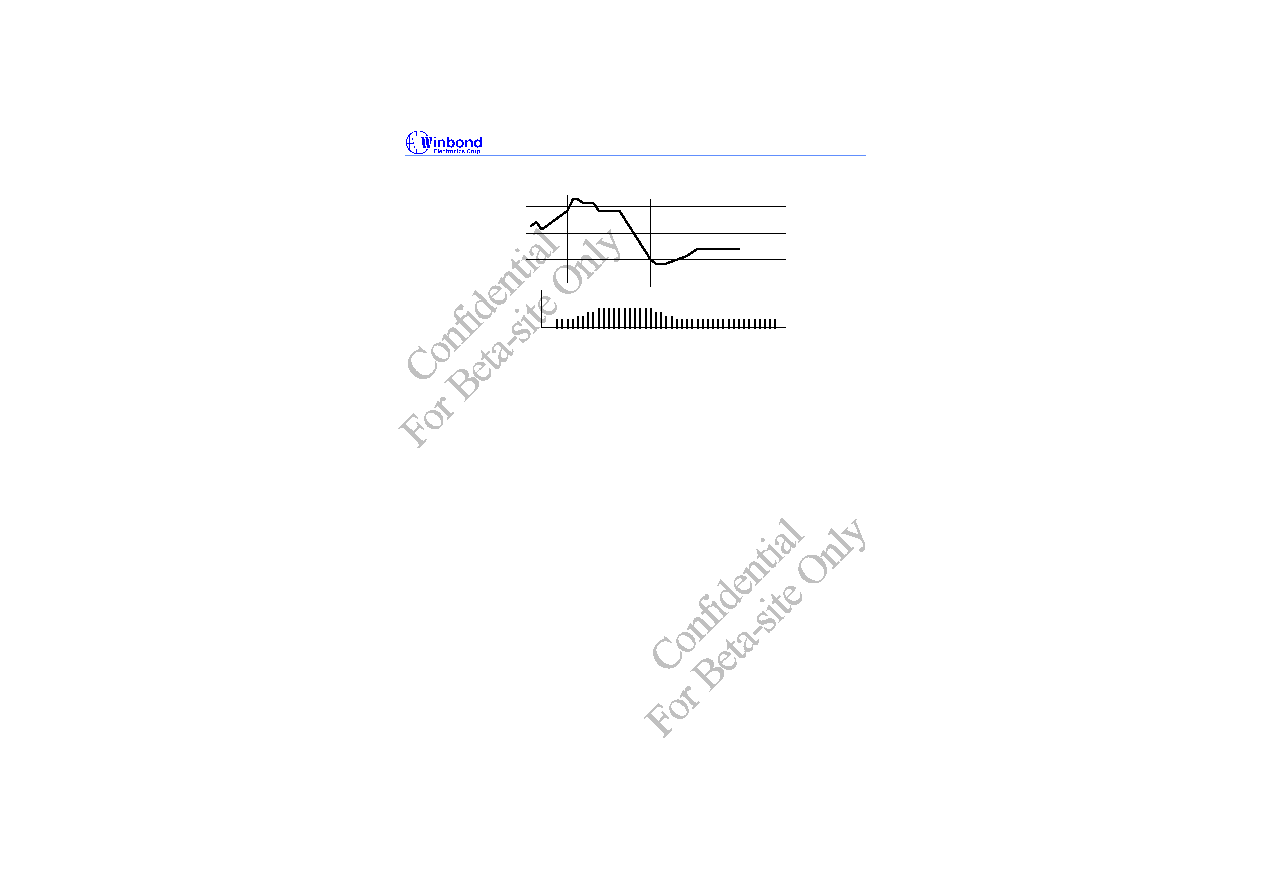

6.5.3.1 Thermal Cruise mode

At this mode, W83L784R provides the Smart Fan system which can control the fan speed

automatically depend on current temperature to keep it with in a specific range. At first a wanted

temperature and interval must be set (ex. 55

�

C

�

3

�

C) by BIOS, as long as the real temperature

remains below the setting value, the fan will be off. Once the temperature exceeds the setting high

limit temperature ( 58

�

C), the fan will be turned on with a specific speed set by BIOS (ex: 80% duty

cycle) and automatically controlled its PWM duty cycle with the temperature varying. Three

conditions may occur :

(1) If the temperature still exceeds the high limit (ex: 58

�

C), PWM duty cycle will increase slowly. If

the fan has been operating in its fully speed but the temperature still exceeds the high limit(ex: 58

�

C),

a warning message or a fan_fault signal(pin5) will be issued to protect the system.

(2) If the temperature goes below the high limit (ex: 58

�

C), but above the low limit (ex: 52

�

C), the fan

speed will be fixed at the current speed because the temperature is in the target area(ex: 52

�

C ~

58

�

C).

(3) If the temperature goes below the low limit (ex: 52

�

C), PWM duty cycle will decrease slowly to 0

until the temperature exceeds the low limit.

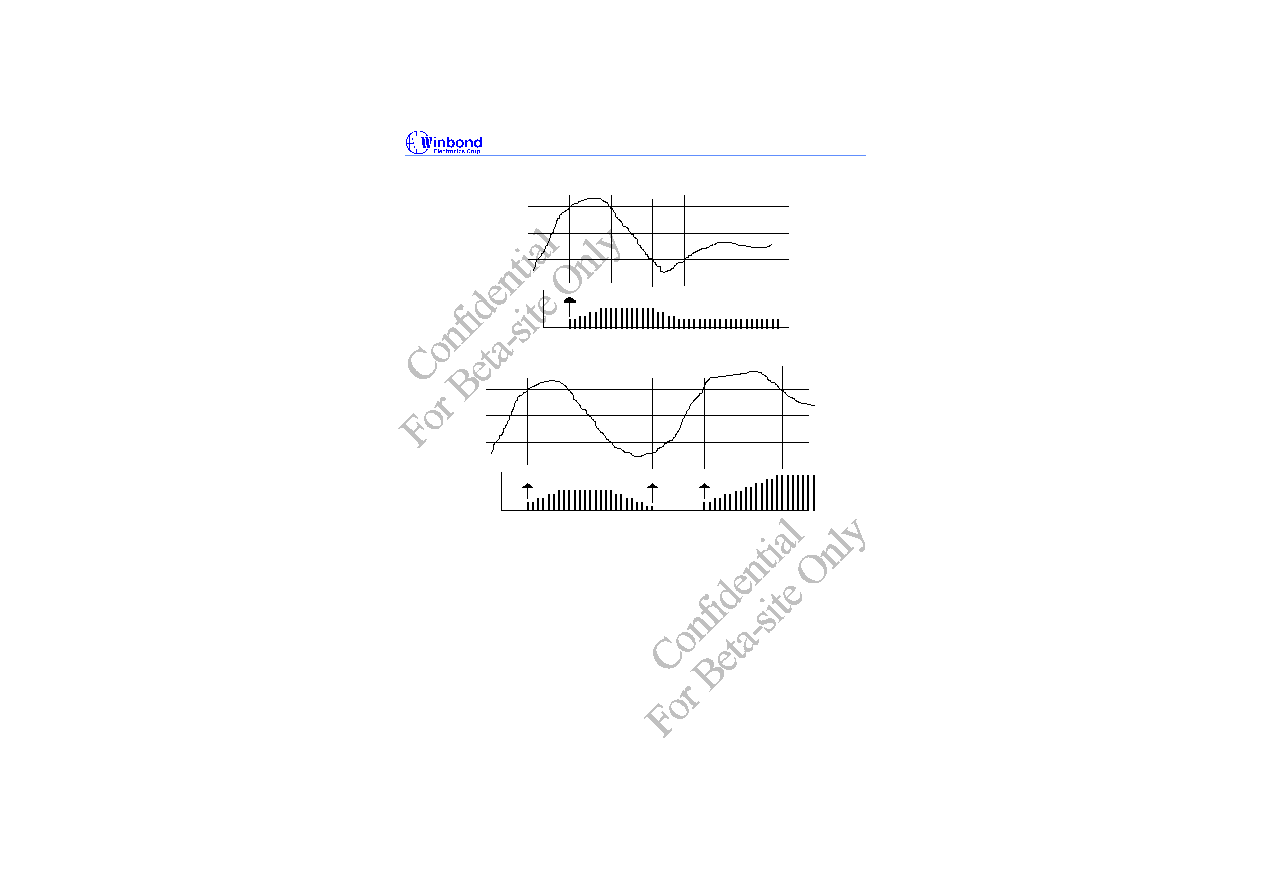

Figure 17 gives an illustration for Thermal Cruise Mode .

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-23 - Revision 0.54

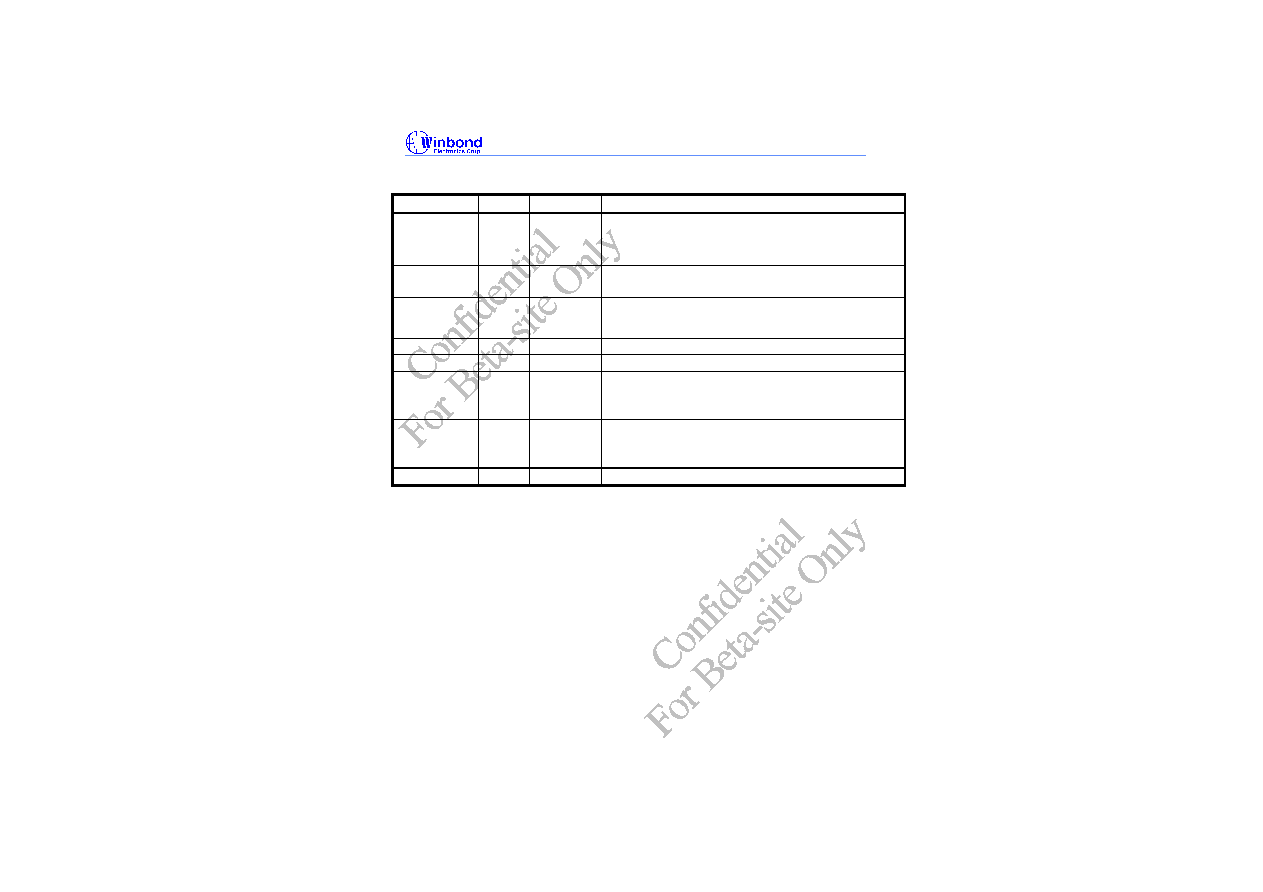

55`C

58`C

52`C

PWM

Duty

Cycle

100

0

50

Fan Start = 20%

A

B

C

D

Figure 17-1.

55`C

58`C

52`C

PWM

Duty

Cycle

100

0

50

Fan Start = 20%

Fan Stop = 10%

Fan Start = 20%

A

B

C

D

Figure 17-2.

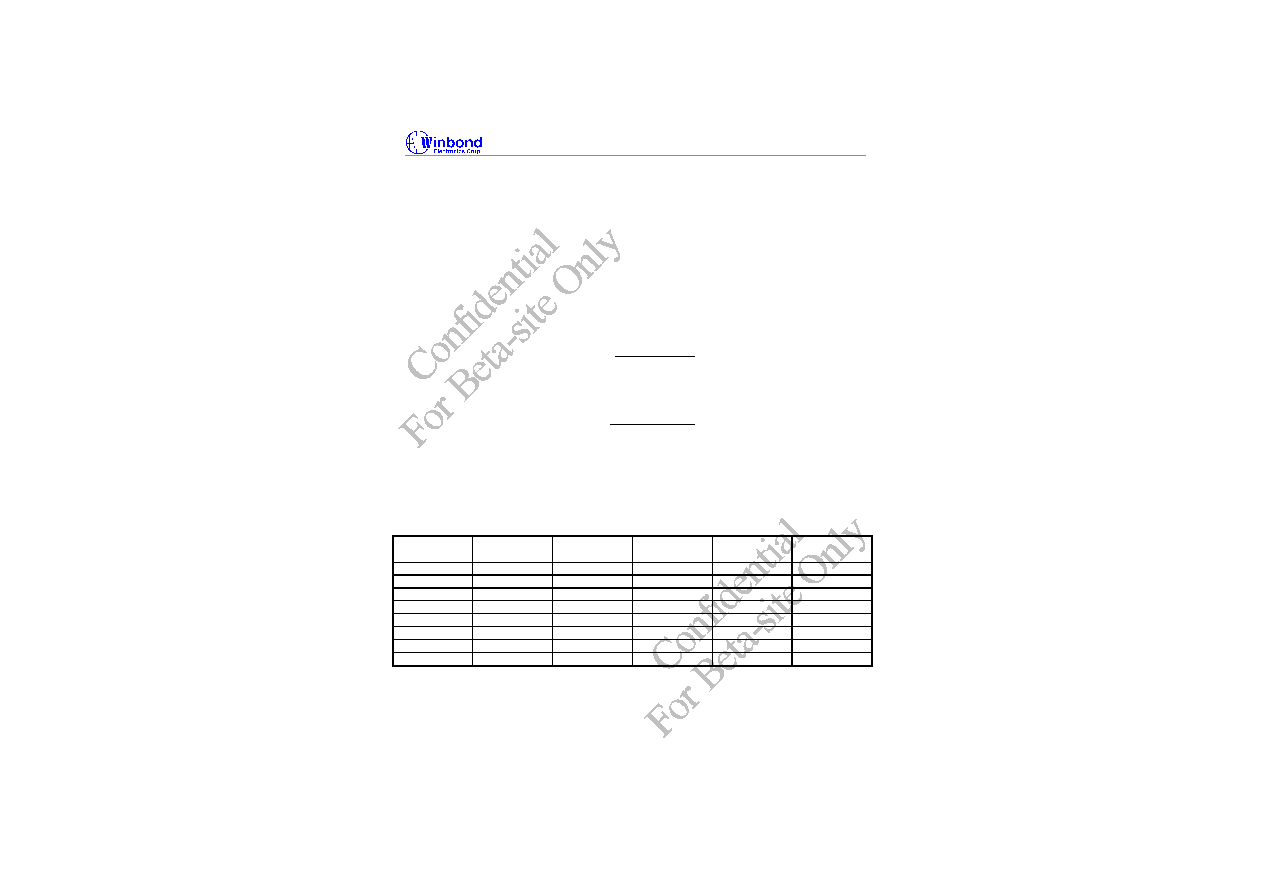

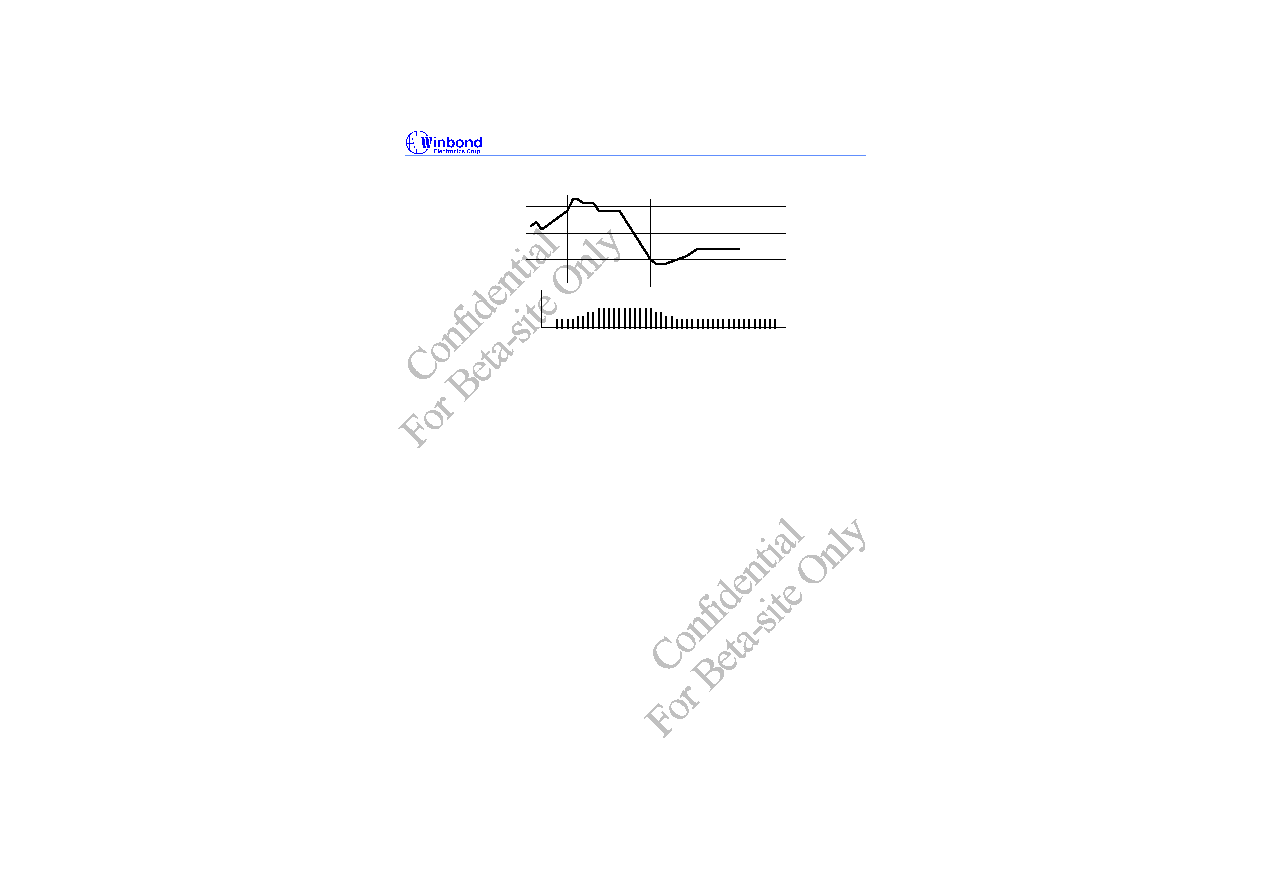

6.5.3.2 Fan Speed Cruise mode

At this mode, W83L784R provides the Smart Fan system which can control the fan speed

automatically depend on current fan spesed to keep it with in a specific range. A wanted fan speed

count and interval must be set (ex. 160

�

10 ) by BIOS. As long as the fan speed count is the specific

range, PWM duty will keep the current value. If current fan speed count is higher than the high limit

(ex. 160+10), PWM duty will be increased to keep the count less than the high limit. Otherwise, if

current fan speed is less than the low limit(ex. 160-10), PWM duty will be decreased to keep the

count higher than the low limit. See Figure 18 example.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-24 - Revision 0.54

160

170

150

PWM

Duty

Cycle

100

0

50

A

C

Count

Figure 18.

Of cource, Smart Fan control system can be disabled and the fan speed control algorithem can be

progrmmed by BIOS or application software.

6.5.4 Fan Fault Alarm

W83L784R can monitor fan speed by detecting fan speed counter value. When fan speed

count is higher than high limit count value(CR58h) or is less than low limit count value(CR59h), pin

FANFAULT# is asserted.

6.6 SMI#

6.6.1 Temperature

Pin SMI# for temperature has 3 modes.

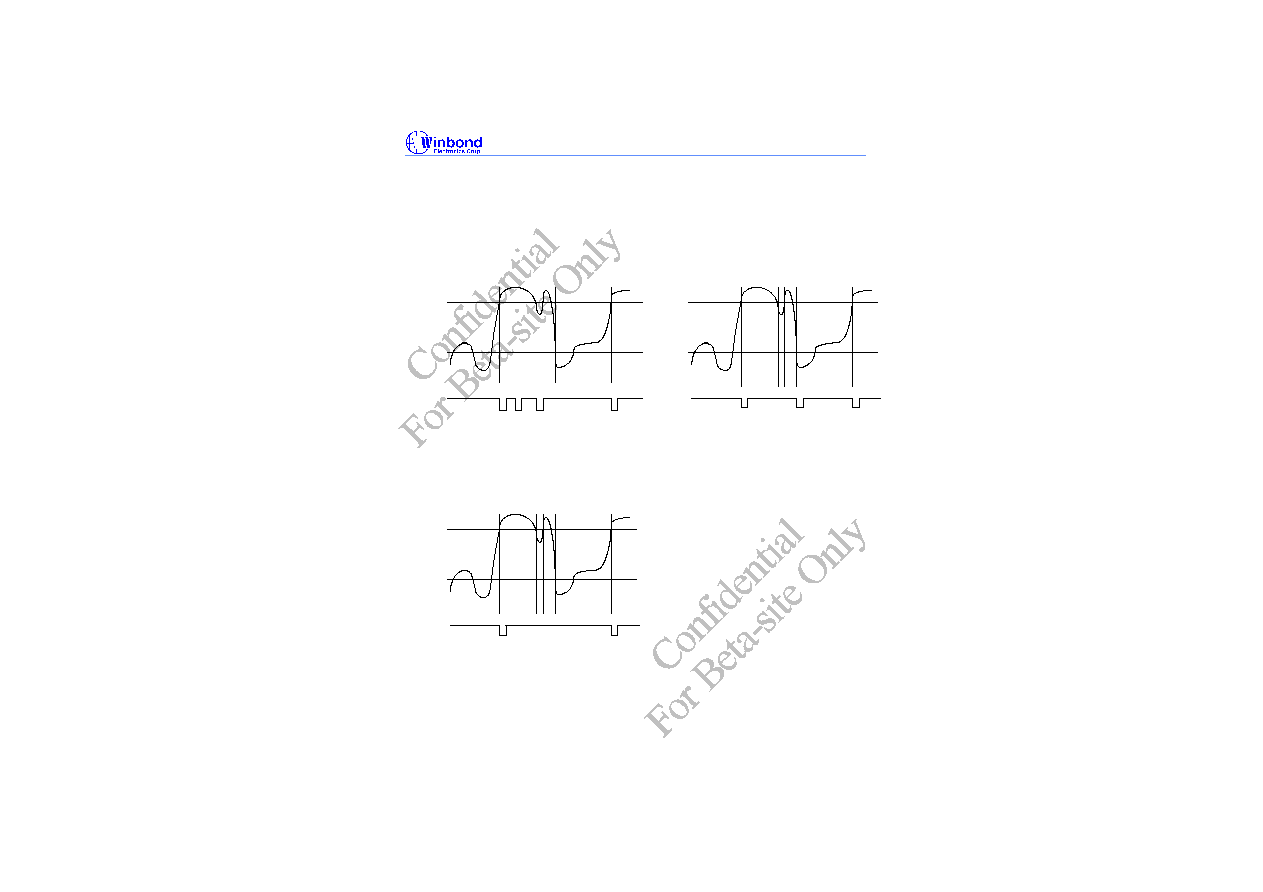

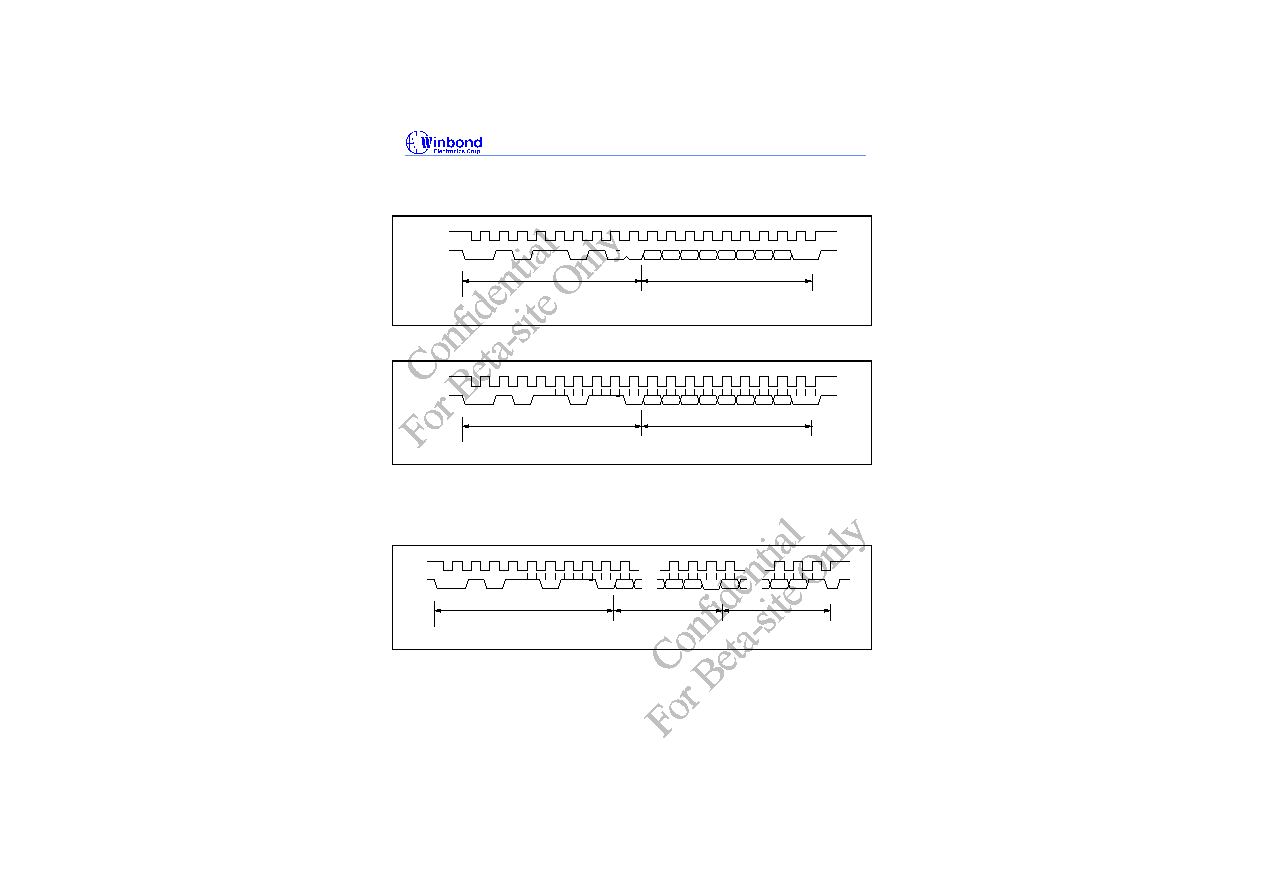

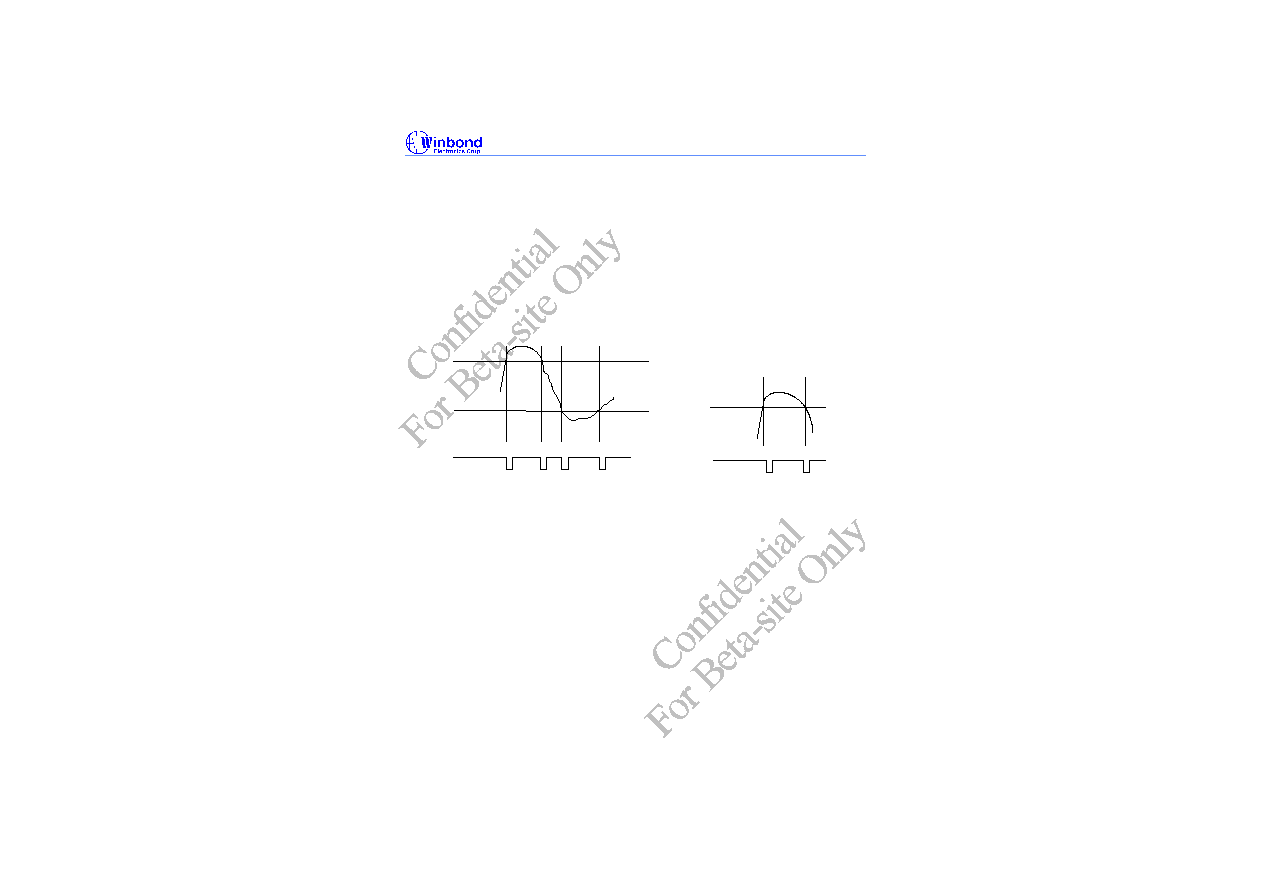

6.6.1.1 Comparator Interrupt Mode

Temperature exceeding T

O

causes an interrupt and this interrupt will be reset by reading all the

Interrupt Status Registers. Once an interrupt event has occurred by exceeding T

O

, then reset, if

the temperature remains above the T

HYST

, the interrupt will occur again when the next conversion

has completed. If an interrupt event has occurred by exceeding T

O

and not reset, the interrupts

will not occur again. The interrupts will continue to occur in this manner until the temperature

goes below T

HYST

. ( Figure 19-1 )

6.6.1.2 Two-Times Interrupt Mode

Temperature exceeding T

O

causes an interrupt and then temperature going below T

HYST

will also

cause an interrupt if the previous interrupt has been reset by reading all the interrupt Status

Register. Once an interrupt event has occurred by exceeding T

O

, then reset, if the temperature

remains above the T

HYST

, the interrupt will not occur. (Figure 19-2 )

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-25 - Revision 0.54

6.6.1.3 One-Time Interrupt Mode

Temperature exceeding T

O

causes an interrupt and then temperature going below T

HYST

will not

cause an interrupt. Once an interrupt event has occurred by exceeding T

O

, then going below

T

HYST,

an interrupt will not occur again until the temperature exceeding T

O

. (Figure 19-3 )

T

OI

T

HYST

*

*

*

Figure 19-1. Comparator Interrupt Mode

*Interrupt Reset when Interrupt Status Registers are read

T

OI

T

HYST

Figure 19-2. Two-Times Interrupt Mode

SMI#

SMI#

*

*

*

*

*

*Interrupt Reset when Interrupt Status Registers are read

T

OI

T

HYST

Figure 19-3. One-Time Interrupt Mode

SMI#

*

*

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-26 - Revision 0.54

6.6.2 Voltage

SMI# interrupt for voltage is Two-Times Interrupt Mode. Voltage exceeding high limit or going

below low limit will causes an interrupt if the previous interrupt has been reset by reading all the

interrupt Status Register. (Figure 20-1 )

6.6.3 Fan

SMI# interrupt for fan is Two-Times Interrupt Mode. Fan count exceeding the limit, or exceeding

and then going below the limit( set at value ram index 3Bh and 3Ch) , will causes an interrupt if

the previous interrupt has been reset by reading all the interrupt Status Register. (Figure 20-2 )

*

*

*

Figure 20-1. Voltage SMI# Mode

*Interrupt Reset when Interrupt Status Registers are read

Figure 20-2. Fan SMI# Mode

SMI#

*

High limit

Low limit

*

SMI#

*

Fan Count limit

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-27 - Revision 0.54

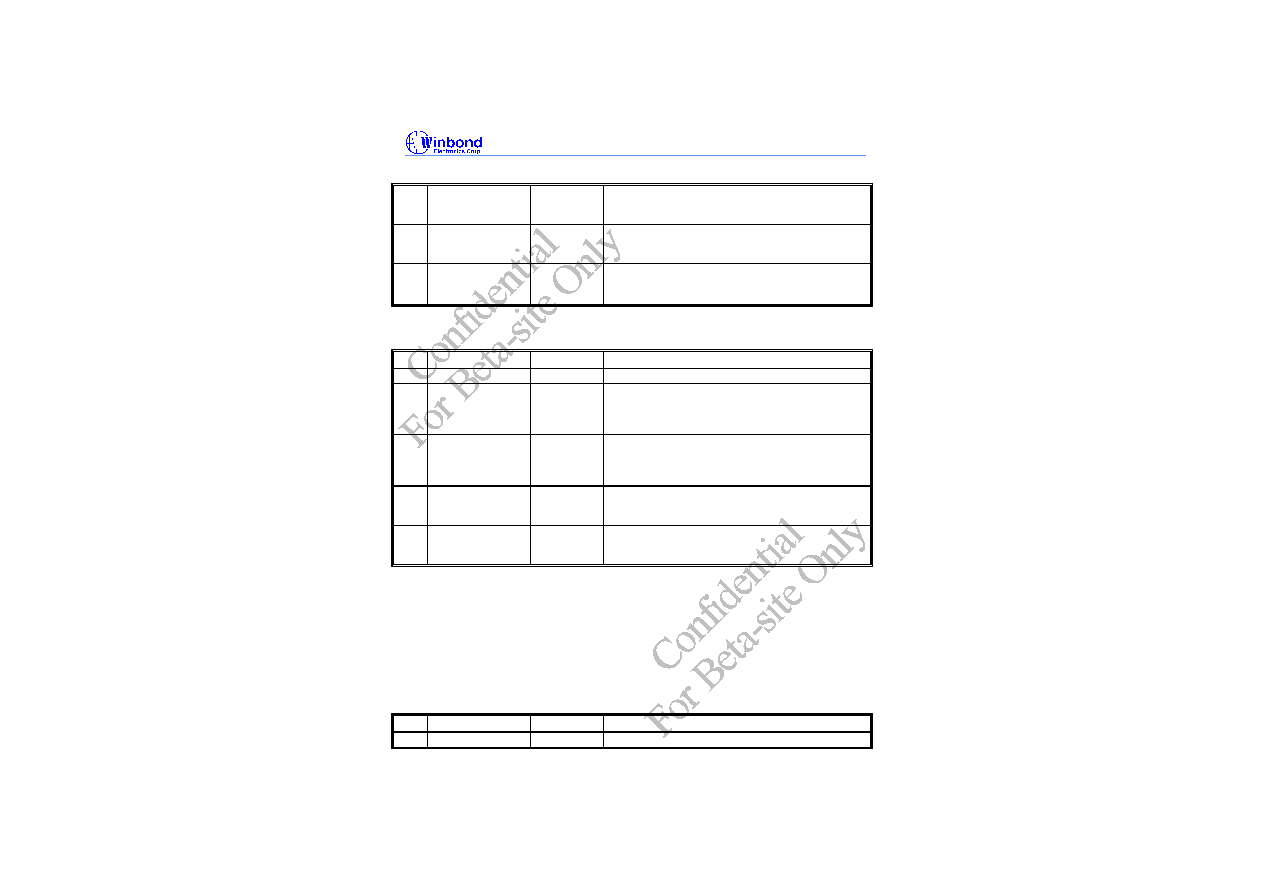

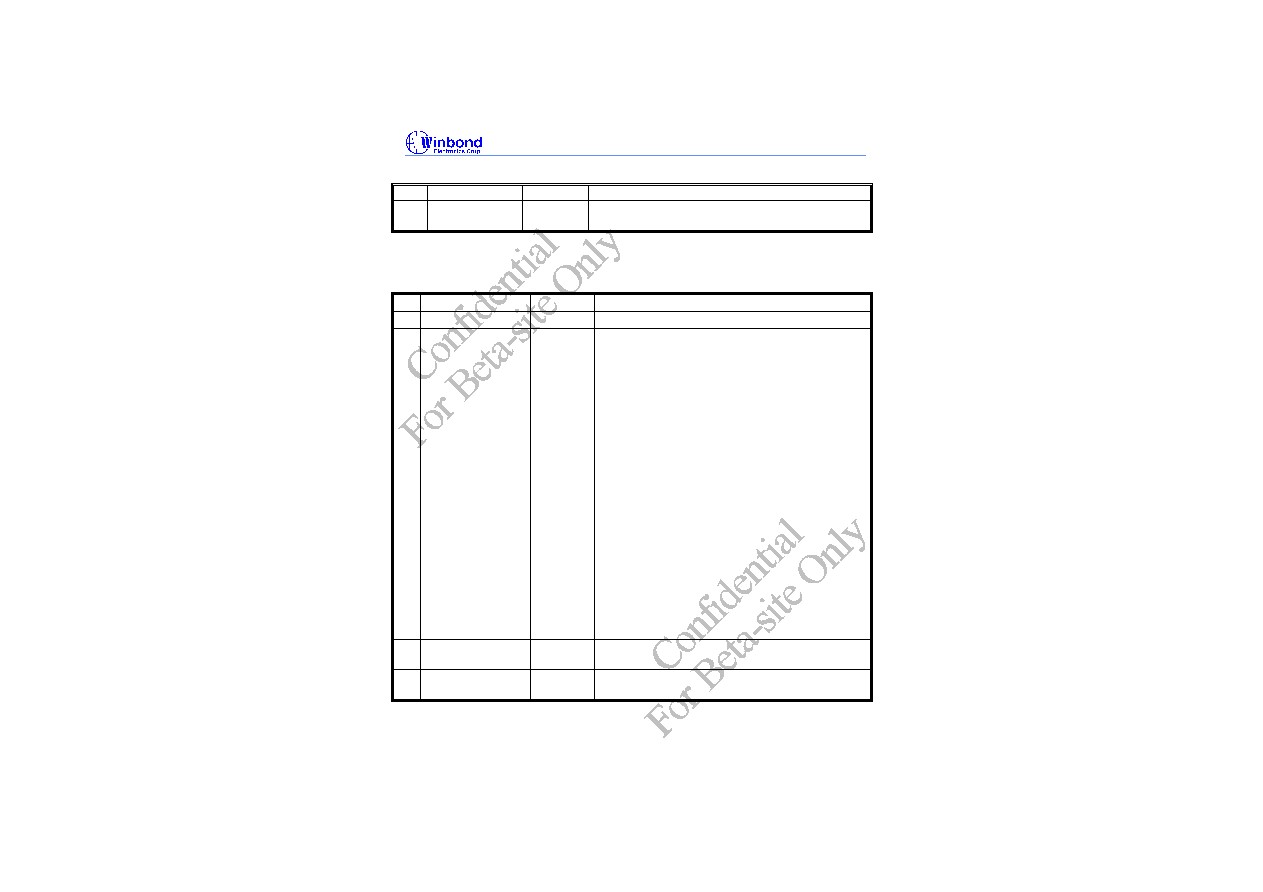

7. REGISTERS AND RAM

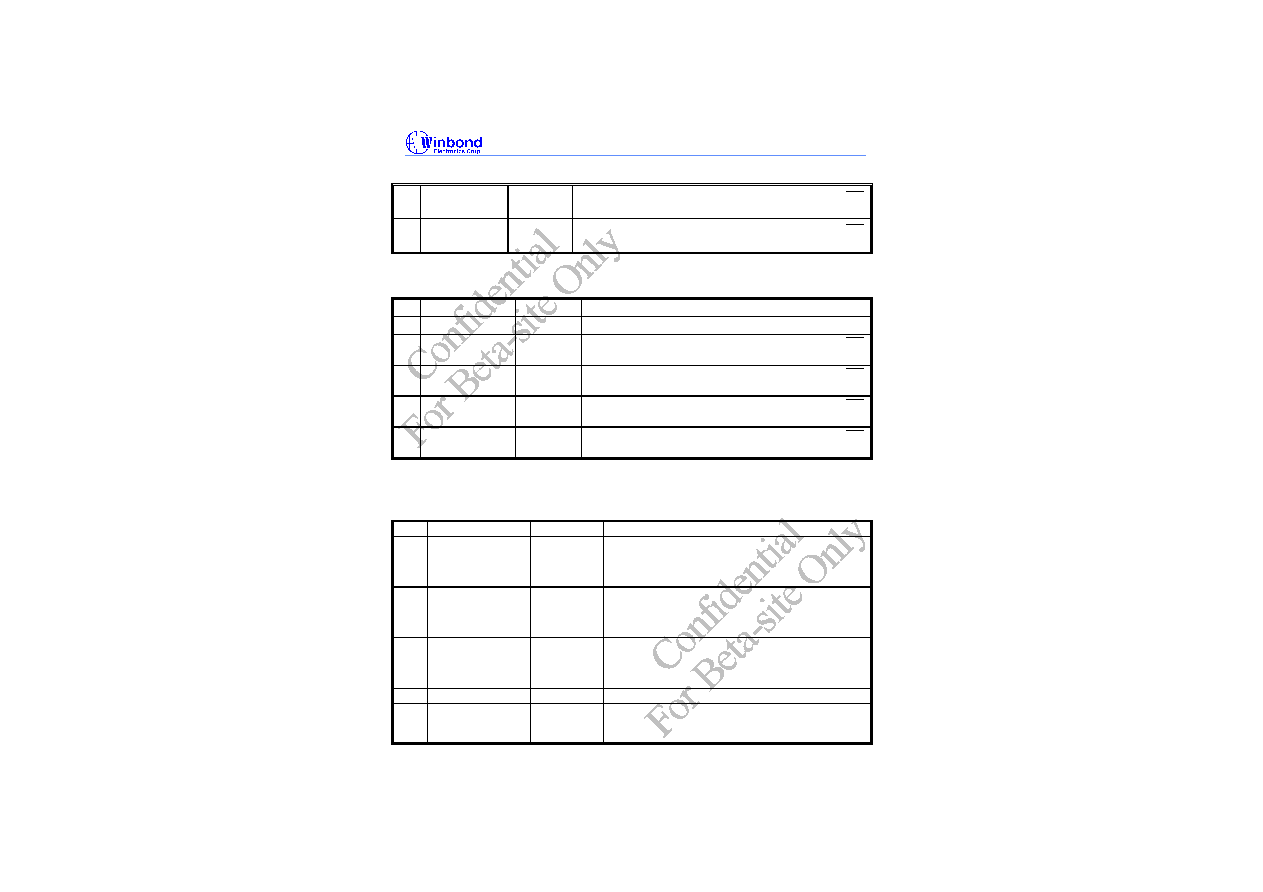

7.1 Configuration Register

�

Index 40h

Power on default [7:0] = 0000,0001 b

Bit

Name

Read/Write

Description

7

INITIALIZATION

Read/Write A one restores power on default value to all registers

except the Serial Bus Address register. This bit clears

itself since the power on default is zero.

6-4

Reserved

Read/Write Reserved

3

DIS_PWROK

Read/Write

Disable Power OK Function. If this bit set to 1, the

PWR_DN# (Pin 6) will keep logical high no mater what

the pwoer VDD or +3.3V drop to the threshold voltage

(4.0v and 2.6v, respectively).

2

Reserved

Reserved

Reserved

1

INT_ Clear

Read/Write A one disables the SMI# and IRQ# outputs without

affecting the contents of Interrupt Status Registers. The

device will stop monitoring. It will resume upon clearing

of this bit.

0

Start

Read/Write A one enables startup of monitoring operations, a zero

puts the part in standby mode.

Note: The outputs of Interrupt pins will not be cleared if

the user writes a zero to this location after an interrupt

has occurred unlike "INT_Clear'' bit.

7.2 Interrupt Status Register 1

�

Index 41h

Power on default [7:0] = 0000,0000 b

Bit

Name

Read/Write

Description

7

TEMP3

Read Only

A one indicates a High or Low limit has been exceeded from

CPUT2 sensor.

6

TEMP2

Read Only

A one indicates a High or Low limit has been exceeded from

CPUT1 sensor.

5

TEMP1

Read Only

A one indicates a High or Low limit has been exceeded from

W83L784R internal temperature sensor.

4

Reserved

Reserved

Reserved

3

VCCIN

Read Only

A one indicates a High or Low limit has been exceeded. (

VCC, +5V)

2

3VIN

Read Only

A one indicates a High or Low limit has been exceeded.

(VIN2)

1

VBATIN

Read Only

A one indicates a High or Low limit has been exceeded.(VIN3

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-28 - Revision 0.54

)

0

VCOIN

Read Only

A one indicates a High or Low limit has been exceeded.

(VIN1)

7.3 Interrupt Status Register 2

�

Index 42h

Power on default [7:0] = 0000,0000 b

Bit

Name

Read/Write

Description

7-4

Reserved

Read Only

Read 0.

3

TAR_T2

Read Only

CPUT2 Target Status. A one indicate CPUT2 temperature

with Fan 2 full speed can not be in the specific range after 3

minutes.

2

TAR_T1

Read Only

CPUT1 Target Status. A one indicate CPUT1 temperature

with Fan 1 full speed can not be in the specific range after 3

minutes.

1

FAN2

Read Only

A one indicates the fan count limit has been exceeded.

0

FAN1

Read Only

A one indicates the fan count limit has been exceeded.

7.4 SMI Mask Register 1

�

Index 43h

Power on default <7:0> = 0000,0000 b

Bit

Name

Read/Write

Description

7

MSK_T3_SMI

Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt.(CPUT2 target temperature)

6

MSK_T2_SMI

Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt.(CPUT1 target temperature)

5

MSK_T1_SMI

Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt. (internal thermal diode)

4

Reserved

Reserved

Reserved

3

MSK_VCC_SMI Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt. (VCC, +5V)

2

MSK_3V_SMI

Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt. (Pin VIN2)

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-29 - Revision 0.54

1

MSK_VBAT_S

MI

Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt.(Pin VIN3)

0

MSK_VCO_SMI Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt. (Pin VIN1)

7.5 SMI� Mask Register 2

�

Index 44h

Power on default [7:0] = 0000,0000 b

Bit

Name

Read/Write

Description

7-4

Reserved

Read/Write

Reserved.

3

MSK_TAR2_SMI

Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt. (CPUT2 target temperature )

2

MSK_TAR1_SMI

Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt. (CPUT1 target temperature )

1

MSK_FAN2_SMI

Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt. (Fan 2 speed counter)

0

MSK_FAN1_SMI

Read/Write A one disables the corresponding interrupt status bit for

SMI

interrupt. (Fan 1 speed counter)

7.6 Real Time Hardware Status Register I -- Index 45h

Power on - [7:0] = 0000,0000 b

Bit

Name

Read/Write

Description

7

TEMP3_STS

Read Only

Temperature sensor 3 (CPU T2) Status. Set 1, the

voltage of temperature sensor is over the limit value.

Set 0, the voltage of temperature sensor is in the limit

range.

6

TEMP2_STS

Read Only

Temperature sensor 2 (CPU T1) Status. Set 1, the

voltage of temperature sensor is over the limit value.

Set 0, the voltage of temperature sensor is in the limit

range.

5

TEMP1_STS

Read Only

Temperature sensor 1 (Internal Thermal Diode) Status.

Set 1, the voltage of temperature sensor is over the

limit value. Set 0, the voltage of temperature sensor is

in the limit range.

4

Reserved

Reserved

Reserved.

3

VCCIN_STS

Read Only

+5V Voltage Status. Set 1, the voltage of +5V is over

the limit value. Set 0, the voltage of +5V is in the limit

range.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-30 - Revision 0.54

2

3V_STS

Read Only

+3.3V Voltage Status. Set 1, the voltage of +3.3V is

over the limit value. Set 0, the voltage of +3.3V is in the

limit range.

1

VBAT_STS

Read Only

VBAT (VIN3) Voltage Status. Set 1, the voltage of

VBAT(VIN3) is over the limit value. Set 0, the voltage

of VBAT(VIN3) is in the limit range.

0

VCO_STS

Read Only

VCORE A Voltage Status. Set 1, the voltage of VCORE

A is over the limit value. Set 0, the voltage of VCORE

A is in the limit range.

7.7 Real Time Hardware Status Register II -- Index 46h

Power on default [7:0] = 0000-0000 b

Bit

Name

Read/Write

Description

7-4

Reserved

Read Only

Read 0.

3

TART2_STS

Read Only

CPUT2 Target Status. Set 1, when CPUT2 target

temperature with Fan 2 full speed can not be in the

range after 3 minutes. Set 0, the temperature or speed

is in the specific range .

2

TART1_STS

Read Only

CPUT1 Targert Status. Set 1, when CPUT1 target

temperature with Fan 1 full speed can not be in the

range after 3 minutes. Set 0, the temperature or speed

is in the specific range ..

1

FAN2_STS

Read Only

FAN 2 Status. Set 1, the fan speed counter is over the

limit value. Set 0, the fan speed counter is in the limit

range.

0

FAN1_STS

Read Only

FAN 1 Status. Set 1, the fan speed counter is over the

limit value. Set 0, the fan speed counter is in the limit

range.

7.8 Reserved Register -- Index 47h

Reserved.

7.9 Reserved Register -- Index 48h

Reserved.

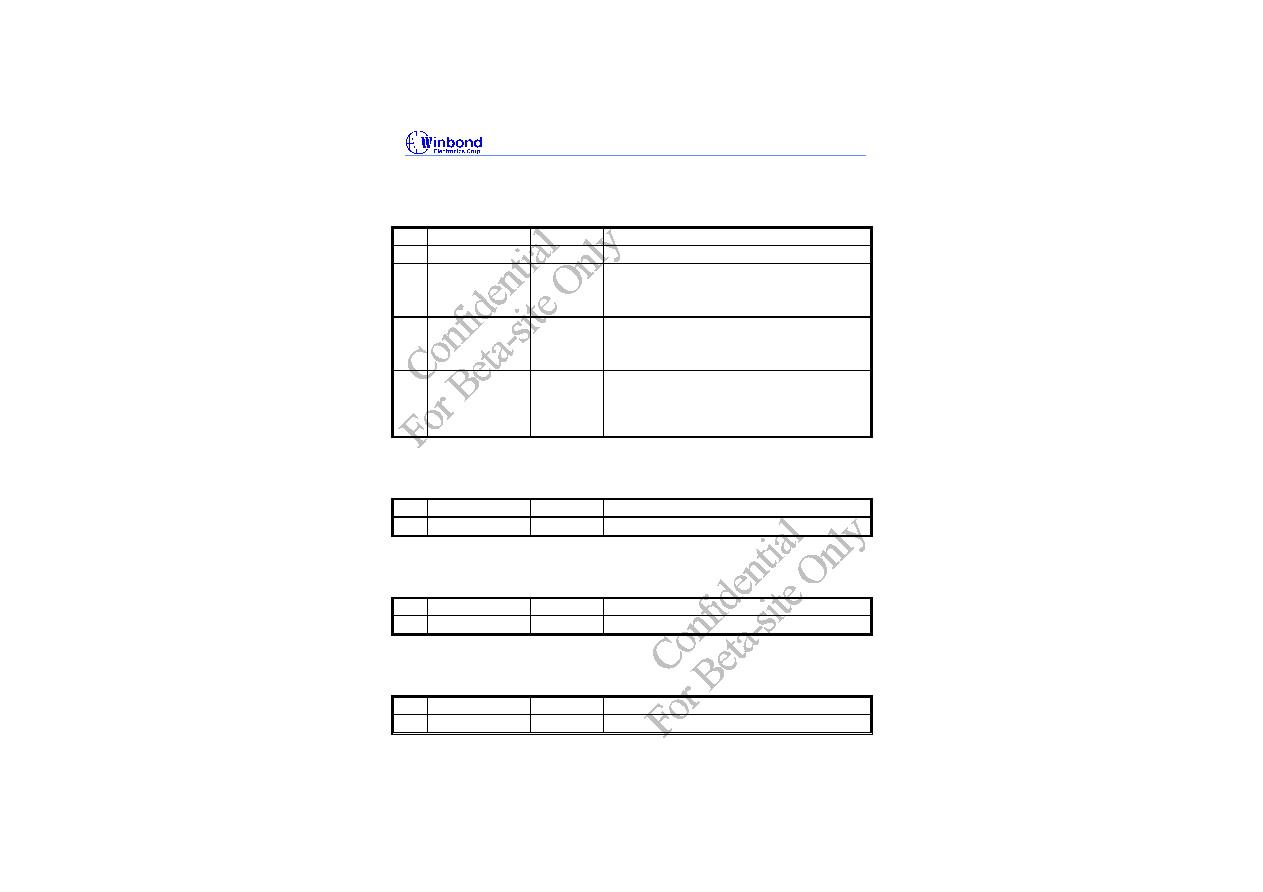

7.10 Fan Divisor Register

�

Index 49h

Power on default [7:4] = 0001,0001 b

Bit

Name

Read/Write

Description

7

Reserved

Read/write

Reserved.

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-31 - Revision 0.54

6-4

F2_SP_CRTL[2:0]

Read/Write

FAN2 Speed Control.

000 - divide by 1;

001 - divide by 2;

010 - divide by 4;

011 - divide by 8.

100 - divide by 16.

101 - divide by 32.

110 - divide by 64.

111 - divide by 128.

3

Reserved

Read/write

Reserved.

2-0

F1_SP_CTRL[2:0]

Read/Write

FAN1 Speed Control.

000 - divide by 1;

001 - divide by 2;

010 - divide by 4;

011 - divide by 8.

100 - divide by 16.

101 - divide by 32.

110 - divide by 64.

111 - divide by 128.

7.11 Serial Bus Address (for Voltage ,Fan, and internal temperature ) Register

�

Address 4Ah

Power on default [7:0] = 0010,1101 b

Bit

Name

Read/Write

Description

7

Reserved

Read Only

6-0

Serial Bus Address

Read/Write

Serial Bus address [6:0].

7.12 CPUT1 Temperature and CPUT2 Temperature Serial Bus Address Register--

Index 4Bh

Power on default [7:0] = 0000,0001 b

Bit

Name

Read/Write

Description

7

DIS_CPUT2

Read/Write

Disable CPUT2 Temperature Function. Set to 1,

disable temperature 3 sensor and can not access any

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-32 - Revision 0.54

data from Temperature Sensor 3. Note that the relative

functions of Status, and SMI# will be disable.

6-4

I2CADDR3[2:0]

Read/Write

Temperature 3 Seiral Bus Address. The serial bus

address is 1001xxx. Where xxx are defined in these

bits.

3

DIS_CPUT1

Read/write

Disable CPUT1 Temperature Function. Set to 1,

disable temperature Sensor and can not access any

data from Temperature Sensor 2. Note that the relative

functions of Status, and SMI# will be disable.

2-0

I2CADDR2[2:0]

Read/Write

Temperature 2 Serial Bus Address. The serial bus

address is 1001xxx. Where xxx are defined in these

bits.

7.13 Winbond Vendor ID (Low Byte) - Index 4Ch (Auto Increase)

Power-on default [7:0] = 1010,0011 b (A3h)

Bit

Name

Read/Write

Description

7:0

VIDL[7:0]

Read Only

Vendor ID Low Byte. Default A3h.

7.14 Winbond Vendor ID (High Byte) - Index 4Dh (No Auto Increase)

Power-on default [7:0] = 0101,1100 b (5Ch)

Bit

Name

Read/Write

Description

7:0

VIDH[7:0]

Read Only

Vendor ID High Byte. Default 5Ch

7.15 Chip ID -- Index 4Eh

Power on default [7:0] = 0101,0000 b

Bit

Name

Read/Write

Description

7-0

CHIPID[7:0]

Read Only

Winbond Chip ID number. Read this register will

return 50h for W83L784R.

7.16 ACPI Temperature Increment Register -- Index 4Fh

Power on deafult [7:0] = 0000,0101 b

Bit

Name

Read/Write

Description

7

Reserved

Read/Write

Reserved.

6-0

DIFFREG[6:0]

ReadWrite

ACPI Temperature Increment Register. If set to this

register to non-zero value, the OVT# signal will be

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-33 - Revision 0.54

register to non-zero value, the OVT# signal will be

actived at pointer of the temperaure of times of

DIFFREG (i.e. DIFFREG*n, where n is non-zero

integer). The default value is 5 degree C.

7.17 OVT# Property Select - Index 50h

Power on default [7:0] = 0000,0000 b

Bit

Name

Read/Write

Description

7-6

Reserved

Read/Write Reserved.

5-4

OVT_MD[1:0]

Read/Write

OVT# Mode Select. There are three OVT# signal output

type.

<00> -

Comparator Mode: (Default)

Temperature exceeding T

O

causes the OVT# output

activated until the temperature is less than T

HYST

.

<01> -

Interrupt Mode:

Setting temperature exceeding T

O

causes the OVT#

output activated indefinitely until reset reading temperature

sensor 1/2/3 registers. Temperature exceeding T

O

, then

OVT# reset, and then temperature going below T

HYST

will

also cause the OVT# activated indifinitely until reset by

reading temperature sensor 1/2/3. Onece the OVT# will not

be activated by exceeding T

O

, then reset, if the

temperature remains above T

HYST

, the OVT# will not be

actived agian.

<10> -

ACPI Mode:

If set to 1 then enable ACPI OVT# output. Which is

always send an OVT# signal when the temperature over

the ACPI temperature increment value defined at Index

4Fh.

3

EN_OVT3

Read/Write Enable CPUT2 temperature sensor over-temperature

(OVT) output if set to 1. Default 0, disable CPUT2 OVT

output through pin OVT#. The pin OVT# is wire OR with

OVT1 and OVT2.

2

EN_OVT2

Read/Write Enable CPUT1 temperature sensor over-temperature

(OVT) output if set to 1. Default 0, disable CPUT1 OVT

output through pin OVT#. The pin OVT# is wire OR with

OVT1 and OVT3.

1

EN_OVT1

Read/Write Enable internal temperature sensor over-temperature

(OVT) output if set to 1. Default 0, disable OVT1 output

through pin OVT#. The pin OVT# is wire OR with OVT2

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-34 - Revision 0.54

and OVT3.

0

OVTPOL

Read/Write

Over-Temperature Polarity. Write 1, OVT# active high.

Write 0, OVT# active low. Default 0.

7.18 SMI# Property Select -- Index 51h

Power on - <7:0> --0000,0100 b

Bit

Name

Read/Write

Description

7-4 Reserved

Read/Write Reserved.

3-2 TEMP_SMI_MD[1:0] Read/Write

Temperature SMI Mode Select.

<00> -

Comparator Interrupt Mode:

Temperature 1/2/3 exceeds T

O

(Over-temperature)

limit causes and interrupt and this interrupt will be reset

by reading all the Interrupt Stauts.

<01> -

Two Time Interrupt Mode:(Default)

This bit use in temperature sensor 1/2/3 interrupt

mode with hysteresis type. Temperature exceeding T

O

,

causes an interrupt and then temperature going below

T

HYST

will also cause an interrupt if the previous interrupt

has been reset by reading all the interrupt Status

Register. Once an interrupt event has occurred by

exceeding T

O

, then reset, if the temperature remains

above the T

HYST

.

<10>

- One Time Interrupt Mode:

This bit use in temperature sensor 1/2/3 interrupt

mode with hysteresis type. Temperature exceeding T

O

(Over-temperature, defined in Bank 1/2) causes an

interrupt and then temperature going below T

HYST

(Hysteresis temperature, defined in Bank 1/2) will not

cause an interrupt. Once an interrupt event has occurred

by exceeding T

O

, then going below T

HYST

, and interrupt

will not occur again until the temperature exceeding T

O

.

1

EN_SMI#

Read/Write

Enable SMI# Output. A one enables the SMI# Interrupt

output.

0

SMIPOL

Read/Write

SMI# Polarity. Write 1, SMI# active high. Write 0, SMI#

active low. Default 0.

7.19 FANIN1/GPO1, FANIN2/GPO2 and BEEP/GPO3 Control Register- Indxe 52h

W83L784R

Preliminary

Confidential, For Beta-site Only Publication Release Date: Sep.

1999

-35 - Revision 0.54

Power on default [7:0] = 0000,0000 b

Bit

Name

Read/Write

Description

7

GPO4_VAL