| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 24AA160-P | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

©

1996 Microchip Technology Inc.

Preliminary

DS21146D-page 1

FEATURES

∑ 3 MHz Clock Rate

∑ SPI Modes 0,0 and 1,1.

∑ Single supply with programming operation down

to 1.8V

∑ Low Power CMOS Technology

- Max Write Current: 5 mA

- Read Current: 1.0 mA

- Standby Current: 1

µ

A typical

∑ Organization

- 1024 x 8 for 25AA080

- 2048 x 8 for 25AA160

∑ 16 Byte Page

∑ Self-timed ERASE and WRITE Cycles

∑ Sequential Read

∑ Block Write Protection

- Protect none, 1/4, 1/2, or all of Array

∑ Built-in Write Protection

- Power On/Off Data Protection Circuitry

- Write Latch

- Write Protect Pin

∑ High Reliability

- Endurance: 10M cycles (guaranteed)

- Data Retention: >200 years

- ESD protection: >4000 V

∑ 8-pin PDIP/SOIC Packages

∑ Temperature ranges supported

DESCRIPTION

The Microchip Technology Inc. 25AA080/160 are 8K

and 16K bit Serial Electrically Erasable PROMs. The

memory is accessed via a simple Serial Peripheral

Interface (SPI) compatible serial bus. The bus signals

required are a clock input (SCK) plus separate data in

(SI) and data out (SO) lines. Access to the device is

controlled through a chip select (CS) input, allowing any

number of devices to share the same bus.

There are two other inputs that provide the end user

with additional flexibility. Communication to the device

can be paused via the hold pin (HOLD). While the

device is paused, transitions on its inputs will be

ignored, with the exception of chip select, allowing the

host to service higher priority interrupts. Also write

operations to the Status Register can be disabled via

the write protect pin (WP).

- Commercial (C):

0

∞

C to

+70

∞

C

- Industrial (I):

-40

∞

C to

+85

∞

C

PACKAGE TYPES

BLOCK DIAGRAM

25AA080/16

0

25AA080/16

0

CS

SO

WP

Vss

Vcc

HOLD

SCK

SI

1

2

3

4

8

7

6

5

CS

SO

WP

Vss

Vcc

HOLD

SCK

SI

1

2

3

4

8

7

6

5

PDIP

SOIC

SI

SO

SCK

CS

HOLD

WP

Status

Register

I/O Control

Memory

Control

Logic

X

Dec

HV Generator

EEPROM

Array

Page Latches

Y Decoder

Sense Amp.

R/W Control

Logic

Vcc

Vss

25AA080/160

8K/16K 1.8V SPI

TM

Bus Serial EEPROM

SPI is a trademark of Motorola.

This document was created with FrameMaker 4 0 4

25AA080/160

DS21146D-page 2

Preliminary

©

1996 Microchip Technology Inc.

1.0

ELECTRICAL

CHARACTERISTICS

1.1

Maximum Ratings*

V

CC

....................................................................... 7.0V

All inputs and outputs w.r.t. ......V

SS

-0.6V to V

CC

+1.0V

Storage temperature .............................-65∞C to 150∞C

Ambient temperature under bias ...........-65∞C to 125∞C

Soldering temperature of leads (10 seconds) ...+300∞C

ESD protection on all pins...................................... 4kV

*

Notice:

Stresses above those listed under `Maximum ratings'

may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at those or

any other conditions above those indicated in the operational

listings of this specification is not implied. Exposure to maxi-

mum rating conditions for extended period of time may affect

device reliability.

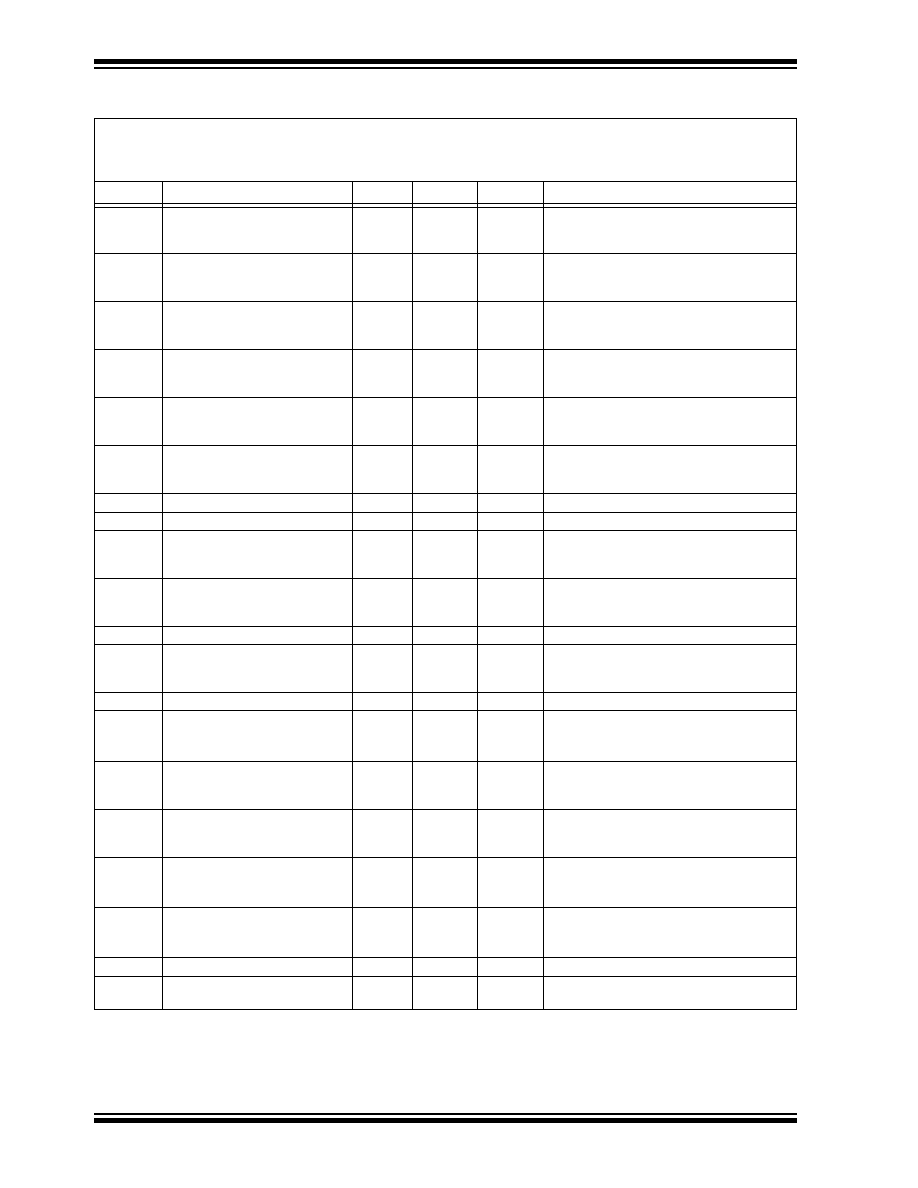

TABLE 1-1:

PIN FUNCTION TABLE

Name

Function

CS

Chip Select Input

SO

Serial Data Output

SI

Serial Data Input

SCK

Serial Clock Input

WP

Write Protect Pin

V

SS

Ground

V

CC

Supply Voltage

HOLD

Hold Input

FIGURE 1-1:

AC TEST CIRCUIT

1.2

AC Test Conditions

AC Waveform:

V

LO

= 0.2V

V

HI

= Vcc - 0.2V

(Note 1)

V

HI

= 4.0V

(Note 2)

Timing Measurement Reference Level

Input

0.5 V

CC

Output

0.5 V

CC

Note 1: For V

CC

4.0V

2: For V

CC

> 4.0V

Vcc

SO

100 pF

1.8 K

2.25 K

TABLE 1-2:

DC CHARACTERISTICS

Applicable over recommended operating ranges shown below unless otherwise noted.

V

CC

= +1.8V to 5.5V

Commercial (C): Tamb

=

0∞C to +70∞C

Industrial (I):

Tamb

=

-40

∞

C to +85

∞

C

Parameter

Symbol

Min

Max

Units

Test Conditions

High level input voltage

V

IH1

2.0

V

CC

+1

V

V

CC

2.7V

V

IH2

0.7 V

CC

V

CC

+1

V

V

CC

< 2.7V

Low level input voltage

V

IL1

-0.3

0.8

V

V

CC

2.7V

V

IL2

-0.3

0.3 V

CC

V

V

CC

< 2.7V

Low level output voltage

V

OL

--

0.4

V

I

OL

=2.1 mA

High level output voltage

V

OH

V

CC

-0.5

--

V

I

OH

=-400

µ

A

Input leakage current

I

LI

-10

10

µ

A

CS=V

IH

, V

IN

=V

SS

to V

CC

Output leakage current

I

LO

-10

10

µ

A

CS=V

IH

, V

OUT

=V

SS

to V

CC

Internal Capacitance

(all inputs and outputs)

C

INT

--

7

pF

Tamb=25∞C, F

CLK

=3.0 MHz,

V

CC

=5.5V (Note)

Operating Current

I

CC

WRITE

--

--

5

3

mA

mA

V

CC

=5.5V

V

CC

=2.5V

I

CC

READ

--

--

1

500

mA

µ

A

V

CC

=5.5V; 3 MHz

V

CC

=2.5V; 2 MHz

Standby Current

I

CCS

--

--

5

2

µ

A

µ

A

CS=V

CC

=5.5V; Vin=0V or V

CC

CS=V

CC

=2.5V; Vin=0V or V

CC

Note:

This parameter is periodically sampled and not 100% tested.

©

1996 Microchip Technology Inc.

Preliminary

DS21146D-page 3

25AA080/160

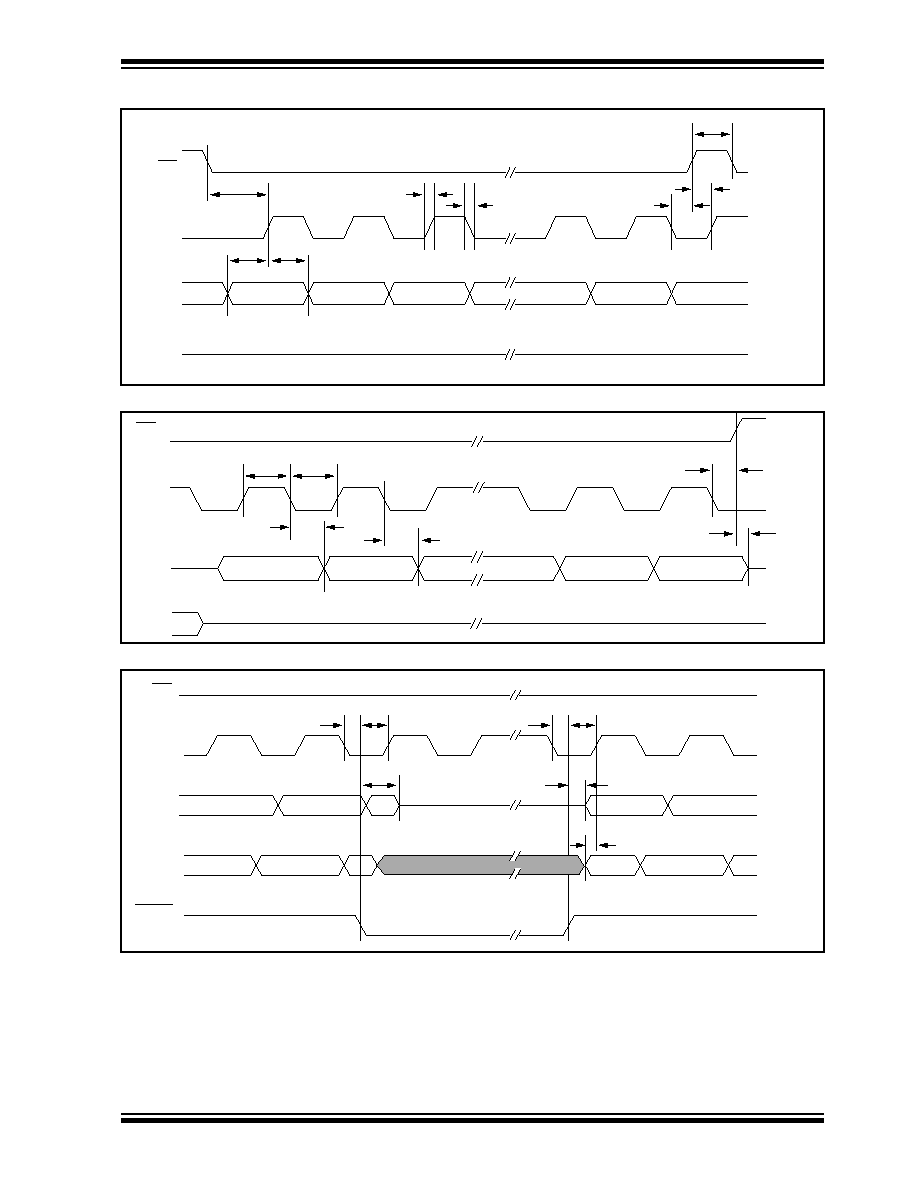

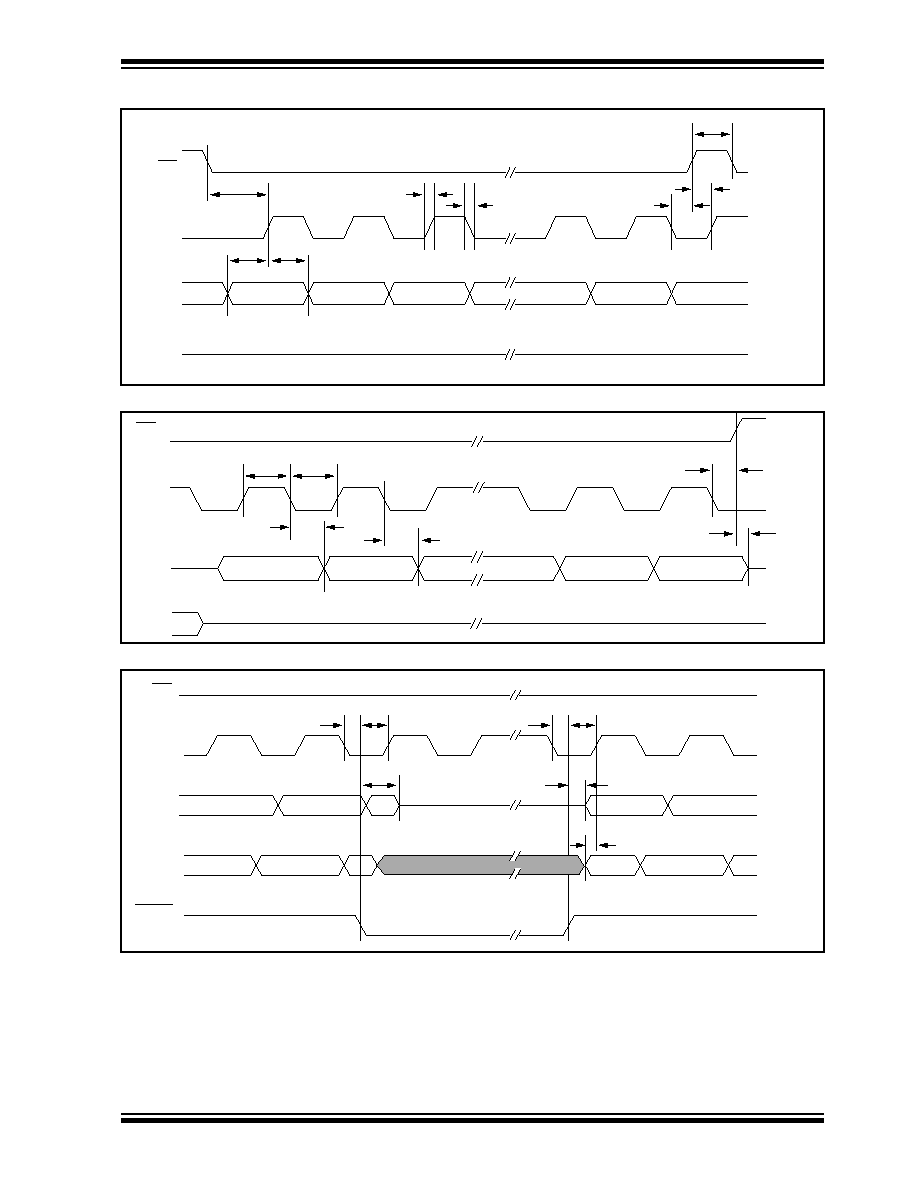

FIGURE 1-2:

SERIAL INPUT TIMING

FIGURE 1-3:

SERIAL OUTPUT TIMING

FIGURE 1-4:

HOLD TIMING

CS

SCK

SI

SO

t

CSS

t

HD

t

SU

t

F

t

R

t

CSD

t

CLD

t

CSH

LSB in

MSB in

high impedance

CS

SCK

SO

t

LO

t

HI

t

HO

t

V

MSB out

LSB out

t

CSH

t

DIS

don't care

SI

CS

SCK

SO

SI

HOLD

t

HH

t

HS

t

HS

t

HH

t

HV

t

HZ

don't care

t

SU

high impedance

n+2

n+1

n

n-1

n

n+2

n+1

n

n

n-1

25AA080/160

DS21146D-page 4

Preliminary

©

1996 Microchip Technology Inc.

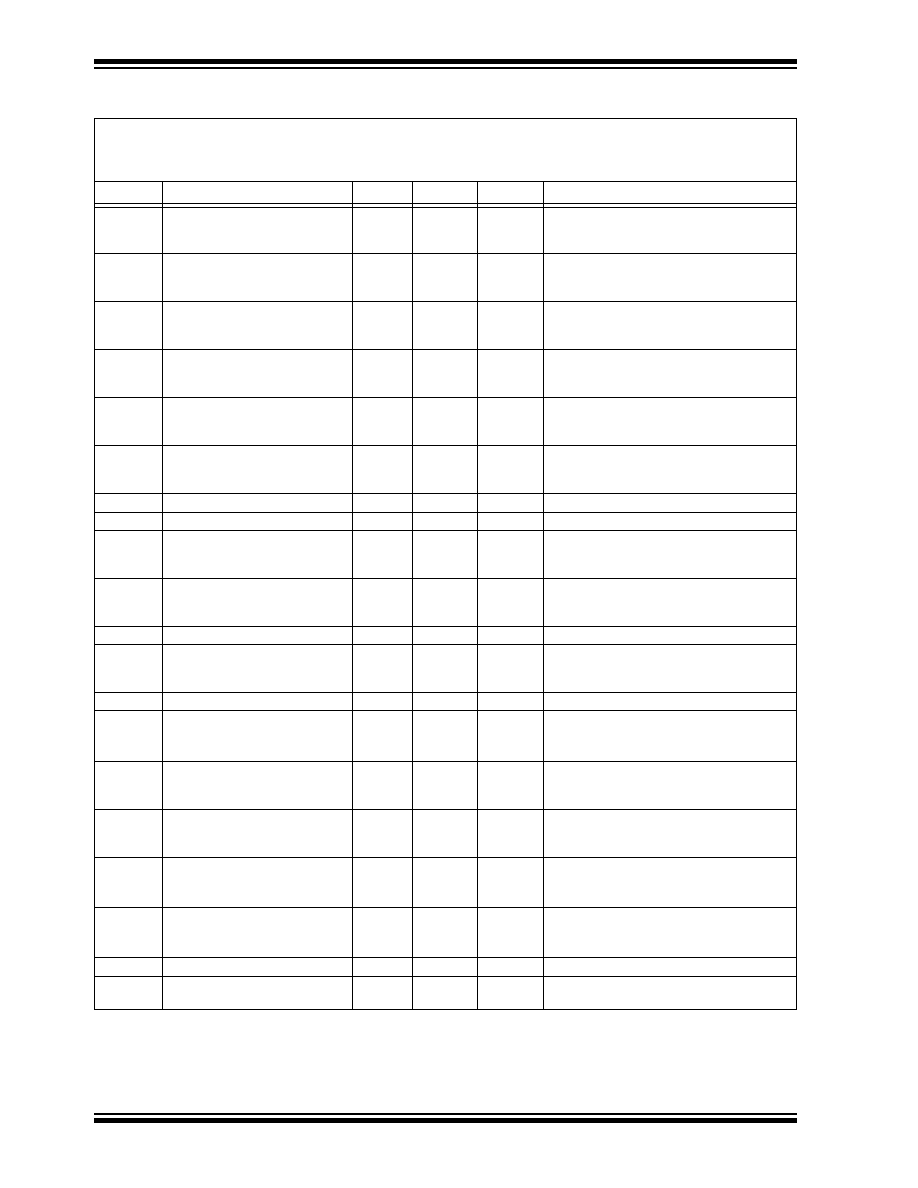

TABLE 1-3:

AC CHARACTERISTICS

Applicable over recommended operating ranges shown below unless otherwise noted.

VCC = +1.8V to 5.5V

Commercial (C):

Tamb = 0∞C to +70∞C

Industrial (I):

Tamb = -40

∞

C to +85

∞

C

Symbol

Parameter

Min

Max

Units

Test Conditions

fSCK

Clock Frequency

--

--

--

3

2

1

MHz

MHz

MHz

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tCSS

CS Setup Time

100

250

500

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tCSH

CS Hold Time

100

250

500

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tCSD

CS Disable Time

250

500

500

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tSU

Data Setup Time

30

50

50

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tHD

Data Hold Time

50

100

100

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tR

CLK Rise Time

--

2

µ

s

(Note 1)

tF

CLK Fall Time

--

2

µ

s

(Note 1)

tHI

Clock High Time

150

250

475

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tLO

Clock Low Time

150

250

475

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tCLD

Clock Delay Time

50

--

ns

tV

Output Valid from

Clock Low

--

--

--

150

250

475

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tHO

Output Hold Time

0

--

ns

tDIS

Output Disable Time

--

--

--

200

250

500

ns

ns

ns

VCC=4.5V to 5.5V (Note 1)

VCC=2.5V to 4.5V (Note 1)

VCC=1.8V to 2.5V (Note 1)

tHS

HOLD Setup Time

100

100

200

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tHH

HOLD Hold Time

100

100

200

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V

VCC=2.5V to 4.5V

VCC=1.8V to 2.5V

tHZ

HOLD Low to Output High-Z

100

150

200

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V (Note 1)

VCC=2.5V to 4.5V (Note 1)

VCC=1.8V to 2.5V (Note 1)

tHV

HOLD High to Output Valid

100

150

200

--

--

--

ns

ns

ns

VCC=4.5V to 5.5V (Note 1)

VCC=2.5V to 4.5V (Note 1)

VCC=1.8V to 2.5V (Note 1)

tWC

Internal Write Cycle Time

--

5

ms

(Note 2)

--

Endurance

10M

--

E/W

Cycles

25

∞

C, Vcc = 5.0V, Block Mode (Note 3)

Note 1:

This parameter is periodically sampled and not 100% tested.

2:

twc begins on the rising edge of CS after a valid write sequence and ends when the internal self-timed write cycle is com-

plete.

3:

This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please

consult the Total Endurance Model which can be obtained on our BBS or website.

This document was created with FrameMaker 4 0 4

©

1996 Microchip Technology Inc.

Preliminary

DS21146D-page 5

25AA080/160

2.0

PRINCIPLES OF OPERATION

The 25AA080/160 is an 1024/2048 byte EEPROM

designed to interface directly with the Serial Peripheral

Interface (SPI) port of many of today's popular micro-

controller families, including Microchip's midrange

PIC16CXX microcontrollers. It may also interface with

microcontrollers that do not have a built-in SPI port by

using discrete I/O lines programmed properly with soft-

ware.

The 25AA080/160 contains an 8-bit instruction register.

The part is accessed via the SI pin, with data being

clocked in on the rising edge of SCK. If the WPEN bit in

the status register is set, the WP pin must be held high

to allow writing to the non-volatile bits in the status reg-

ister.

Table 2-1 contains a list of the possible instruction bytes

and format for device operation. All instructions,

addresses and data are transferred MSB first, LSB last.

Data is sampled on the first rising edge of SCK after CS

goes low. If the clock line is shared with other peripheral

devices on the SPI bus, the user can assert the HOLD

input and place the 25AA080/160 in `HOLD' mode.

After releasing the HOLD pin, operation will resume

from the point when the HOLD was asserted.

2.1

Write Enable (WREN) and Write

Disable (WRDI)

The 25AA080/160 contains a write enable latch. This

latch must be set before any write operation will be

completed internally. The WREN instruction will set the

latch, and the WRDI will reset the latch. The following is

a list of conditions under which the write enable latch

will be reset:

∑ Power-up

∑ WRDI instruction successfully executed

∑ WRSR instruction successfully executed

∑ WRITE instruction successfully executed

2.2

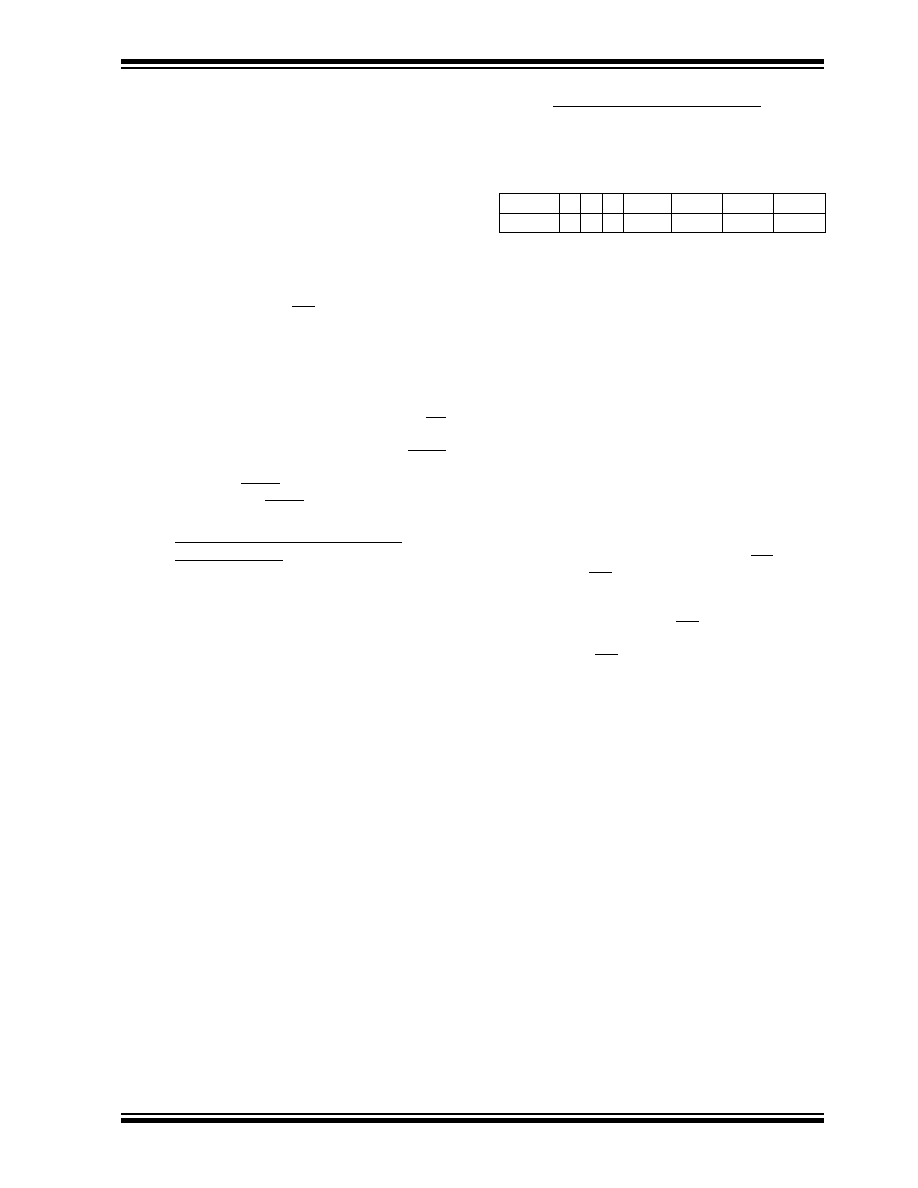

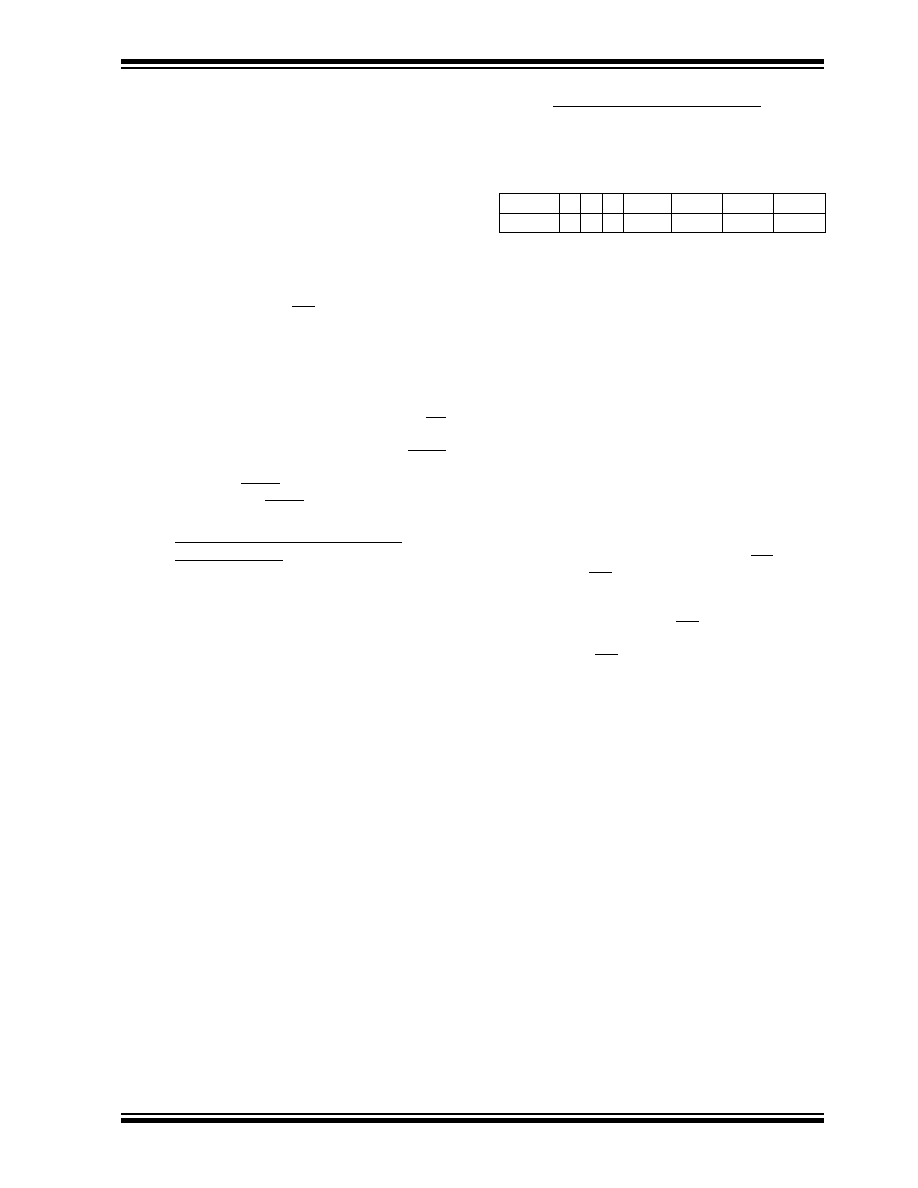

Read Status Register (RDSR)

The RDSR instruction provides access to the status

register. The status register may be read at any time,

even during a write cycle. The status register is format-

ted as follows:

The Write-In-Process (WIP) bit indicates whether the

25AA080/160 is busy with a write operation. When set

to a `1' a write is in progress, when set to a `0' no write

is in progress. This bit is read only.

The Write Enable Latch (WEL) bit indicates the status

of the write enable latch. When set to a `1' the latch

allows writes to the array and status register, when set

to a `0' the latch prohibits writes to the array and status

register. The state of this bit can always be updated via

the WREN or WRDI commands regardless of the state

of write protection on the status register. This bit is read

only.

The Block Protection (BP0 and BP1) bits indicate

which blocks are currently write protected. These bits

are set by the user issuing the WRSR instruction.

These bits are non-volatile.

The Write Protect Enable (WPEN) bit is a non-volatile

bit that is available as an enable bit for the WP pin. The

Write Protect (WP) pin and the Write Protect Enable

(WPEN) bit in the status register control the program-

mable hardware write protect feature. Hardware write

protection is enabled when WP pin is low and the

WPEN bit is high. Hardware write protection is disabled

when either the WP pin is high or the WPEN bit is low.

When the chip is hardware write protected, only writes

to non-volatile bits in the status register are disabled.

See Table 2-2 for matrix of functionality on the WPEN

bit and Figure 2-1 for a flowchart of Table 2-2.

See Figure 3-5 for RDSR timing sequence.

7

6

5

4

3

2

1

0

WPEN

X

X

X

BP1

BP0

WEL

WIP