MD400184/A

1

84221

Features

s

Single Chip 100BaseTX/10BaseT

Physical Layer Solution

s

Four Independent Channels in One IC

s

3.3V Power Supply with 5V Tolerant I/O

s

Dual Speed - 10/100 Mbps

s

Half and Full Duplex

s

Reduced Pin Count MII (RMII) Interface to

Ethernet Controller

s

MI Interface for Configuration and Status

s

Optional Repeater Interface

s

AutoNegotiation for 10/100, Full/Half Duplex

Hardware Controlled Advertisement

s

Meets all Applicable IEEE 802.3, 10BaseT,

100BaseTX Standards

s

On Chip Wave Shaping - No External Filters

Required

s

Adaptive Equalizer for 100BaseTX

s

Baseline Wander Correction

s

LED Outputs

Link

Activity

Collision

Full Duplex

10/100

s

128L PQFP

Description

The 84221 is a highly integrated Ethernet Transceiver for

twisted pair and fiber Ethernet applications. The 84221

can be configured for either 100BaseTX or 10BaseT

Ethernet operation.

The 84221 consists of four (4) separate and independent

channels. Each channel consists of: 4B5B/Manchester

encoder, scrambler, transmitter with wave shaping and on-

chip filters, transmit output driver, receiver with adaptive

equalizer, filters, baseline wander correction, clock and

data recovery, descrambler, 4B5B/Manchester decoder,

and controller interface (MII or RMII).

The addition of internal output waveshaping circuitry and

on-chip filters eliminates the need for external filters

normally required in 100BaseTX and 10BaseT

applications.

The 84221 can automatically configure itself for 100 or 10

Mbps and Full or Half Duplex operation, for each channel

independently, using the on-chip AutoNegotiation

algorithm.

The 84221 can access eleven 16-bit registers for each

channel through the Management Interface (MI) serial

port. These registers comply to Clause 22 of IEEE 802.3u

and contain configuration inputs, status outputs, and

device capabilities.

The 84221 is ideal as a media interface for 100BaseTX/

10BaseT switching hubs, repeaters, routers, bridges, and

other multi port applications.

The 84221 is implemented in a low power CMOS

technology and operates with a 3.3V power supply.

84221

99191

Quad 100BaseTX/10BaseT

Physical Layer Device

PRELIMINARY

Note: Check for latest Data Sheet revision before

starting any designs.

SEEQ Data Sheets are now on the Web, at

www.lsilogic.com

This document is an LSI Logic document. Any

reference to SEEQ Technology should be consid-

ered LSI Logic.

4

MD400184/A

84221

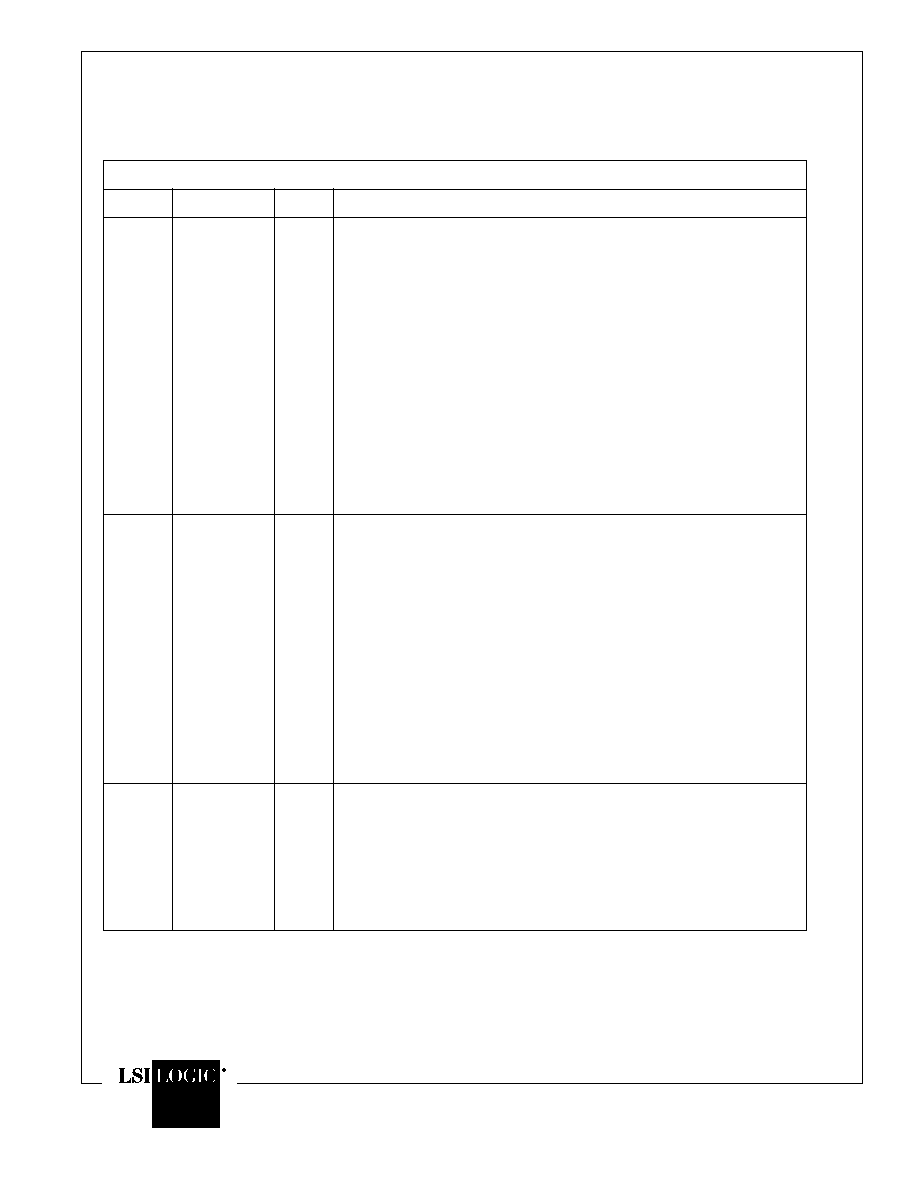

1.0 PIN DESCRIPTION (cont'd)

Media Interface

Pin #

Pin Name

I/O

Description

7

16

24

33

TPOP_[3:0]

O

Twisted Pair Transmit Output, Positive.

10

13

27

30

TPON_[3:0]

O

Twisted Pair Transmit Output, Negative.

4

18

21

35

TPIP_[3:0]

I

Twisted Pair Receive Input, Positive.

5

17

22

34

TPIN_[3:0]

I

Twisted Pair Receive Input, Negative.

19

REXT

--

Transmit Current Set.

An external resistor connected between this pin and GND will set the level

for the transmit outputs.

MD400184/A

5

84221

1.0 PIN DESCRIPTION (cont'd)

Controller Interface (RMII)

Pin #

Pin Name

I/O

Description

127

CLKIN

I

Clock Input.

This controller interface input latches controller interface data in and out of

the device on rising edges for all channels. There must be a 50 Mhz clock

tied to this pin.

104

91

75

61

TXEN_[3:0]

I

Transmit Enable Input.

These interface inputs must be be asserted active

high to allow data on TXD and TXER to be clocked in on the rising edges of

CLKIN.

[106:105]

[93:92]

[77:76]

[63:62]

TXD[1:0]_3

TXD[1:0]_2

TXD[1:0]_1

TXD[1:0]_0

I

Transmit Data Input.

These interface inputs contain input di-bit data to be

transmitted on the TP outputs and are clocked in on rising edges of CLKIN.

107

97

82

68

CRS_DV[3:0]

O

Carrier Sense Output.

These interface outputs are asserted active high

when valid data is detected on the receive TP inputs and is clocked out on

the rising edge of CLKIN.

[100:101]

[85:86]

[69:70]

[57:58]

RXD[1:0]_3

RXD[1:0]_2

RXD[1:0]_1

RXD[1:0]_0

O

Receive Data Output.

These interface outputs contain recovered di-bit data

from the TP inputs and are clocked out on the rising edges of CLKIN.

103

88

72

59

RXER_[3:0]

O

Receive Error Output.

These interface outputs are asserted active high

when coding or other specified errors are detected on the TP inputs and are

clocked out on rising edges of CLKIN.