| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: L64734 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

February 2001

1

Copyright © 2000, 2001 by LSI Logic Corporation. All rights reserved.

Æ

L64733C/L64734 Tuner and

Satellite Receiver Chipset

Datasheet

The L64733C/734 chipset is designed for satellite broadcast digital TV. It

is compliant with the European digital video broadcast (DVB-S) standard,

as well as the technical specifications for DSS systems. The

L64733C/734 chipset forms a complete "L-band-to-bits" system.

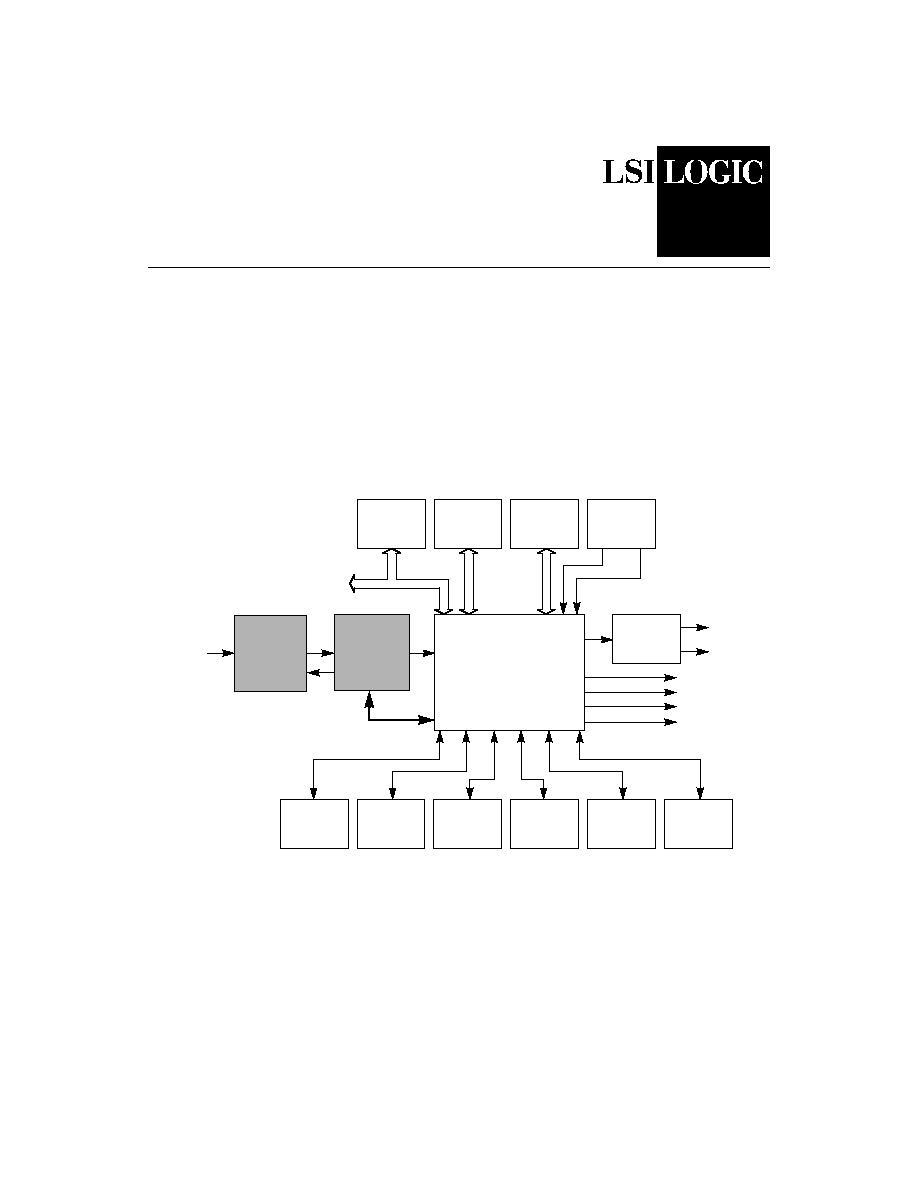

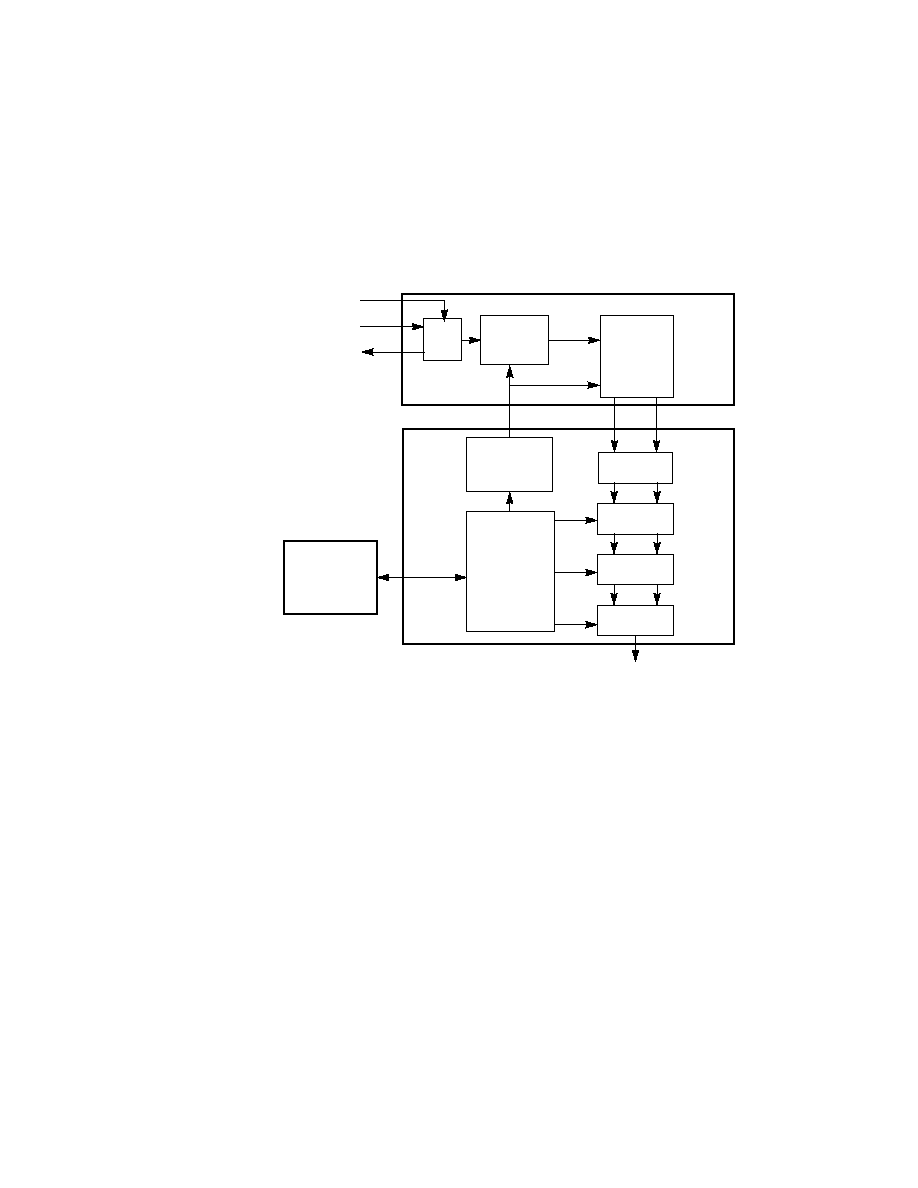

A typical application of the L64733C/734 chipset is satellite digital TV

reception in accordance with the ETS 300 421 standard. Figure 1 shows

the L64733C/734 chipset satellite receiver implemented in a typical

satellite receiver set-top decoder.

Figure 1

Set-Top Box Block Diagram

The L64733C Tuner IC directly down-converts the satellite signal from

L-band to baseband; it includes an on-chip synthesizer. Using frequency

information programmed into its configuration registers, the L64734

Satellite Receiver generates control signals for the L64733C synthesizer.

The L64734 also controls the programming of the low-pass filters on the

FLASH

SDRAM-B

SDRAM-A

27 MHz

VCXO

Expansion

Bus

Analog

Audio

Analog CVBS

Analog Y/C

Analog RGB

Digital Video

OP

AMPs

SC2000

Single-Chip

Source Decoder

GPIO

Pins

I/R

Rx & Tx

RS232-C

Interface

CODEC

IEEE

Smart

Serial Bus

Cards

1284

Satellite

RF Signal

L64733C

Tuner

L64734

Demodulator

2

L64733C/L64734 Tuner and Satellite Receiver Chipset

L64733C and generates dual automatic gain control (AGC) voltages for

the two-stage automatic gain control on the L64733C. A simplified

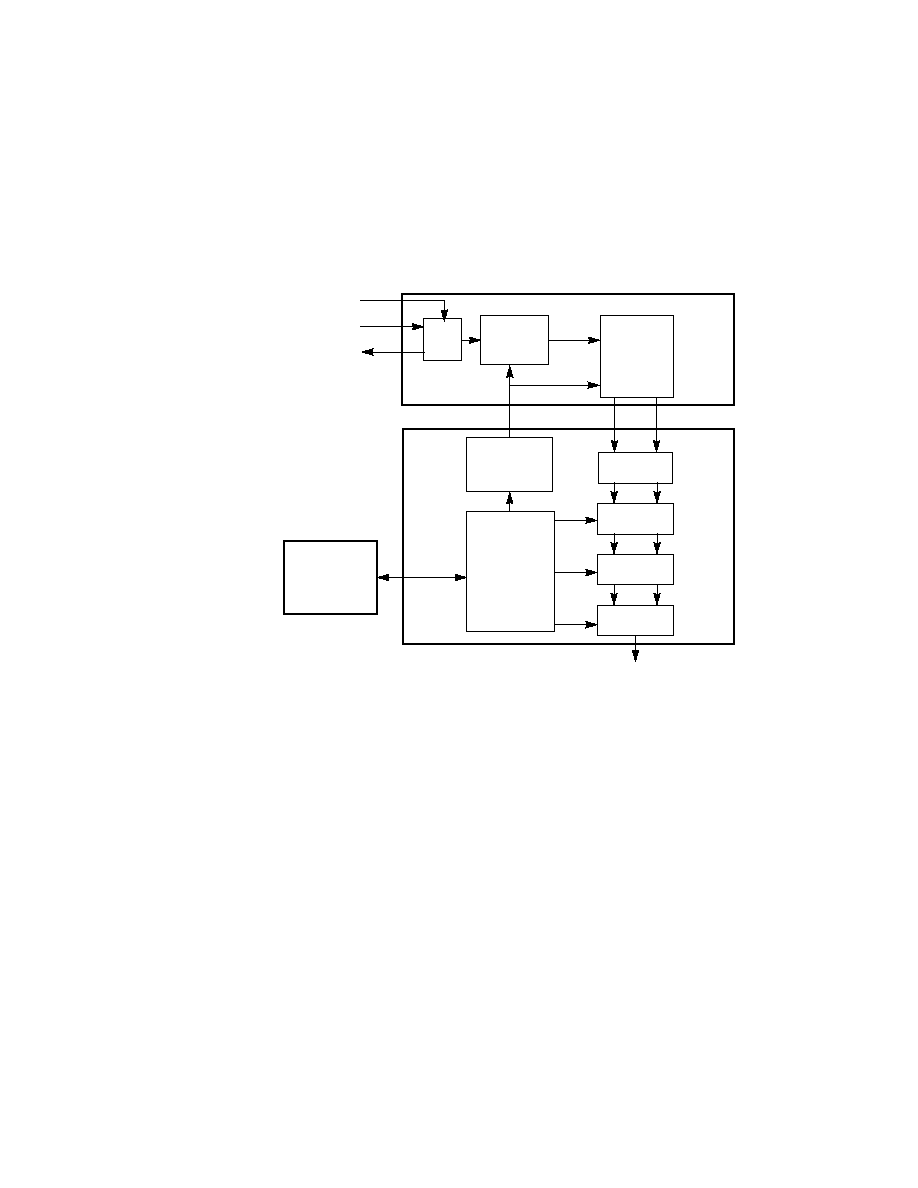

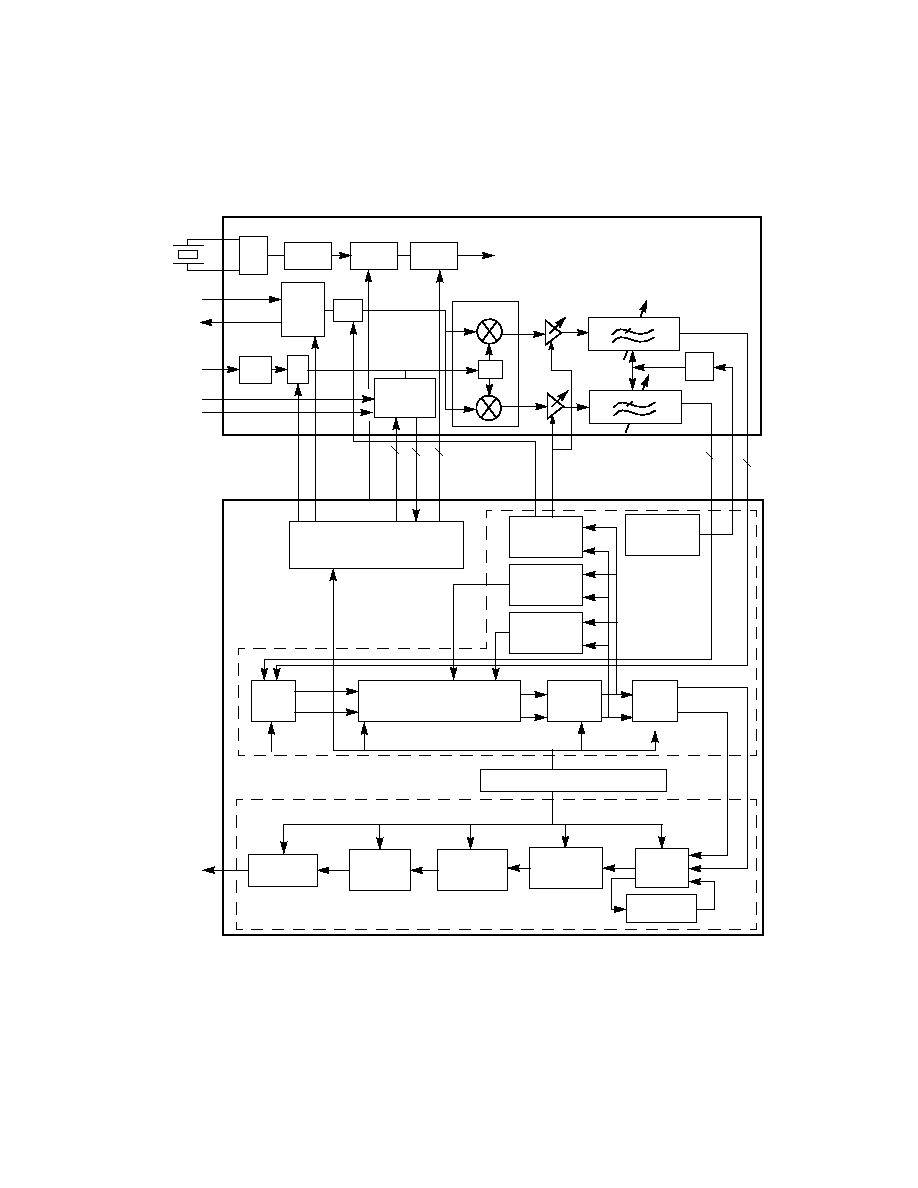

chipset block diagram is shown in Figure 2.

Figure 2

L64733C/734 Simplified Block Diagram

Figure 3 shows a more detailed chipset block diagram.

The L64733C accepts the RF In L-Band signal input from the satellite

low noise block (LNB) feed. The L64733C handles a fully loaded raster

of transponder signals from 925 MHz to 2175 MHz. RF In is internally

matched to 75

; it requires no matching network between the cable

connector and the L64733C input pins, except for a DC-blocking

capacitor. The L64733C uses the L64734 INSEL signal to select the

appropriate RF function (Normal or Loop-Through Mode).

RF

RF Input

RF Output

Select

IOUT QOUT

Dual ADC

Demodulator

Error

Correction

Descrambler

Microcontroller

Interface

Microcontroller

Host

Control

Modules for

MPEG Output

L64733C

L64734

Control Signals

Mixer,

Down

Conversion

Baseband

Filter

Synthesizer

and Filter

Switch

L64733C/L64734 Tuner and Satellite Receiver Chipset

3

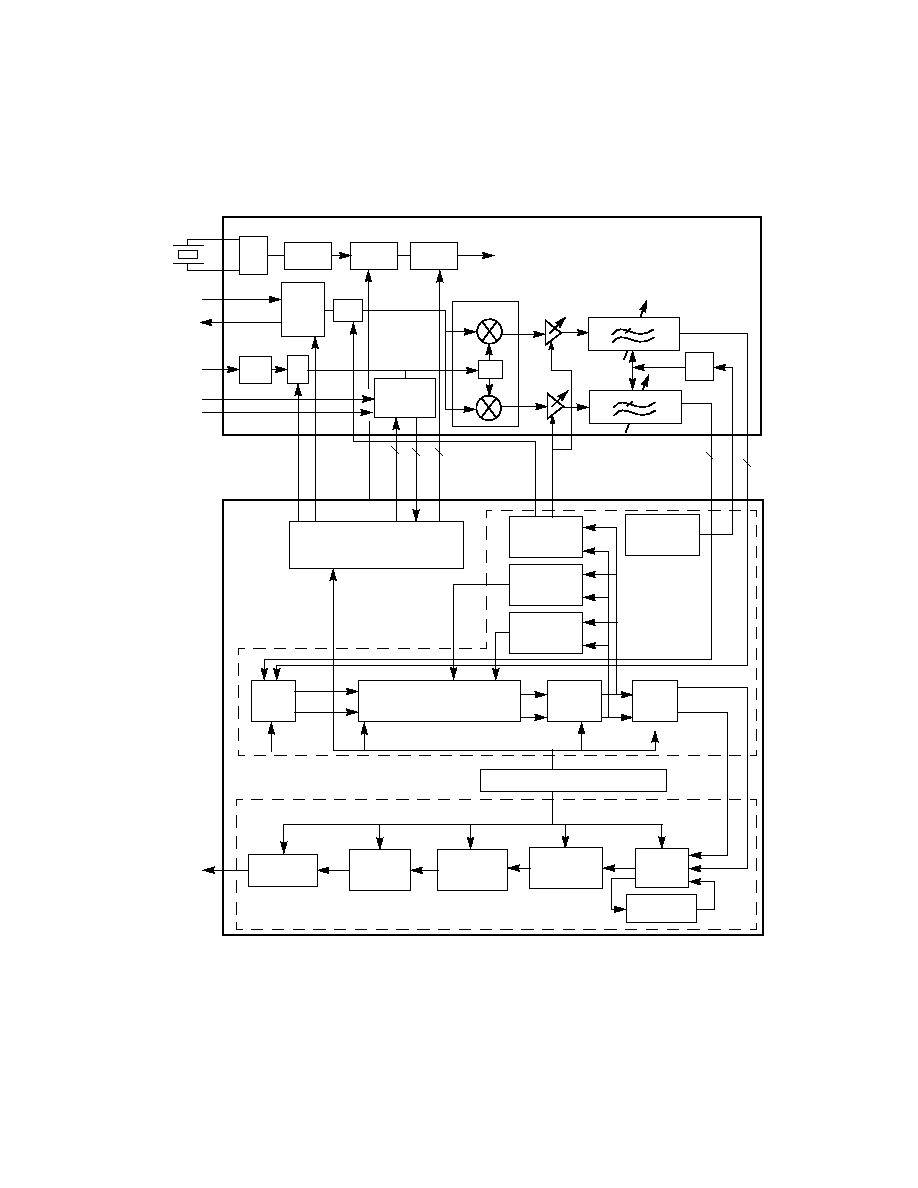

Figure 3

Detailed Chipset Block Diagram

Filter

Matched

Filter

Carrier

Loop Control

AGC

Control

Timing Loop

Control

Output

Control

I

Q

1/T

Descrambler

Dual

ADC

Interpolator/Decimation

External Microcontroller Interface

Clk

(from L64734

on-chip PLL)

Xtal

Osc

Phase

RF In

RF Out

RF

Charge

Pump

Fc

90

∞

VCO

X2

Tank

Circuit

PLLIN

FDOUB

MOD

PSOUT

CPG

A

GC1

INSEL

IOUT

QOUT

FLCLK

Synthesizer Control Module

L64734

L64733C

Detect.

Filter

Control

Module

Amp

To external

Loop Filter

˜

by 8

Quadrature

Down-Converter

2

2

2

2

A

GC2

4≠7.26 MHz

BPSK/QPSK

Demodulator

Microcontroller Data and Address Bus

Microcontroller Data and Address Bus

FEC Decoder Pipeline

Channel

Output

(MPEG-2

Transport

Stream)

Reed-

Solomon

Decoder

Convolutional

Deinterleaver

Reed-

Solomon

Synchronizer

Viterbi

Synchronizer

Viterbi

Decoder

Switch

2

LOBUF

LODIV

˜

32/33

or

˜

1/2

4

L64733C/L64734 Tuner and Satellite Receiver Chipset

The RF signal is sent to a variable gain stage controlled by the L64734

AGC1 signal. The L64734 adjusts AGC1 in conjunction with AGC2 to

maximize the SNR of the RF In signal while maintaining proper levels at

the baseband outputs (IOUT and QOUT). The signal then is fed to two

mixers in the quadrature demodulator. The mixers are fed with local

oscillator signals that are offset by 90 degrees from one another. The

quadrature demodulator converts the frequency of the RF In signal

directly to baseband while splitting the signal into quadrature I and Q

signal paths.

The baseband signals pass through a pair of variable gain amplifiers,

controlled through the AGC2 pin by the L64734. The signals then pass

through a pair of seventh-order filters for antialiasing. The filter shape is

seventh-order Butterworth, followed by a single-pole delay equalizer. The

L64734 FLCLK signal controls the filter cutoff frequency, which is related

to the baud rate. The filtered baseband output signals are fed to

differential output stages at IOUTp, IOUTn, QOUTp, and QOUTn.

The baseband outputs of the L64733C are sent to the L64734 to be

digitized by the analog-to-digital converter (ADC). Then, they are sent to

a BPSK/QPSK demodulator, filtered, and sent to the L64734 forward

error correction (FEC) decoder pipeline, which outputs an MPEG-2

transport stream.

The frequency synthesizer functionality is split between the L64733C and

L64734. The Synthesizer Control Module resides on the L64734 and

generates control signals for the L64733C Tuner IC frequency

synthesizer. The Synthesizer Control Module also contains

programmable counters for the synthesizer feedback loop.

The L64733C provides analog functions for the frequency synthesizer,

the RF local oscillator, and the crystal reference oscillator. Tuning

oscillator signals are generated for the mixers in the 925≠2175 MHz

range, with a 0.625 MHz step size when using a 5 MHz crystal reference.

The on-chip VCO tuning frequency is 543≠1088 MHz. To tune channels

from 925≠1086 MHz, the L64734 disables the frequency doubler (X2

block) on the L64733C. To tune channels from 1086≠2175 MHz, the

L64734 enables the frequency doubler.

The L64733C can improve half-harmonic rejection. It requires special

programming of the frequency doubler control pin (FDOUB), which now

L64733C/L64734 Tuner and Satellite Receiver Chipset

5

has 3-state operation (see the "Synthesizer Control Interface" section on

page 20).

The VCO requires an external resonant tank circuit, which includes

varactor diodes to vary the frequency of oscillation.

The VCO signal is fed to the Prescaler block before being passed

deferentially through the PSOUTp and PSOUTn pins to the L64734. The

L64734 MODp and MODn differential signals control the divider ratio for

the Prescaler block. The L64734 dynamically changes the divide ratio to

ensure that the tuning step size is not affected by the divider. The

L64734 contains programmable counters to further divide the signal

frequency before it is fed back to the L64733C through the PLLINp and

PLLINn pins. The crystal reference oscillator frequency is divided by

eight and fed to the phase detector. The phase detector generates a

current signal proportional to the difference in phase between PLLINp,

PLLINn, and the divided crystal frequency. A charge pump circuit

generates current that controls pins CP and FB, and an external

transistor to buffer the L64733C against the tuning voltage (28 V). The

current is passed through a discrete loop filter and is converted to a

tuning voltage that drives the external varactor diodes for the VCO tank

circuit. A frequency controlled loop is formed. Changing the frequency

divider ratios in the L64734 registers varies the VCO frequency. See

Figure 7, on page 23, for more details regarding the external circuitry for

the VCO, crystal oscillator, charge pump, tank circuitry, and

frequency-controlled loop.

The chipset provides maximum integration and flexibility for system

designers at a minimum cost. The number of external components

required to build a system is minimal because the synthesizer, variable

rate filters, and clock and carrier loops are integrated into the two

devices.