Document Outline

- crc MegaCore Function Parameterized CRC Generator/Checker Data Sheet

Æ

Altera Corporation

1

crc MegaCore Function

Parameterized CRC

Generator/Checker

April 1999, ver. 2

Data Sheet

A-DS-CRC-02

Features

s

crc

MegaCore

TM

function, general-purpose cyclic redundancy code

(CRC) generator and checker

s

Optimized for the FLEX

Æ

device architecture

s

Supported by the MAX+PLUS

Æ

II development system

s

High-speed operation, over 100 MHz for many configurations

s

Fully parameterized, including:

≠

Any length generator polynomial

≠

Input data width, from 1 bit to the width of the polynomial

≠

Any initial value

s

Built-in support for:

≠

Inverting output data

≠

Reflecting (reversing bit order) input and output data

General

Description

The

crc

MegaCore function is a general-purpose CRC generator and

checker that validates data frames and ensures that data corruption

during transmission is detected. The

crc

function is fully parameterized,

and therefore can be used in virtually any design that requires a CRC

checker. See

Figure 1

.

Figure 1. crc Symbol

CRC

POLY[ ]

XOROUT[ ]

CLOCK

ACLR

SLOAD

RUN_NSHIFT

INIT[ ]

DATA_IN[ ]

ENABLE

CRC_OUT[ ]

WIDTH=

SHIFT="NO"

REFIN="NO"

REFOUT="NO"

WPAR=1

USE_CARRY="NO"

2

Altera Corporation

crc MegaCore Function Parameterized CRC Generator/Checker Data Sheet

AHDL Function Prototype

The Altera

Æ

Hardware Description Language (AHDL) Function

Prototype of the

crc

function is shown below:

FUNCTION crc (poly[WIDTH-1..0], xorout[WIDTH-1..0], clock,

aclr, sload, run_nshift, init[WIDTH-1..0],

data_in[WPAR-1..0], enable)

WITH (WIDTH, SHIFT, REFOUT, REFIN, WPAR, USE_CARRY)

RETURNS (crc_out[WIDTH-1..0]);

VHDL Component Declaration

The VHDL Component Declaration of the

crc

function is shown below:

COMPONENT crc

GENERIC (

WIDTH

: POSITIVE;

SHIFT

: STRING

:= "NO";

REFOUT

: STRING

:= "NO";

REFIN

: STRING

:= "NO";

WPAR

: POSITIVE

:= 1;

USE_CARRY

: STRING

:= "NO";

PORT (

poly

: IN STD_LOGIC_VECTOR

(WIDTH-1 DOWNTO 0);

xorout

: IN STD_LOGIC_VECTOR(WIDTH-1 DOWNTO 0)

:= (OTHERS => '0');

clock

: IN STD_LOGIC;

aclr

: IN STD_LOGIC

:= '0';

sload

: IN STD_LOGIC;

run_nshift : IN STD_LOGIC;

init

: IN STD_LOGIC_VECTOR(WIDTH-1 DOWNTO 0);

data_in

: IN STD_LOGIC_VECTOR(WPAR-1 DOWNTO 0);

enable

: IN STD_LOGIC

:= '1';

crc_out

: OUT

STD_LOGIC_VECTOR(WIDTH-1 DOWNTO 0) );

END COMPONENT;

Altera Corporation

3

crc MegaCore Function Parameterized CRC Generator/Checker Data Sheet

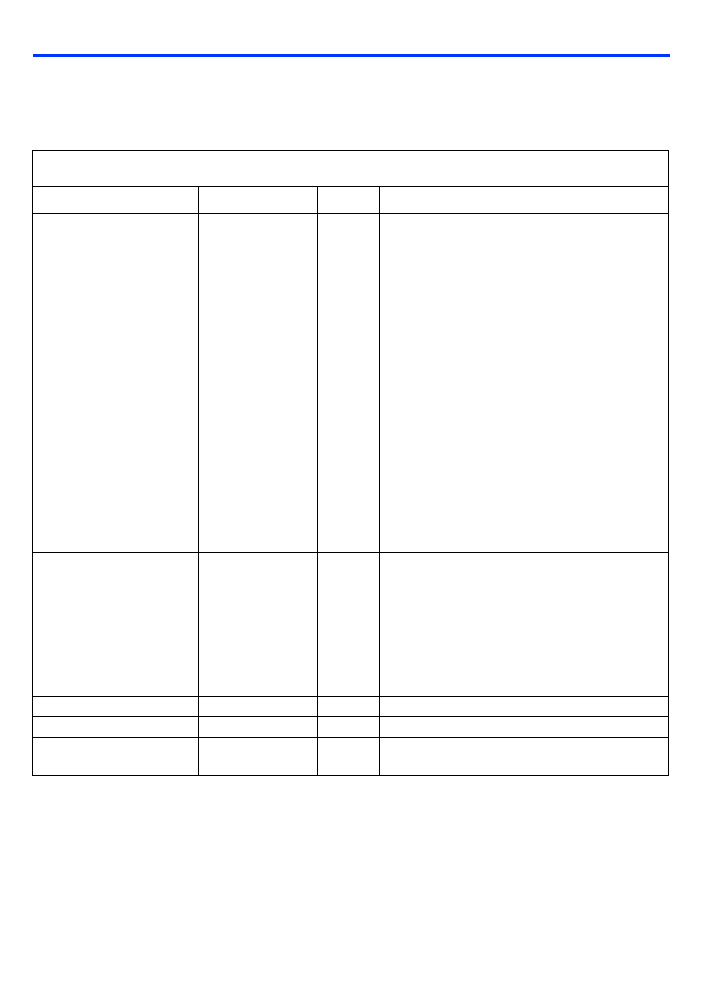

Parameters

Table 1

describes the parameters of the

crc

function.

Table 1. crc Parameters

Name

Required

Default

Description

WIDTH

Yes

--

Width of the generator polynomial.

SHIFT

No

"NO"

If

"YES"

is specified, the

run_nshift

input is used. If

"NO"

is specified, the

run_nshift

input is not used.

REFIN

No

"NO"

If

"YES"

is specified, the

crc

function will

reflect (bit reverse) the input data. The

REFIN

parameter allows a different bit

order, e.g., some algorithms require the

most significant bit (MSB) first, while

others require the least significant bit

(LSB) first.

REFOUT

No

"NO"

Specifies whether or not the output data

bits are reflected.

WPAR

No

1

The

WPAR

parameter indicates the width

of the input word. Some systems require

data to be processed one bit at a time. In

this case,

WPAR

would be set to

1

. Other

systems require that data be processed in

bytes, words, or double words. In this

case,

WPAR

would be set to

8

,

16

, or

32

respectively. The

WPAR

parameter may

be any factor of

WIDTH

.

USE_CARRY

No

"NO"

Specifies whether or not carry chain logic

is used during synthesis.

4

Altera Corporation

crc MegaCore Function Parameterized CRC Generator/Checker Data Sheet

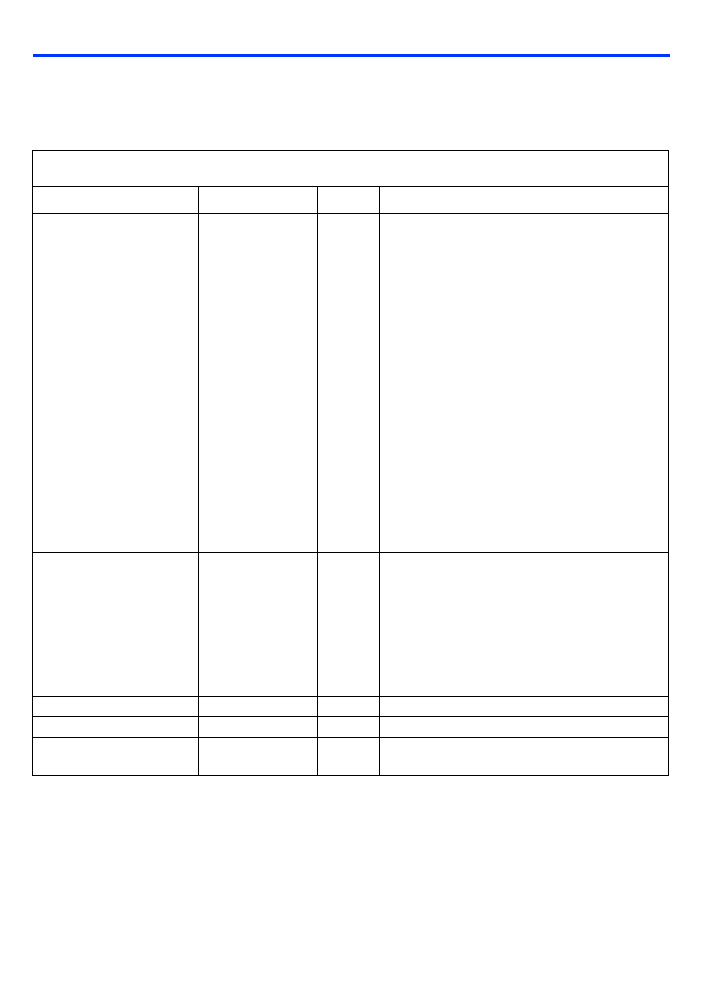

Ports

Table 2

describes the input and output ports of the

crc

function.

Table 2. crc Ports (Part 1 of 2)

Name

Required

Type

Description

poly[WIDTH-1..0]

Yes

Input

The

poly[WIDTH-1..0]

input is used to define

the generator polynomial. However, the

polynomial must first be converted to a binary

value. For example, the CRC-16 generator

polynomial is defined as: X

16

+ X

15

+ X

2

+ X

0

, and

can be transformed into a binary number by

placing a logic 1 in every position where there is a

non-zero power in the generator polynomial.

Thus, the CRC-16 generator polynomial equals

the following 17-bit binary number:

11000000000000101

.

Because every generator polynomial has a logic 1

as its MSB, the MSB is left off when specifying the

polynomial as a binary number. Thus, the 17-bit

binary number, which represents the CRC-16

generator polynomial, becomes the following

16-bit binary number:

B"1000000000000101"

or

H"8005"

.

xorout[WIDTH-1..0]

No (Default =

GND

)

Input

Some CRC algorithms specify that the CRC

register value be inverted before being output.

When using one of these algorithms, the

xorout[WIDTH-1..0]

input specifies which bits

should be inverted, e.g., any bit with a logic 1

value in the

xorout[WIDTH-1..0]

word will be

inverted between the CRC register and the

crc_out[WIDTH-1..0]

output.

clock

Yes

Input

Clock input.

aclr

No

Input

Asynchronous clear.

sload

Yes

Input

Synchronous load. Loads the value on the

init[WIDTH-1..0]

bus into the CRC register.

Altera Corporation

5

crc MegaCore Function Parameterized CRC Generator/Checker Data Sheet

Table 3

summarizes the parameters for several standard CRC algorithms,

including the algorithm width, polynomial value, initial value

(hexadecimal radix), whether the bit order of the input and output data is

reversed (reflected), the

XOR

ed output, and

check

values.

run_nshift

No

Input

Run/shift. When high, the

crc

function is

operating as a CRC generator. When this input is

low and the

SHIFT

parameter is set to

"YES"

, the

crc

register is serially shifted to the right.

init[WIDTH-1..0]

Yes

Input

The

init[WIDTH-1..0]

input specifies the

initial value of the CRC register when the

algorithm starts. This input allows the designer to

dynamically place any value into the CRC register

whenever the

sload

input is high, which also

allows the designer to initialize the CRC register

synchronously. The

init[WIDTH-1..0]

input is

used for both setting the initial value of the CRC

and starting mid-stream.

In many systems, such as networking

applications, data frames from different data

streams are received in an interleaved order. For

multiple data streams where the CRC must be

calculated over many data frames, intermediate

CRC values can be stored and loaded from a

RAM buffer.

data_in[WPAR-1..0]

Yes

Input

Input data stream.

enable

No

Input

Clock enable

crc_out[WIDTH-1..0]

Yes

Output

Computed CRC output.

Table 2. crc Ports (Part 2 of 2)

Name

Required

Type

Description