| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AK6012A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

ASAHI KASEI

[AK6010A/12A]

DAI02E-03

2002/11

- 1 -

AK6010A / 12A

I

2

C bus 32K / 64Kbit Serial CMOS EEPROM

Features

ADVANCED CMOS EEPROM TECHNOLOGY

READ/WRITE NON-VOLATILE MEMORY

WIDE VCC OPERATION : VCC = 1.8V to 5.5V

AK6010A 32768 bits, 4096 x 8 organization

AK6012A

65536 bits, 8192 x 8 organization

I

2

C

TM

SERIAL INTERFACE

LOW POWER CONSUMPTION

- 0.8µA Max. Standby

HIGH RELIABILITY

- Endurance

: 100K cycles

- Data Retention : 10 years

32 byte Page Write Mode

Automatic write cycle time-out with auto-ERASE

IDEAL FOR LOW DENSITY DATA STORAGE

- Low cost, space saving, 8-pin package (SOP)

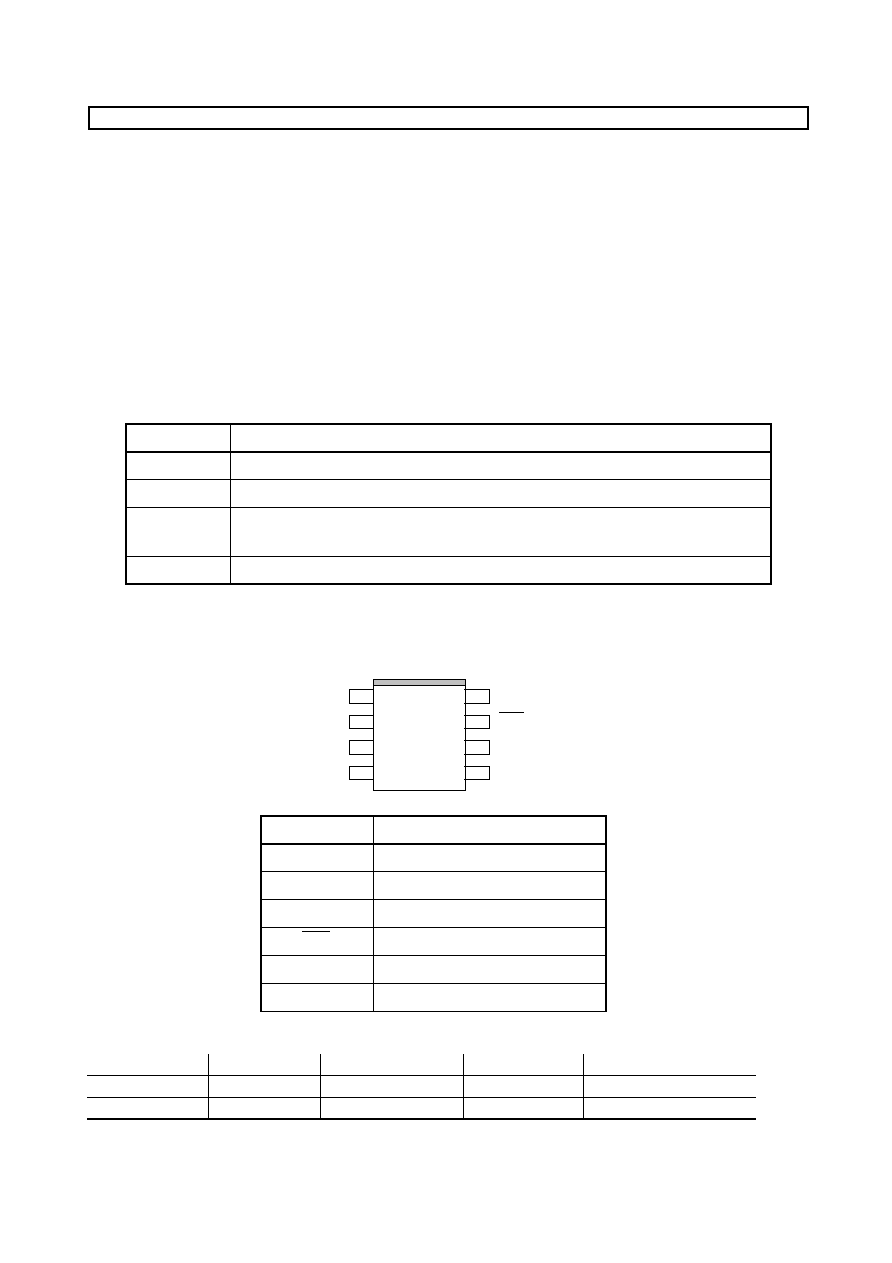

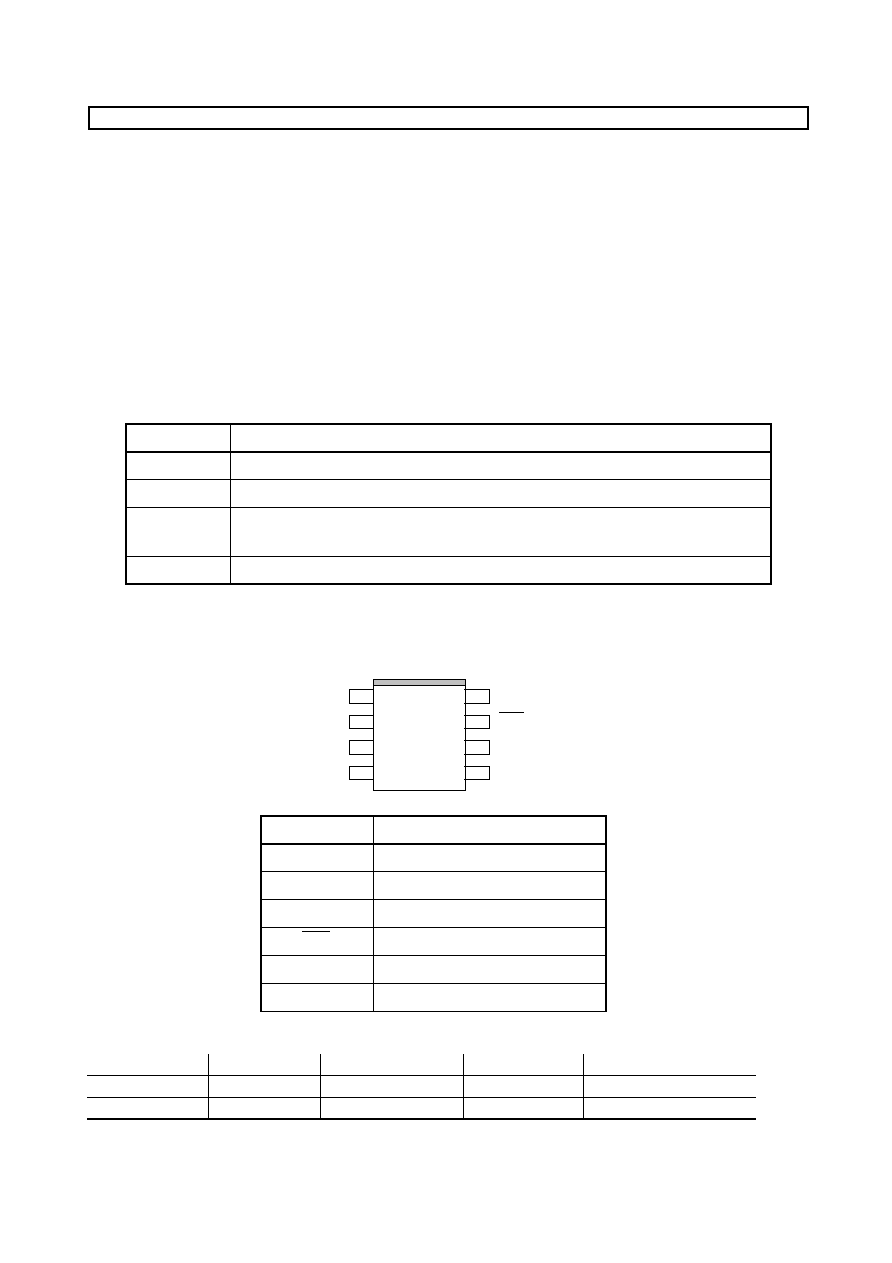

Block Diagram

I

2

C

TM

is a registered trademark of Philips Corporation.

SLAVE ADDRESS

REGISTER

+COMPARATOR

START

STOP

LOGIC

VCC

GND

WC

SDA

SCL

S2

S1

CONTROL

LOGIC

WORD

ADDRESS

COUNTER

XDEC

AK6010A = 32768bit

AK6012A = 65536bit

EEPROM

H.V.GENERATION

TIMING

& CONTROL

YDEC

DATA REGISTER

DOUT

ACK

S0

ASAHI KASEI

[AK6010A/12A]

DAI02E-03

2002/11

- 2 -

General Description

The AK6010A/12A is a 32768/65536-bit serial CMOS EEPROM divided into 4096/8192 registers of

8 bits each.

The AK6010A/12A can operate full function under wide operating voltage range from 1.8V to 5.5V.

The charge up circuit is integrated for high voltage generation that is used for write operation.

The AK6010A/12A conforms to all specifications in the 2 wire protocol and is controlled by serial

clock (SCL) and serial data (SDA) line.

Some devices can be connected to the same bus. Each device connected to the bus is software

addressable by a unique address, and can operate as either a transmitter or receiver. In addition

to transmitters and receivers, devices can also be considered as masters or slaves when performing

data transfers (see Table1). The master is the device which initiates a data transfers on the bus

and generates the clock signals to permit that transfer. At that time, the device addressed is

considered as the slave.

TERM DESCRIPTION

Transmitter The device which sends the data to the bus

Receiver

The device which receives the data from the bus

Master

The device which initiates a transfer, generates clock signals and

terminates a transfer

Slave

The device addressed by a master

Table 1. Definitions

Pin arrangement

Pin Name

Function

S0, S1, S2

Device Address Inputs

SCL Clock

Input

SDA

Data Input / Output

WC Write

Control

VCC Power

Supply

GND Ground

Type of Products

Model

Memory size

Temp. Range

VCC

Package

AK6010AF

32K bits

-40∞C to +70∞C

1.8V to 5.5V

8pin Plastic SOP

AK6012AF

64K bits

-40∞C to +70∞C

1.8V to 5.5V

8pin Plastic SOP

AK6010A/12A

GND

S2

S0

S1

2

1

3

4

VCC

7

8

6

5 SDA

SCL

WC

ASAHI KASEI

[AK6010A/12A]

DAI02E-03

2002/11

- 3 -

DATA TRANSFER

All commands are preceded by a START condition. After the START condition, a slave address is

sent. After the AK6010A/12A recognizes the START condition, the devices interfaced to the bus

wait for the slave address to be transmitted over the SDA line. If the transmitted slave address

matches an address of one of the devices, the designated slave pulls the SDA line to LOW

(ACKNOWLEDGE).

The data transfer is always terminated by a STOP condition generated by the master.

[Data validity]

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW

state of the data line can only change when the clock signal on the SCL line is LOW.

Figure 1. Data transfer

[START and STOP condition]

A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. All

commands are preceded by the START condition.

A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition. All

communications are terminated by the STOP condition. After a read sequence, the STOP

condition will place the EEPROM in a standby power mode.

Figure 2. Start and Stop Definition

DATA STABLE

DATA

CHANGE

SDA

SCL

START CONDITION

SDA

SCL

STOP CONDITION

ASAHI KASEI

[AK6010A/12A]

DAI02E-03

2002/11

- 4 -

[ACKNOWLEDGE]

ACKNOWLEDGE is a software convention used to indicate successful data transfers. The

transmitting device will release the bus after transmitting eight bits. During the next clock (ninth

clock), the receiver will pull the SDA line to LOW to acknowledge that it received the eight bits of

data.

The AK6010A/12A will respond with an acknowledge after recognition of a start condition and its

slave address. If both the device and a write operation have been selected, the AK6010A/12A will

respond with an acknowledge after the receipt of each subsequent eight bit word.

In the read mode the AK6010A/12A slave will transmit eight bits of data, release the SDA line and

monitor the line for an acknowledge. If an acknowledge is detected and no STOP condition is

generated by the master, the slave will continue to transmit data. If an acknowledge is not

detected, the slave will terminate further data transmissions and await the STOP condition to return

to the standby power mode.

Figure 3. Acknowledge Response from Receiver

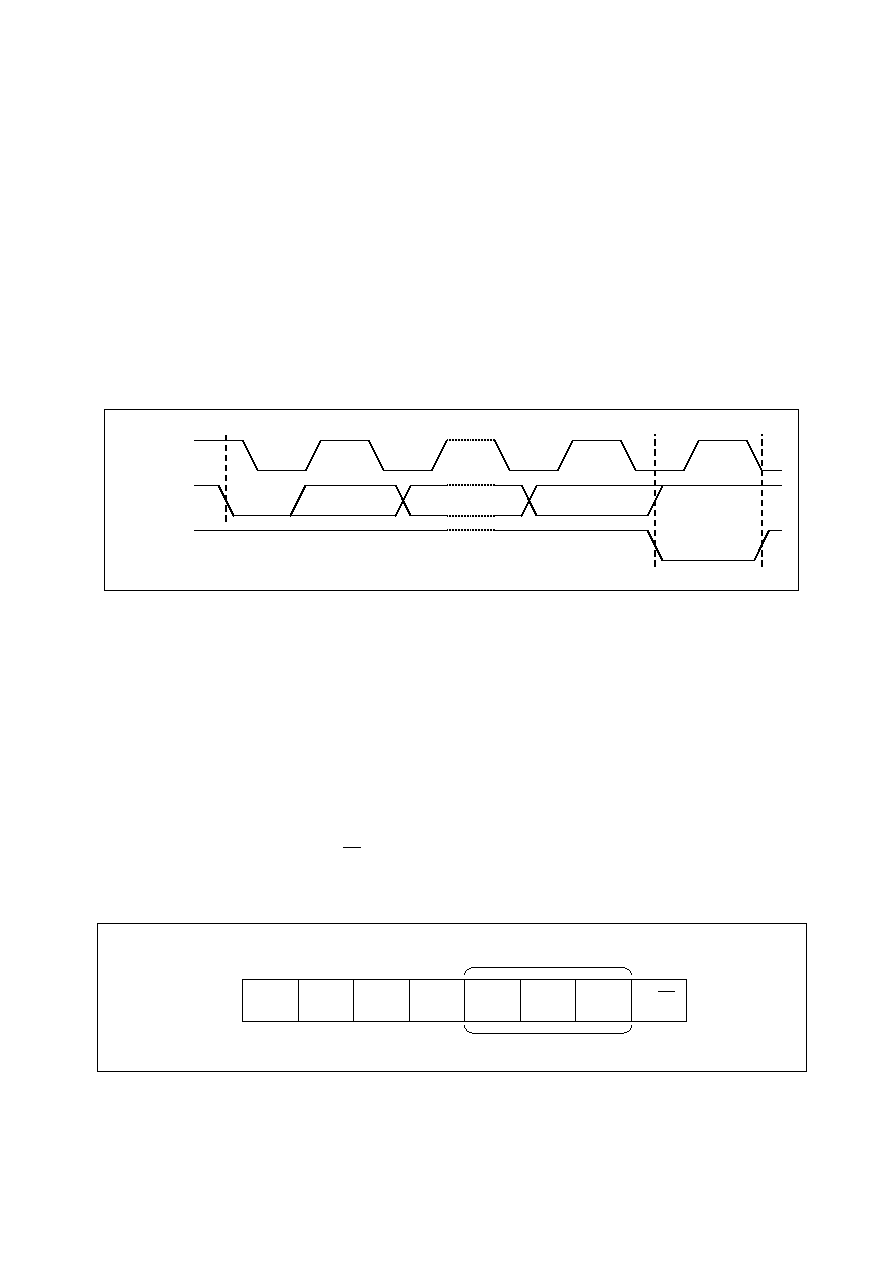

[SLAVE ADDRESS]

After the START condition, a SLAVE ADDRESS is sent. If the transmitted slave address matches

an address of one of the device, the designated slave pulls the SDA line to LOW.

The most significant four bits of the slave address are fixed as "1010". The next three bits are S0,

S1 and S2 device address bits. These three bits identify the specific device on the bus. They is

set by the hard wired input pins (S0 pin, S1 pin and S2 pin). Therefore a total of eight devices can

be connected to the same bus.

The last bit of the slave address (R/W bit) defines whether a write or read condition is requested by

the master. A "1" indicates that the read operation is to be executed. A "0" indicates that the write

operation is to be executed.

Figure 4. Slave Address

1

They is set by the hard-wired input pins (S0 pin, S1 pin and S2 pin).

DEVICE ADDRESS

0 1 0 S2

S1

S0

R/W

DATA

OUTPUT

FROM

TRANSMITTER

ACKNOWLEDGE

DATA

OUTPUT

FROM

RECEIVER

SCL FROM

MASTER

1

8

9

ASAHI KASEI

[AK6010A/12A]

DAI02E-03

2002/11

- 5 -

Pin Descriptions

SCL

(Serial Clock)

The SCL input is used to clock all data into and out of the device.

SDA

(Serial Data)

The SDA is a bidirectional pin used to transfer data into and out of the device.

It is an open drain output and may be wire-ORed with any number of open drain or open

collector outputs.

S0, S1, S2

(Device Address)

The S0, S1 and S2 are device address inputs that are used to set three bits of the slave

address.

A total of eight devices can be connected to the same bus.

WC

(Write Control)

If the WC is High level, WRITE operations onto the upper quarter of the memory (AK6010A:

C00 to FFF(Hex), AK6012A: 1800 to 1FFF(Hex)) will not be executed. If the WC is Low level,

the AK6010A/12A will be enabled to perform WRITE operation.

As the WC is internally pulled down to GND, the AK6010A/12A will be enabled to perform

WRITE operation if the WC is left floating.

WC must not change from the start condition input to the stop condition input.

VCC

(Power Supply)

GND

(Ground)