ASAHI KASEI [AK2048]

MS0073-E-00 2001/01

1

AK2048D

AK2048D

AK2048D

AK2048D

2M

2M

2M

2M CMI

CMI

CMI

CMI Transceiver

Transceiver

Transceiver

Transceiver

FEATURES

- 2.048Mbps CMI Interface

- CLOCK & DATA Recovery function

- Loss of Lock Detection

- Loss of Signal Detection

- Transmitter Pulse Shape

- Single 5.0V

�

5% Operation

- Low Power Consumption: 400mW (TYP)

- Package: 44pin QFP

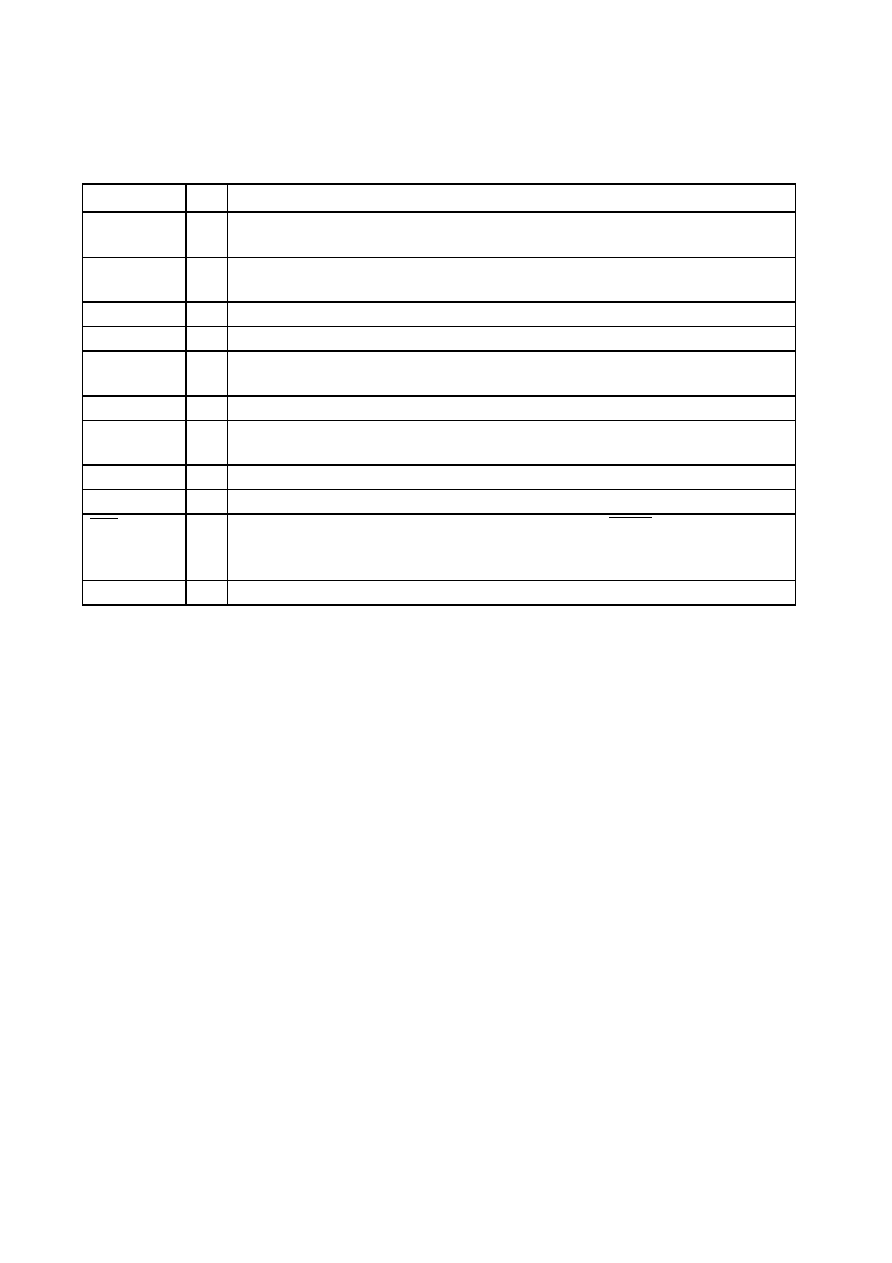

BLOCK DIAGRAM

2M CMI Transceiver Block Diagram

DRIVER

TXA

TXA

TXA

TXA

CMI

ENCODER

TDATA

TDATA

TDATA

TDATA

LOS

CMI

DECODER

LOCK

CLOCK

RECOVER

CALIB

VREF

RESET

TXB

TXB

TXB

TXB

R

R

R

RXA

XA

XA

XA

R

R

R

RX

X

X

XB

B

B

B

TCLK

TCLK

TCLK

TCLK

TCRV

TCRV

TCRV

TCRV

LOS

LOS

LOS

LOS

RDATA

RDATA

RDATA

RDATA

RCRV

RCRV

RCRV

RCRV

RCLK

RCLK

RCLK

RCLK

LOCK

LOCK

LOCK

LOCK

RST

RST

RST

RST

REF25

REF25

REF25

REF25

R

R

R

RVDD

VDD

VDD

VDD

RVSS

RVSS

RVSS

RVSS

TVDD

TVDD

TVDD

TVDD

TVSS

TVSS

TVSS

TVSS

ASAHI KASEI [AK2048]

MS0073-E-00 2001/01

3

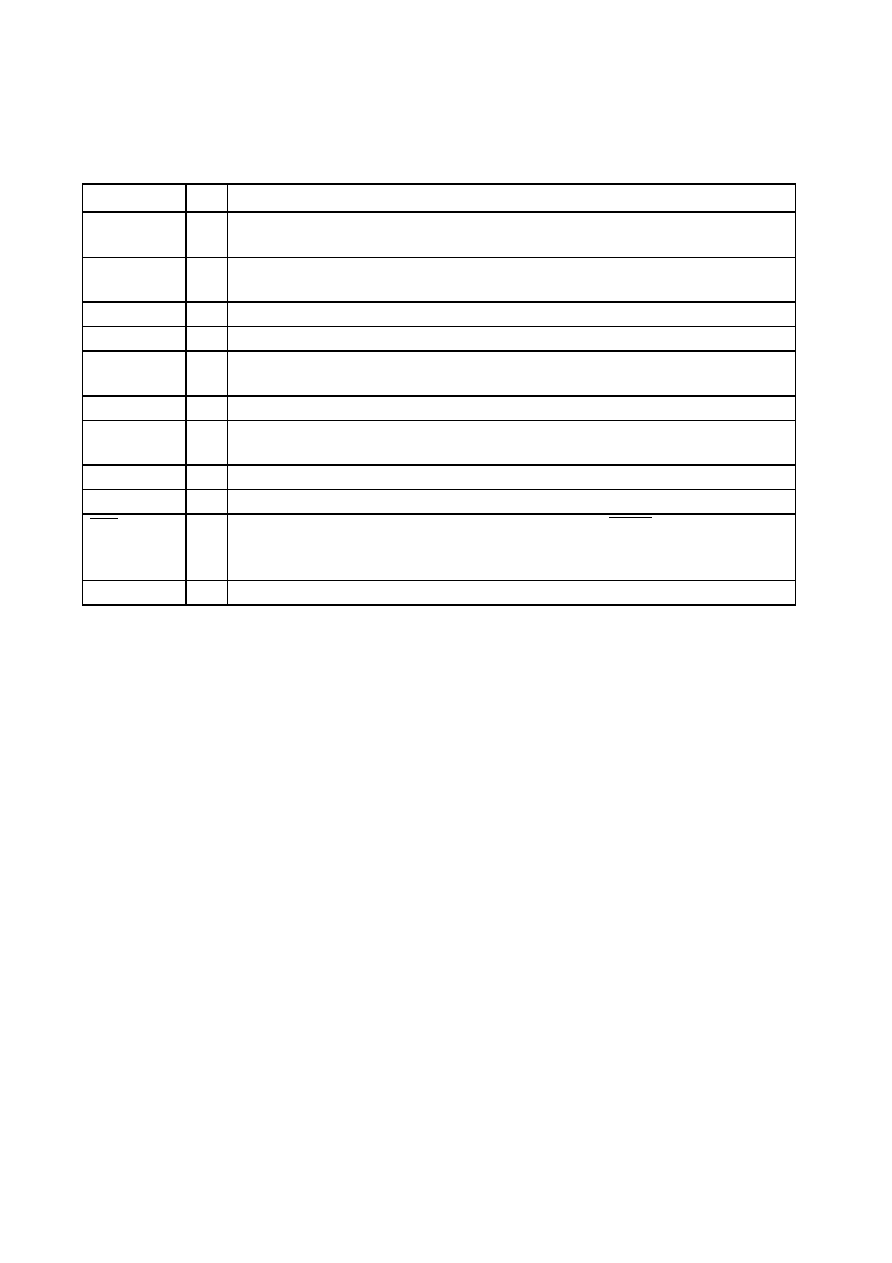

PIN ASSIGNMENTS

Pin No.

Pin Name

I/O

Type

AC Load

(MAX)

DC Load

(MIN)

Comment

1

RDATA O TTL

15pF

4k

2

RCLK O TTL

15pF

4k

3

RCRV O TTL

15pF

4k

9

TDATA I TTL

10

TCLK I TTL

11

TCRV I TTL

13

TEST1 -

*2)

14

TEST2 -

*2)

15

LOCK O TTL

15pF

4k

16

LOS O TTL

15pF

4k

23

TXB O

Analog

15pF

*1)

24

TVSS -

25

TVDD -

26

TXA O

Analog

15pF

*1)

29

RXB I

Analog

31

REF25 O Analog 1

�

F(typ)

33

RXA I

Analog

40

RVDD -

41

RST

I

TTL

Pulled up to VDD

by the internal

register (50K

min)

42

RVSS -

The other pins (4-8,12,17-22,27,28,30,32,34-39,43,44) are NC pins.

NC pins are recommended to connect to VSS to avoid noise problem.

*1) TXA, TXB can drive 110

connected between these pins.

*2) Must be open.

ASAHI KASEI [AK2048]

MS0073-E-00 2001/01

4

PIN DESCRIPTIONS

Pin Name

I/O

Function

RDATA O

Receive Data output recovered from the incoming data. Delay time from the incoming

data to the RDATA is about 1.25bit. Output on the rising edge of RCLK.

RCLK O

Receive Clock Output recovered from the incoming data.

RCRV O

CRV (Code Rule Violation) output pin.

When AK2048D detects the CRV of CMI codes from in the coming data, RCRV goes

to "high" synchronized with the violation data. CRV is detected for both "0" data and

"1" data. Refer to Fig.6, 11

TDATA I

Transmit Data Input pin.

Input on the falling edge of TCLK.

TCLK I

Transmit Clock Input pin.

TCRV I

If this input is "high", AK2048D generates CRV in the transmit data.

CRV is generated for both "0"data and "1"data. "High" input TCRV is accepted until 5

clocks duration. If the duration of "High" input is longer than 6 clocks, TCRV input

after 6th clock is ignored. Refer to Fig.4, 11

TEST1 NC

Test pin. Should be floated.

TEST2 NC

Test pin. Should be floated.

LOCK O

LOCK indicates the PLL status whether PLL is in the LOCK status or PLL is in the

UNLOCK status.

LOCK status

LOCK becomes "Low" when the sampled RCLK are all "Low" during the consecutive

32 RXA-RXB sample clock duration.

UN LOCK status

LOCK becomes "High" when the following both conditions are satisfied.

-

The sampled RCLK are "High" more than 5 clocks in the frame of the consecutive

256 RXA-RXB clock duration.

-

And the above happens in the 5 consecutive frames.

In another condition, LOCK keeps the current output status without change.

The output timing of this signal is asynchronous with RCLK.

When RST is "Low", LOCK is fixed to "High".

ASAHI KASEI [AK2048]

MS0073-E-00 2001/01

5

Pin Name

I/O

Function

LOS O

LOS goes High within 12usec after AK2048D detects that the amplitude of the RXB

input signal is lower than 135mVpp(typ). Output on the rising edge of RCLK.

TXB O

Transmit CMI signal output. TXA is to CMI+, and TXB is corresponds to CMI-.

Delay time from TDATA to TXB is about 1bit.

TVSS -

Negative power supply 0V

TVDD -

Positive power supply 5V

TXA O

Transmit CMI signal output. TXA is to CMI+, and TXB is corresponds to CMI-.

Delay time from TDATA to TXA is about 1bit.

RXB I

Receive CMI signal input. RXA is to CMI+, and RXB is corresponds to CMI-.

REF25 O

Output reference voltage (about 2.5V) in order to decide middle point of input signal

(RXA-RXB). Connected to middle point of the external equalizer.

RXA I

Receive CMI signal input. RXA is to CMI+, and RXB is corresponds to CMI-.

RVDD -

Positive power supply.

5V

RST O

"Low" input reset the calibration circuit and forces LOCK output "High" and

TXA-TXB output "High-Z". When this input rise, PLL calibration restarts.

Please set open or connect to VDD when not using.

RVSS -

Negative power supply 0V